### Automatic Generation of Parallel Programs with Dynamic Load Balancing for a Network of Workstations

Bruce S. Siegell May 5, 1995

CMU-CS-95-168

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Thesis Committee:

H. T. Kung, Chair Allan Fisher Peter Steenkiste Jaspal Subhlok

Copyright ©1995 by Bruce S. Siegell.

Supported in part by the Defense Advanced Research Projects Agency, Information Science and Technology Office, under the title "Research on Parallel Computing," ARPA Order No. 7330. Work furnished in connection with this research is provided under prime contract MDA972-90-C-0035 issued by DARPA/CMO to Carnegie Mellon University and under its subcontract, No. 334918-58792 with Networks Systems Corporation.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of Network Systems Corporation, DARPA or the U. S. Government.

**Keywords:** dynamic load balancing, parallelizing compilers, network of workstations, self-scheduling, grain size, Nectar

### Abstract

Because of their high availability and relatively low cost, networks of workstations are now often considered as platforms for applications that used to be relegated to dedicated multiprocessors. Parallelizing compilers have simplified the programming of shared and distributed memory multiprocessors. However, with networks of workstations, which are more loosely coupled, additional problems of heterogeneity, varying resource availability, and higher communication costs must be addressed in order to maximize utilization of system resources. Computational capabilities may vary with time due to other applications competing for resources, so dynamic load balancing is very important.

Our research explores issues in retargeting a parallelizing compiler for a network of workstations. In this dissertation, we describe a system that supports dynamic load balancing of distributed applications consisting of parallelized DOALL and DOACROSS loops. We outline the added compiler functionality needed to generate parallel programs with dynamic load balancing and demonstrate how parameters for dynamic load balancing can be selected and controlled automatically at run time with cooperation between the compiler and runtime system. We have implemented a prototype runtime system on the Nectar system at Carnegie Mellon University and have evaluated its performance using hand-parallelized applications running in various environments.

Key performance parameters under our control include the grain size of the application, the frequency of load balancing, and the amount and frequency of work movement. The optimal grain size is selected based on computation and communication costs of the application on the particular system on which it is run. Selecting an appropriate load balancing frequency requires information about communication costs and process scheduling by the operating system. The frequency must be adjusted as loads on the processors change, and controlling the frequency requires the cooperation of the compiler. Making correct decisions regarding work movement is a difficult problem because of high work movement costs and the unpredictable nature of the loads on the processors. Our measurements show that dynamic load performance improves system utilization and reduces execution times in some cases, but is ineffective for others, largely due to the costs of moving work.

### Acknowledgements

I would like to thank my advisor, H. T. Kung, for his advice, support, and encouragement. I am grateful to him for allowing me to follow my interests in both hardware and software within the contexts of the Nectar and iWarp projects. I would also like to thank Peter Steenkiste for advising me after Kung left for Harvard. Peter is a good sounding board and encouraged me to write papers to help organize my ideas. He also read my manuscript several times, identifying problem areas and giving useful suggestions about ways to strengthen its presentation. Thanks also to the other members of my thesis committee—Allan Fisher and Jaspal Subhlok—for their invaluable comments and suggestions regarding my dissertation.

Many other people in the ECE<sup>1</sup> and SCS<sup>2</sup> communities have helped me with my research and helped to make my life enjoyable during my time at CMU. I am indebted to the people who listened to and gave constructive feedback on the practice talks for my defense and to the attendees of the iWarp/Nectar seminars who listened attentively to my other talks over the years. I thank the members of the Nectar project who developed and maintained the Nectar hardware and software. Michael Gillinov deserves special thanks for helping me keep the prototype Nectar system running after everyone else went off to do other things. I also thank the SCS Facilities staff for keeping everything else running. My officemates and the SCS Zephyr community<sup>3</sup> have also helped me with many day-to-day questions and problems. Finally, I'd like to thank my friends and family for being supportive during the ups and downs of my graduate studies.

Portions of the work described here have been published previously [54].

<sup>&</sup>lt;sup>1</sup>Department of Electrical and Computer Engineering.

<sup>&</sup>lt;sup>2</sup>School of Computer Science.

<sup>&</sup>lt;sup>3</sup>The people who use the Zephyr Notification Service.

### Contents

| 1 | Intro | oduction                                                         | 1  |

|---|-------|------------------------------------------------------------------|----|

|   | 1.1   | Features of target system                                        | 3  |

|   | 1.2   | Application domain and compiler model                            | 3  |

|   |       | 1.2.1 Notation used in this thesis                               | 5  |

|   |       | 1.2.2 DOALL loops                                                | 6  |

|   |       | 1.2.3 DOACROSS loops                                             | 7  |

|   |       | 1.2.4 Dealing with recurrences                                   | 8  |

|   |       | 1.2.5 Example applications                                       | 8  |

|   | 1.3   | Our load balancing approach                                      | 12 |

|   | 1.4   | Control theory model of dynamic load balancing 1                 | 14 |

|   | 1.5   | Evaluating parallel performance                                  | 17 |

|   | 1.6   | Summary of experimental results                                  | 21 |

|   | 1.7   | Related work                                                     | 21 |

|   |       | 1.7.1 Compiler support for load balancing                        | 22 |

|   |       | 1.7.2 Self-scheduling                                            | 22 |

|   |       | 1.7.3 Diffusion methods                                          | 24 |

|   |       | 1.7.4 Use of prior performance as estimate of future performance | 24 |

|   | 1.8   | Organization of this dissertation                                | 25 |

| 2 | Load  | d balancing architecture 2                                       | 27 |

|   | 2.1   | Application considerations                                       | 27 |

|   |       | 2.1.1 Position of distributed loop in loop structure             | 28 |

|   |       | 2.1.2 Loop carried dependences                                   | 28 |

|   |       | 2.1.3 Dependences outside loop                                   | 29 |

|   |       | 2.1.4 Loop bounds                                                | 30 |

|   |       | 2.1.5 Iteration sizes                                            | 31 |

|   |       | 2.1.6 Data size                                                  | 32 |

|   | 2.2   | Environmental considerations                                     | 32 |

|   |       | 2.2.1 Hardware configuration                                     | 32 |

|   |       | 2.2.2 Communication costs                                        | 33 |

|   |       | 2.2.3 Dynamicness of system                                      | 33 |

|   | 2.3   | Load balancing design space                                      | 34 |

|   | 2.4  | Load balancing architecture                              |

|---|------|----------------------------------------------------------|

|   |      | 2.4.1 Global information                                 |

|   |      | 2.4.2 Work distributed among slave processors            |

|   |      | 2.4.3 Use of application knowledge                       |

|   | 2.5  | Load balancing strategy                                  |

|   | 2.6  | Master-slave interactions                                |

|   |      | 2.6.1 Pipelined Load Balancing                           |

|   |      | 2.6.2 Asynchronous load balancing                        |

|   |      | 2.6.3 Granularity of work movement                       |

|   | 2.7  | Summary                                                  |

| 3 | Auto | omatic selection of grain size 47                        |

|   | 3.1  | Synchronization types                                    |

|   | 3.2  | Compile-time control of grain size                       |

|   |      | 3.2.1 Loop splitting                                     |

|   |      | 3.2.2 Message aggregation                                |

|   |      | 3.2.3 Strip mining                                       |

|   |      | 3.2.4 Loop tiling                                        |

|   | 3.3  | Unidirectional synchronizations                          |

|   |      | 3.3.1 Controlling grain size at run time                 |

|   |      | 3.3.2 Communication costs                                |

|   |      | 3.3.3 Pipeline fill and drain times                      |

|   |      | 3.3.4 Selecting the optimal block size                   |

|   |      | 3.3.5 Evaluation of grain size model                     |

|   |      | 3.3.6 Optimal grain size vs. fixed grain size            |

|   |      | 3.3.7 Effect of competing loads                          |

|   | 3.4  | Bidirectional (barrier) synchronizations                 |

|   |      | 3.4.1 Synchronization overhead                           |

|   |      | 3.4.2 Effect of competing loads                          |

|   | 3.5  | Summary                                                  |

| 4 | Auto | omatic selection of load balancing frequency 75          |

|   | 4.1  | Cooperation between compiler and runtime system          |

|   | 4.2  | Compiler placement of load balancing code                |

|   |      | 4.2.1 Possible hook locations                            |

|   |      | 4.2.2 Selecting from among possible hook locations       |

|   |      | 4.2.3 Code restructuring to create better hook locations |

|   |      | 4.2.4 Hook placement algorithm                           |

|   |      | 4.2.5 Timing code                                        |

|   | 4.3  | Selection of load balancing frequency at run time        |

|   |      | 4.3.1 Interaction overhead                               |

|   |      | 4.3.2 Cost of work movement                              |

|   |      | 4.3.3 Interaction with time quantum                      |

|   |                                                                                                                                  | 4.3.4 Target load balancing period                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|---|----------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   |                                                                                                                                  | 4.3.5 Effect of load balancing frequency on performance                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                                                                                                  | 4.3.6 Effectiveness of frequency selection in limiting overhead                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|   | 4.4                                                                                                                              | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5 | Loa                                                                                                                              | balancing process 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|   | 5.1                                                                                                                              | High-level design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|   | 5.2                                                                                                                              | Computing the optimal distribution                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.3                                                                                                                              | Imbalance detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|   |                                                                                                                                  | 5.3.1 Quantifying load imbalance                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                                                                                                                  | 5.3.2 Effect of imbalance threshold on performance                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|   | 5.4                                                                                                                              | Filtering rate information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   |                                                                                                                                  | 5.4.1 Effect of filtering on performance                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|   | 5.5                                                                                                                              | Instruction generation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|   |                                                                                                                                  | 5.5.1 Unrestricted work movement                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|   |                                                                                                                                  | 5.5.2 Restricted work movement                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|   | 5.6                                                                                                                              | Profitability determination                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|   |                                                                                                                                  | 5.6.1 Estimating costs of work movement                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                                                                                                  | 5.6.2 Estimating benefits of work movement                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

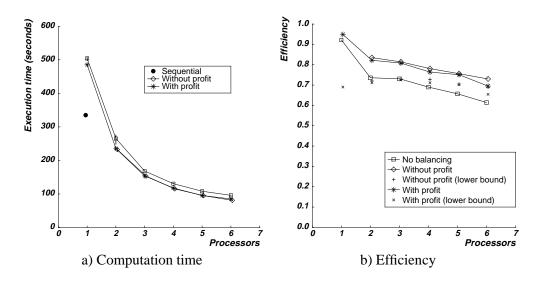

|   |                                                                                                                                  | 5.6.3 Effect of Profitability Determination on Performance                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|   | 5.7                                                                                                                              | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|   |                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6 | Con                                                                                                                              | piler support for load balancing 127                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6 | <b>Con</b><br>6.1                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 6 |                                                                                                                                  | Code structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6 | 6.1                                                                                                                              | Code structure       128         Changes to distributed loop bounds and distributed data structures       129                                                                                                                                                                                                                                                                                                                                                                                                |

| 6 | 6.1                                                                                                                              | Code structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6 | 6.1                                                                                                                              | Code structure       128         Changes to distributed loop bounds and distributed data structures       129         6.2.1       Basic data structure       131         6.2.2       Efficient access to data       131                                                                                                                                                                                                                                                                                      |

| 6 | 6.1                                                                                                                              | Code structure       128         Changes to distributed loop bounds and distributed data structures       129         6.2.1       Basic data structure       131         6.2.2       Efficient access to data       131         6.2.3       Selecting the data structure       137                                                                                                                                                                                                                           |

| 6 | 6.1<br>6.2                                                                                                                       | Code structure       128         Changes to distributed loop bounds and distributed data structures       129         6.2.1       Basic data structure       131         6.2.2       Efficient access to data       131                                                                                                                                                                                                                                                                                      |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                    | Code structure       128         Changes to distributed loop bounds and distributed data structures       129         6.2.1       Basic data structure       131         6.2.2       Efficient access to data       131         6.2.3       Selecting the data structure       137         Dealing with varying loop bounds       137                                                                                                                                                                        |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                    | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved141                                                                                                                                                                                                                       |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li></ul>                                                                                    | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1426.4.2Moving distributed data between processors.142                                                                                                                                                                    |

| 6 | <ul><li>6.1</li><li>6.2</li><li>6.3</li><li>6.4</li></ul>                                                                        | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1416.4.2Moving distributed data between processors.142Work update routines143                                                                                                                                             |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> </ul>                                                      | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1426.4.2Moving distributed data between processors.142                                                                                                                                                                    |

| 6 | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul>                            | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1426.4.2Moving distributed data between processors.142Work update routines142Modifications to communication code144Summary146                                                                                             |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>Eval</li> </ul>              | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1416.4.2Moving distributed data between processors.142Work update routines144Modifications to communication code144Summary146Mation147                                                                                    |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> </ul>                            | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1416.4.2Moving distributed data between processors142Work update routines143Modifications to communication code144Summary146Itation147Experimental setup147                                                               |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>Eval</li> </ul>              | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1416.4.2Moving distributed data between processors142Work update routines144Modifications to communication code144Summary146Tation147Fxperimental setup1477.1.1Target environment148                                      |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>Eval</li> </ul>              | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1446.4.2Moving distributed data between processors144Modifications to communication code144Summary146nation147Fxperimental setup1477.1.1Target environment1487.1.2Application versions149                                 |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>Eval</li> </ul>              | Code structure126Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1446.4.2Moving distributed data between processors142Work update routines144Modifications to communication code144Summary1467.1.1Target environment1477.1.2Application versions1457.1.3Performance with load balancing150 |

|   | <ul> <li>6.1</li> <li>6.2</li> <li>6.3</li> <li>6.4</li> <li>6.5</li> <li>6.6</li> <li>6.7</li> <li>Eval</li> <li>7.1</li> </ul> | Code structure128Changes to distributed loop bounds and distributed data structures1296.2.1Basic data structure1316.2.2Efficient access to data1316.2.3Selecting the data structure137Dealing with varying loop bounds137Work movement routines1406.4.1Identifying data to be moved1446.4.2Moving distributed data between processors144Modifications to communication code144Summary146nation147Fxperimental setup1477.1.1Target environment1487.1.2Application versions149                                 |

|   | 7.4 | Load balancing in a dynamic system             |

|---|-----|------------------------------------------------|

|   | 7.5 | Modeling performance with oscillating loads    |

|   |     | 7.5.1 Static load balancing                    |

|   |     | 7.5.2 Dynamic load balancing                   |

|   |     | 7.5.3 Improving the model/Improving the system |

|   | 7.6 | Limits of dynamic load balancing approach      |

|   | 7.7 | Summary                                        |

| 8 | Con | clusions 185                                   |

|   | 8.1 | Contributions                                  |

|   | 8.2 | Areas for future work                          |

### **List of Figures**

| 1.1  | Distribution of output matrix by columns.                                                     | 4  |

|------|-----------------------------------------------------------------------------------------------|----|

| 1.2  | Matrix and vector notation for figures and equations.                                         | 5  |

| 1.3  | Representations for program examples.                                                         | 6  |

| 1.4  | Distribution of DOALL loop.                                                                   | 7  |

| 1.5  | Distribution of DOACROSS loop.                                                                | 8  |

| 1.6  | Replacement of recurrence with reduction operation.                                           | 9  |

| 1.7  | Sequential code for matrix multiplication (MM).                                               | 10 |

| 1.8  | Sequential code for successive overrelaxation (SOR).                                          | 11 |

| 1.9  | Dependences and execution order for single SOR phase                                          | 11 |

| 1.10 | Sequential code for LU decomposition (LU).                                                    | 13 |

| 1.11 | Redistribution of output matrix to balance load                                               | 14 |

| 1.12 | Simplified model of load balancer as a digital feedback control system.                       | 15 |

| 1.13 | Dynamic load balancing control system.                                                        | 16 |

| 0.1  |                                                                                               | 20 |

| 2.1  | Communication requirements for different mappings of loop iterations.                         | 29 |

| 2.2  | Communication for load balancing.                                                             | 38 |

| 2.3  | Interactions for load balancing in a stable balanced system.                                  | 40 |

| 2.4  | Interactions for load balancing in a system where available computation resources vary.       | 43 |

| 2.5  | Pipelined vs. asynchronous load balancing for $500 \times 500$ MM                             | 45 |

| 3.1  | Communication pattern determines synchronization type.                                        | 48 |

| 3.2  | LU decomposition row elimination loop.                                                        | 50 |

| 3.3  | Strip mining transformation.                                                                  | 51 |

| 3.4  | Parallelization options for SOR.                                                              | 52 |

| 3.5  | Modeling execution time for pipelined application.                                            | 57 |

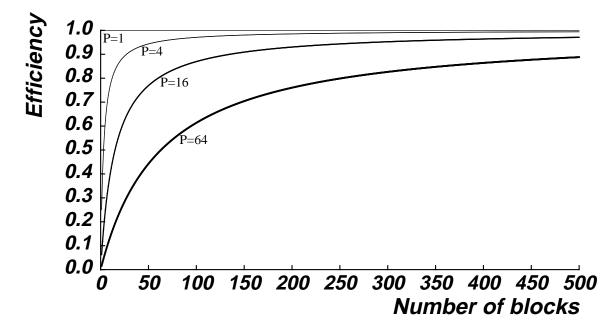

| 3.6  | Upper bound on efficiency for pipelined loop                                                  | 58 |

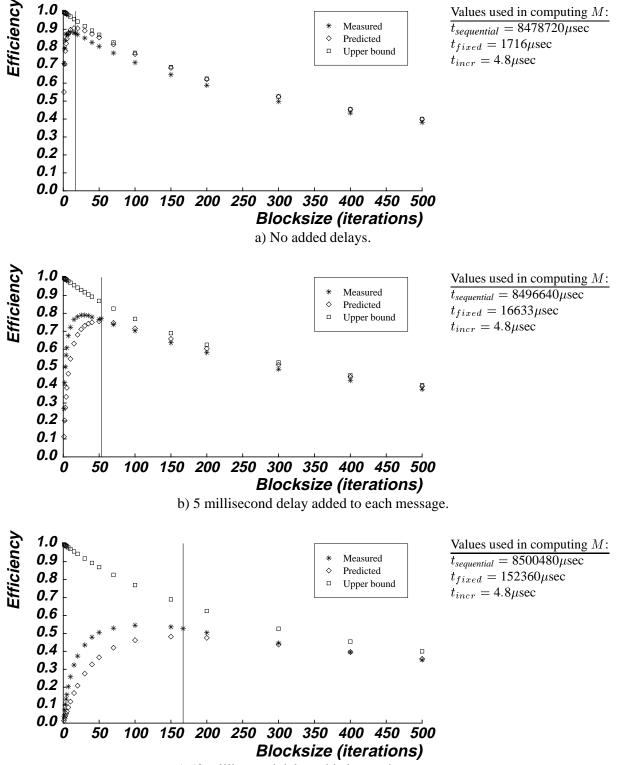

| 3.7  | Efficiency of pipelined loop in SOR as a function of block size.                              | 60 |

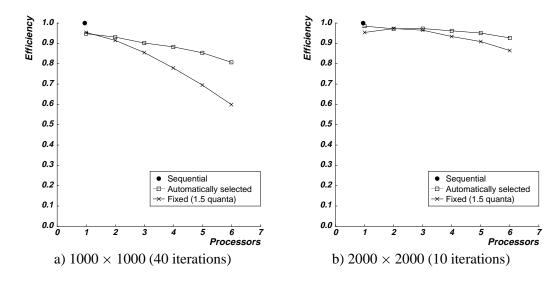

| 3.8  | Fixed grain size vs. automatically selected grain size for pipelined application.             | 62 |

| 3.9  | Model of pipelined execution with competing load.                                             | 63 |

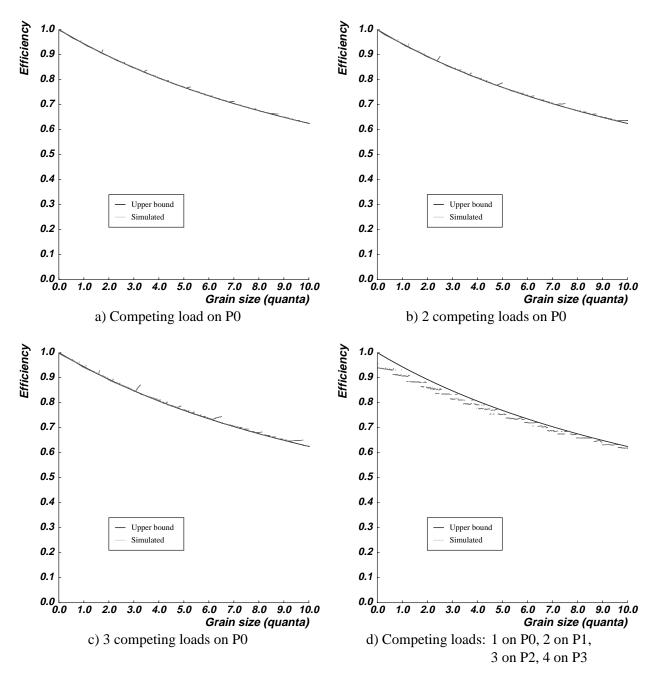

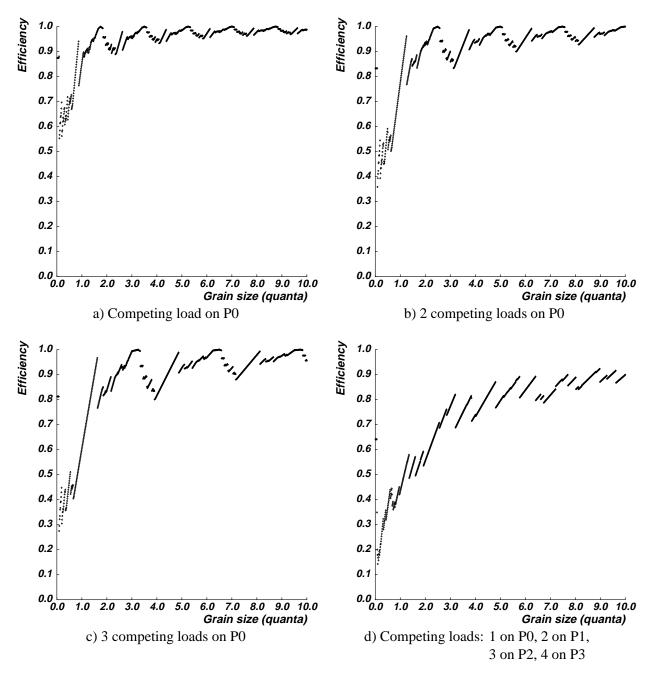

| 3.10 | Simulation results for pipelined execution with competing loads.                              | 65 |

| 3.11 | Parallelized code with barrier synchronizations.                                              | 66 |

| 3.12 | Interaction between barrier synchronizations ( $grainsize = 70$ msec) and competing load      | 69 |

| 3.13 | Interaction between barrier synchronizations ( $grainsize = 140$ msec) and competing load.    | 70 |

| 3.14 | Simulation results for parallel execution with barrier synchronizations with competing loads. | 71 |

| 4.1        | Code for load balancing hook.                                                                                                    | 77   |

|------------|----------------------------------------------------------------------------------------------------------------------------------|------|

| 4.2        | Time line showing computation and load balancing periods.                                                                        | 77   |

| 4.3        | Pseudocode for SOR showing possible locations for load balancing hook.                                                           | 79   |

| 4.4        | Pseudocode for MM showing possible locations for load balancing hook.                                                            | 82   |

| 4.5        | Using strip mining and loop interchange to increase control of load balancing hook frequency.                                    | 83   |

| 4.6        | Placement of timing code.                                                                                                        | 87   |

| 4.7        | Periods affecting selection of load balancing period                                                                             | 89   |

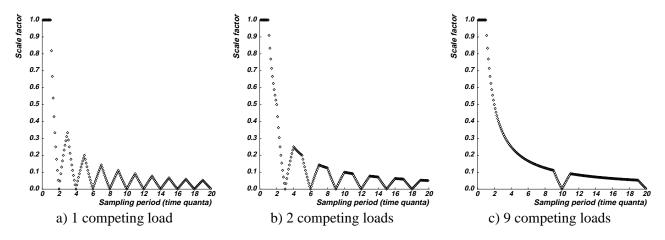

| 4.8        | Sampling of oscillating performance information.                                                                                 | 92   |

| 4.9        | Scale factor for amplitude of oscillations for different sampling periods.                                                       | 93   |

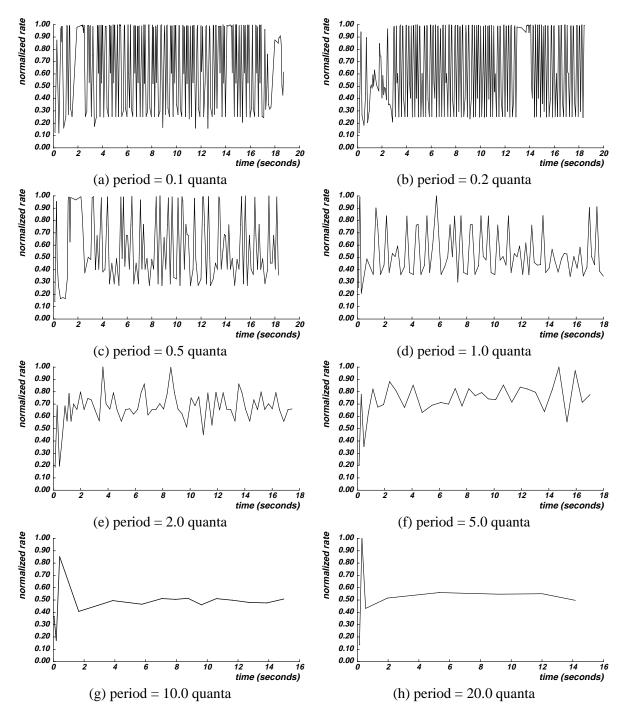

| 4.10       | Effect of sampling period on stability of measurements.                                                                          | 94   |

| 4.11       | Lower bounds on load balancing period.                                                                                           | 95   |

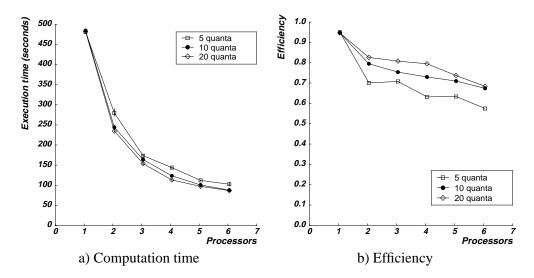

| 4.12       | Effect of load balancing period on efficiency.                                                                                   | 97   |

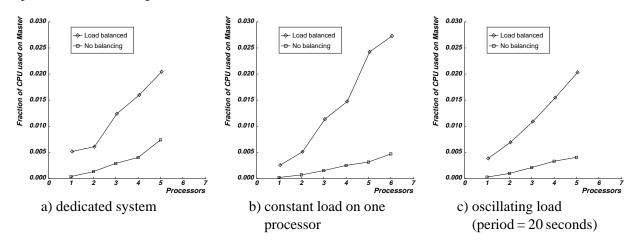

| 4.13       | Fraction of CPU used on master processor for $500 \times 500$ MM                                                                 | 98   |

| 5 1        | The load holonoing desision and soo                                                                                              | 102  |

| 5.1        | The load balancing decision process.                                                                                             | 102  |

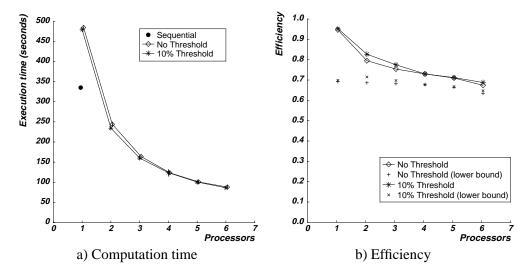

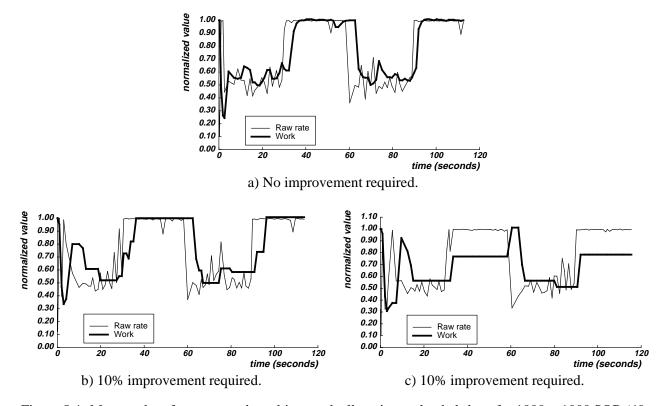

| 5.2        | Effect of threshold on work allocation in response to changes in measured rate on processor with constant competing load.        | 105  |

| 5 2        |                                                                                                                                  |      |

| 5.3        | Effect of using threshold on work allocation in response to changes in rate on processor with                                    | 100  |

| 5.4        | Effect of threshold on work allocation in response to changes in rate on processor with $accillating load (period = 60 seconds)$ | 107  |

| 5.5        | oscillating load (period = 60 seconds).                                                                                          |      |

|            | Performance assessment for a constant competing load.                                                                            |      |

| 5.6<br>5.7 | Performance assessment for an oscillating competing load                                                                         |      |

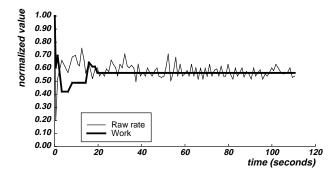

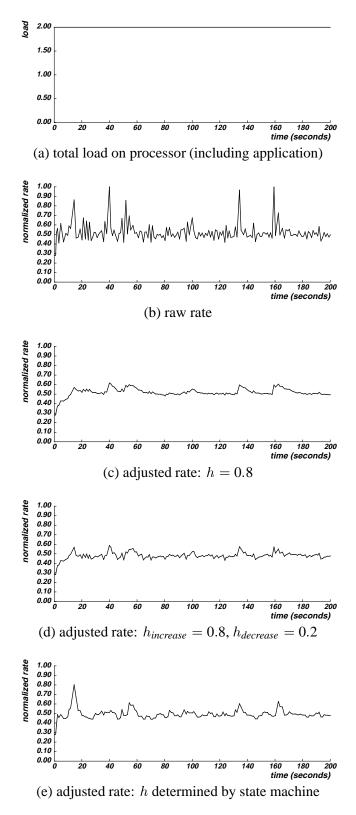

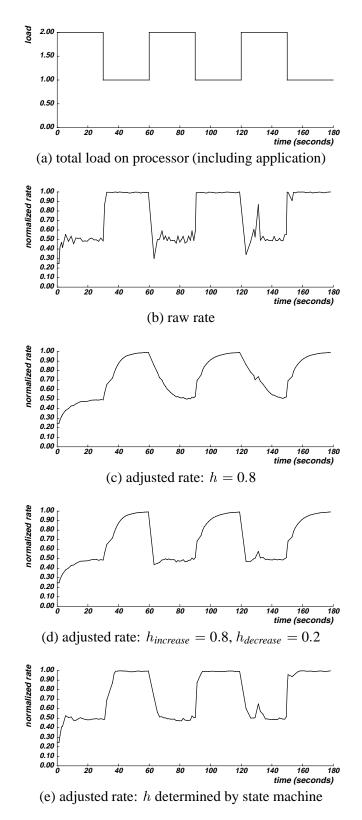

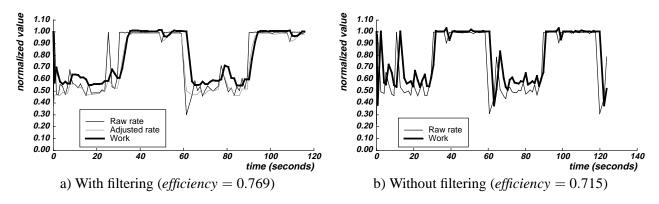

| 5.7        | Effect of filtering on work allocation in response to changes in rate on processor with                                          | 115  |

| 5.0        | oscillating load (period = 60 seconds).                                                                                          | 113  |

| 5.9        | Unrestricted work movement using Algorithm 5.1.                                                                                  |      |

| 5.10       |                                                                                                                                  |      |

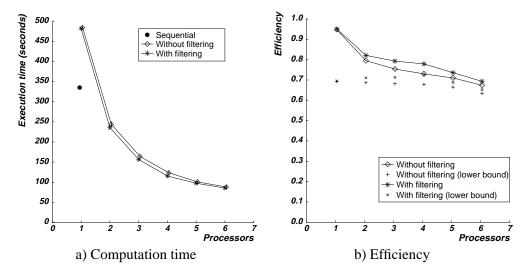

|            | Effect of filtering of rate information on efficiency.                                                                           |      |

| 5.11       |                                                                                                                                  | 121  |

| 6.1        | Code structure for master and slave processes for SOR                                                                            | 129  |

| 6.2        | Common regular distributions.                                                                                                    | 130  |

| 6.3        | Sequential version of code used in comparing representations of irregular distributions                                          | 130  |

| 6.4        | Basic (scattered) data structure for storing distributed data.                                                                   | 132  |

| 6.5        | Scattered data structure with index array.                                                                                       | 134  |

| 6.6        | Packed data structure.                                                                                                           | 135  |

| 6.7        | Packed data structure with reverse index array.                                                                                  |      |

| 6.8        | Data structure for applications with restricted work movement.                                                                   | 138  |

| 6.9        | Code for deactivating data slices when distributed loop bound decreases.                                                         |      |

| 6.10       | Steps in load balancing of SOR example.                                                                                          | 145  |

| 7.1        | The Nectar system.                                                                                                               | 148  |

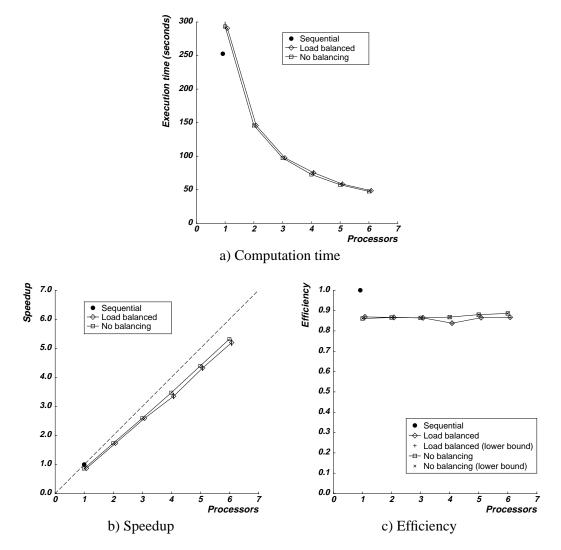

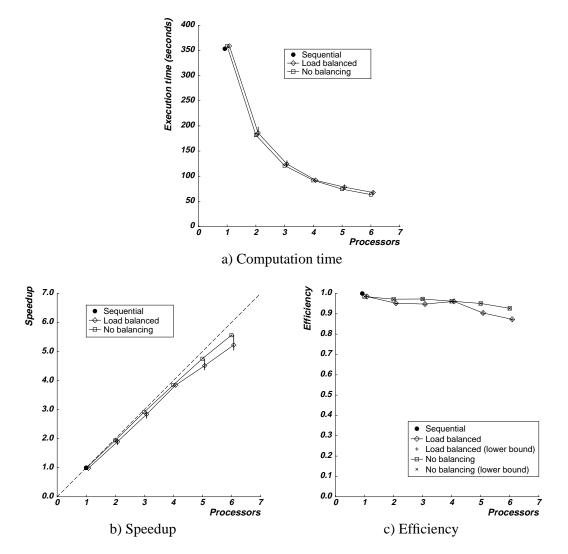

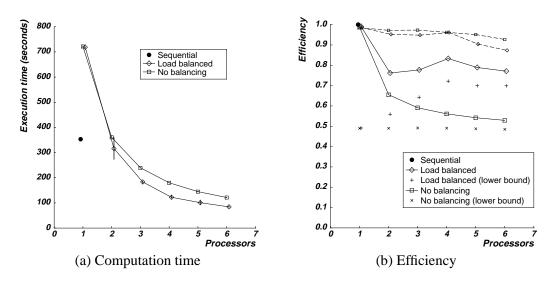

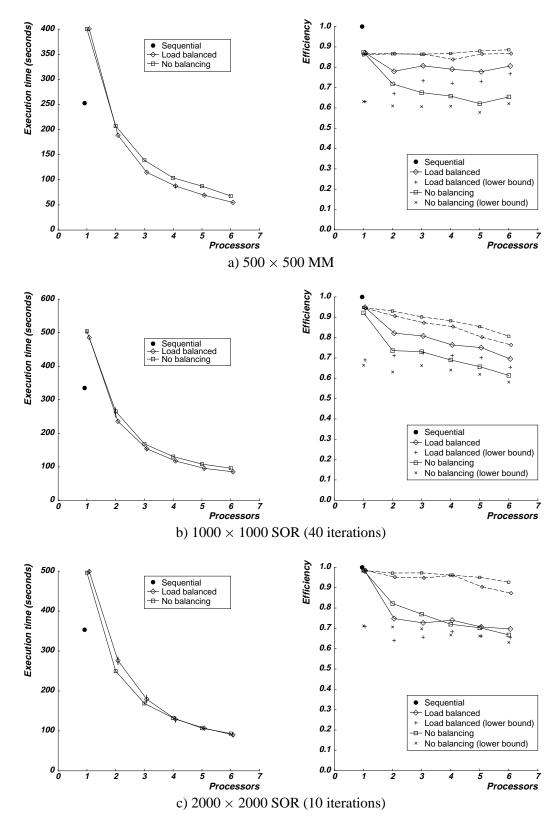

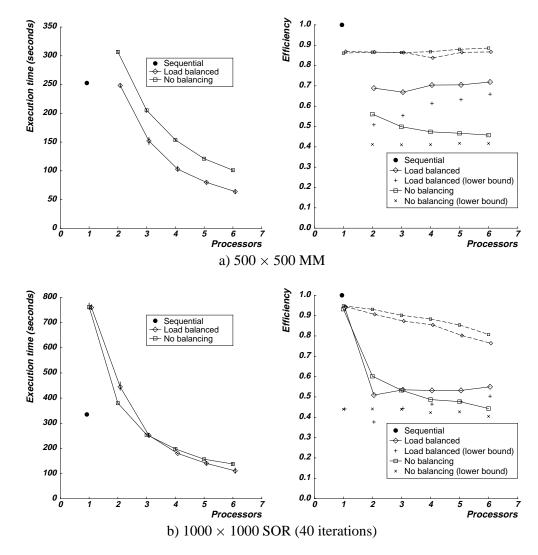

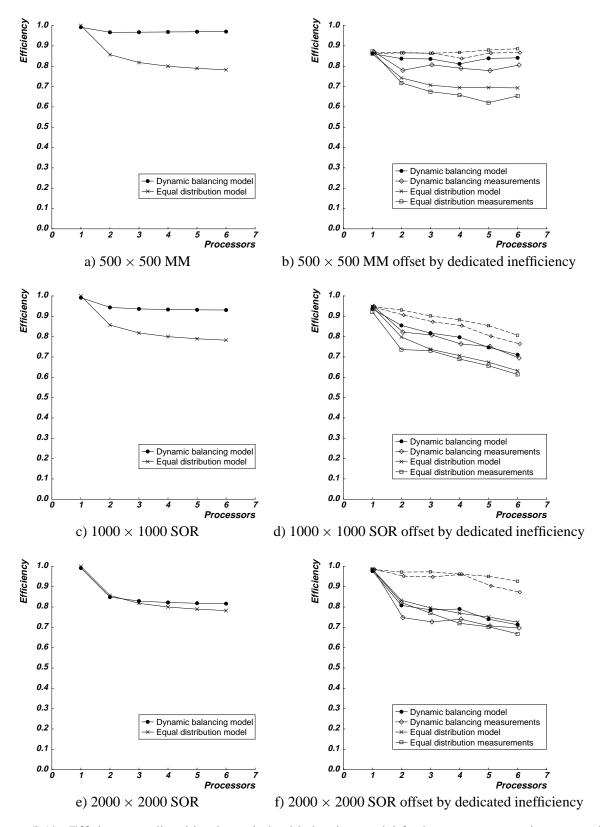

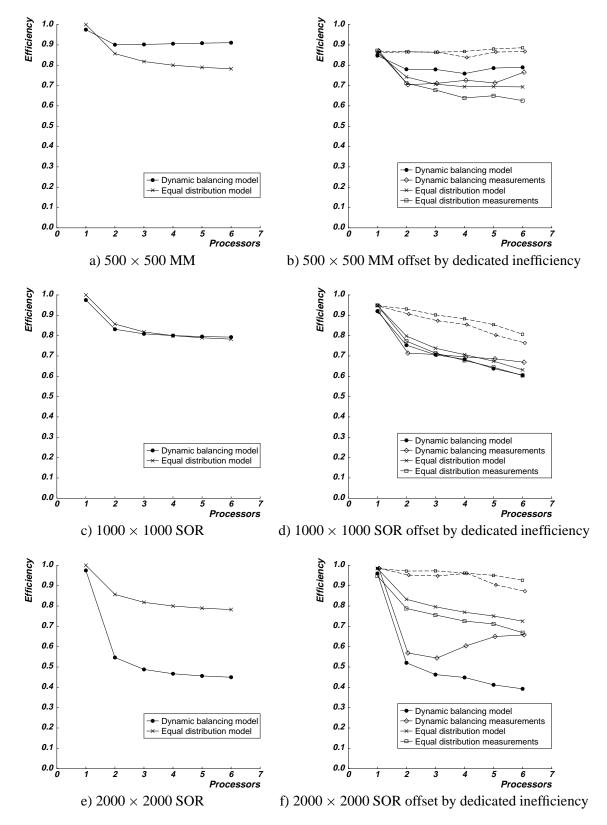

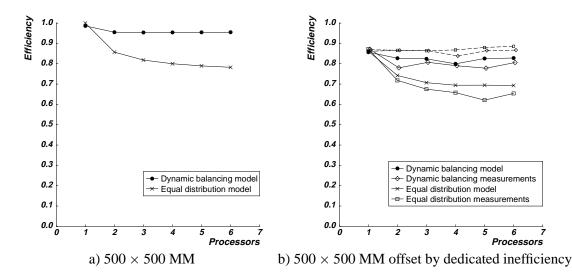

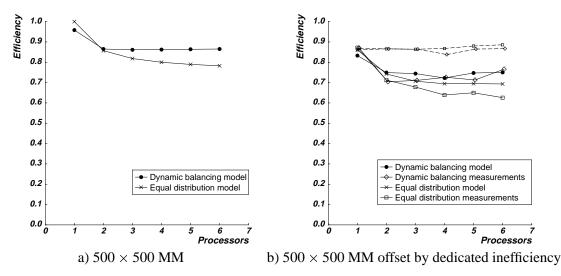

| 7.2        | $500 \times 500$ MM running in dedicated homogeneous environment.                                                                |      |

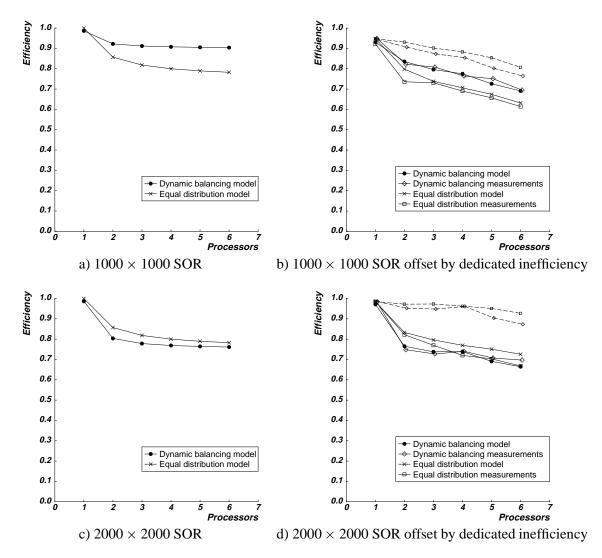

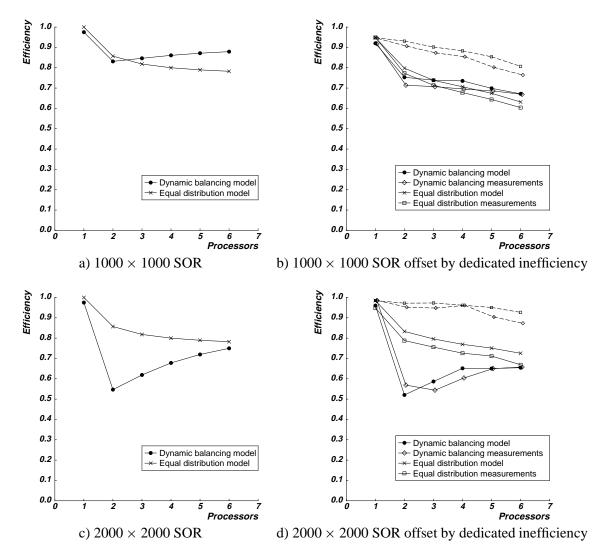

| 7.2        | $1000 \times 1000$ SOR running in dedicated homogeneous environment.                                                             |      |

| 1.5        | 1000 A 1000 DOR funning in dedicated nonlogeneous environment.                                                                   | 1.74 |

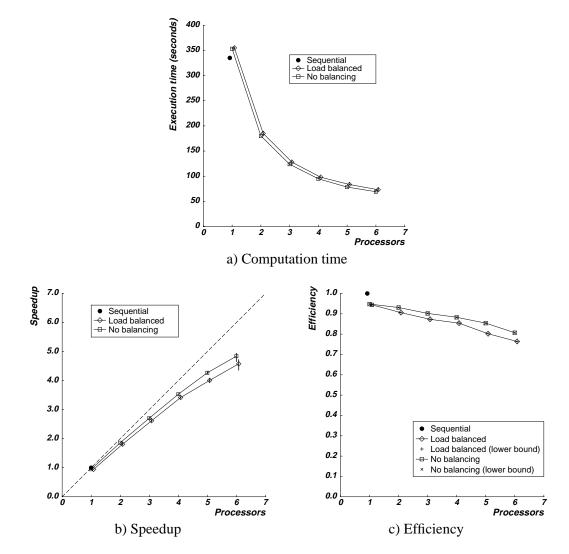

| 7.4  | $2000 \times 2000$ SOR running in dedicated homogeneous environment                                            |

|------|----------------------------------------------------------------------------------------------------------------|

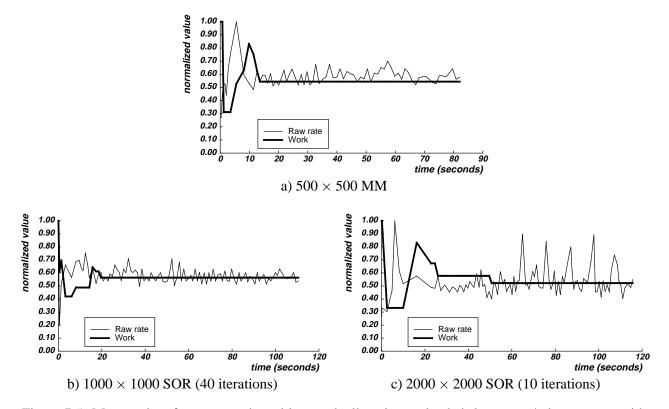

| 7.5  | Measured performance and work movement on processor with constant competing load $157$                         |

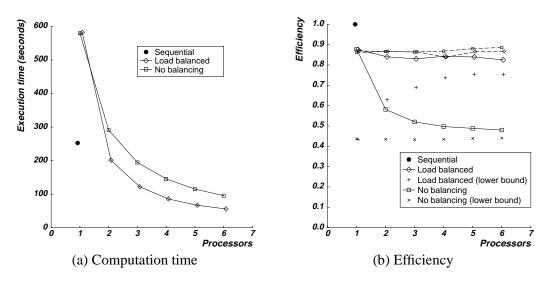

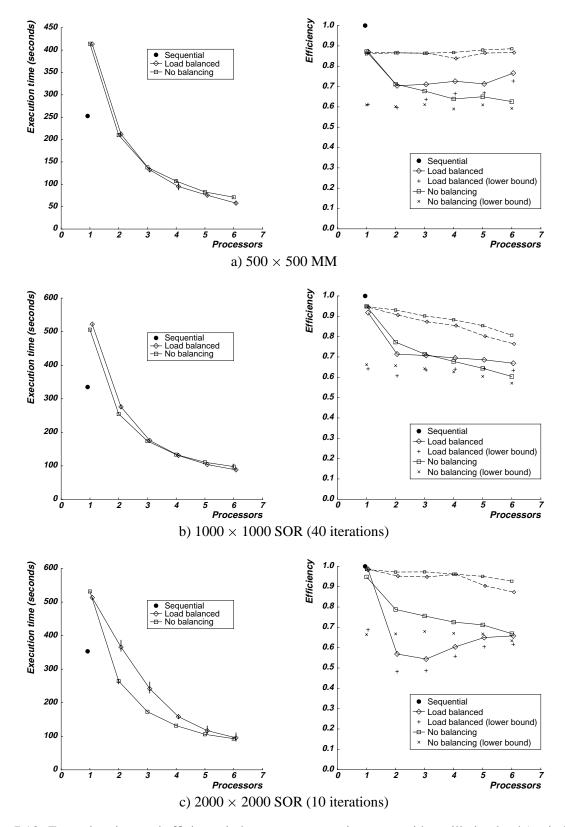

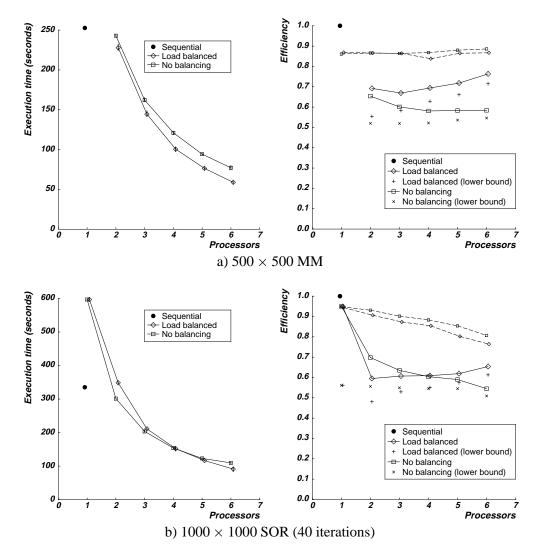

| 7.6  | $500\times500$ MM running in environment with constant load on first processor                                 |

| 7.7  | $1000 \times 1000$ SOR running in environment with constant load on first processor 158                        |

| 7.8  | $2000 \times 2000$ SOR running in environment with constant load on first processor 158                        |

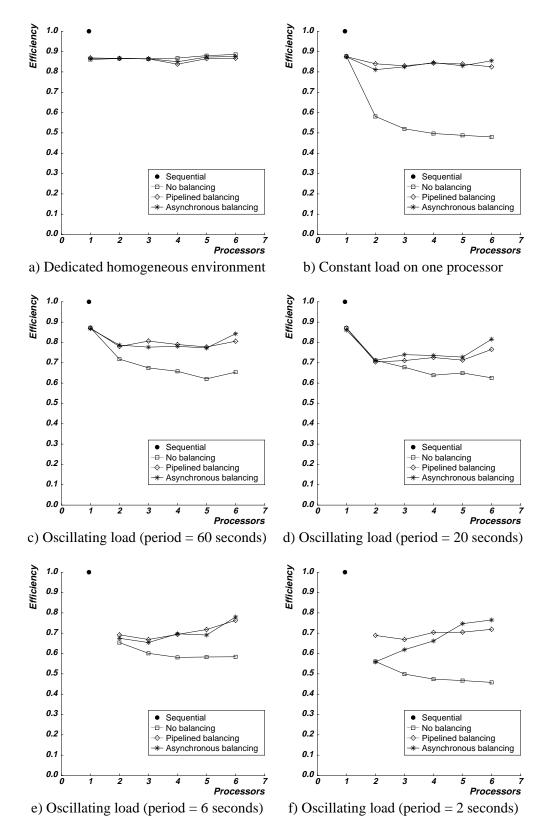

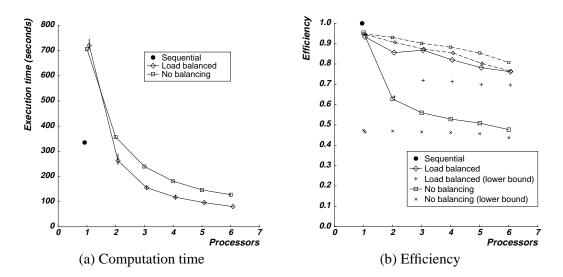

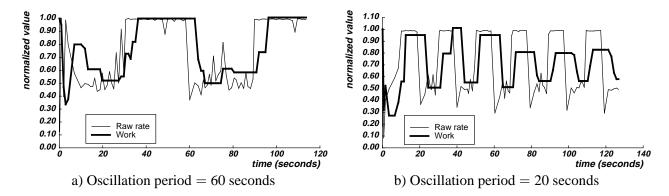

| 7.9  | Performance in environment with oscillating load (period = $60 \text{ sec.}$ ) on one processor 161            |

|      | Performance in environment with oscillating load (period = $20$ sec.) on one processor 162                     |

| 7.11 | Performance in environment with oscillating load (period = $6 \text{ sec.}$ ) on one processor 163             |

|      | Performance in environment with oscillating load (period = $2 \text{ sec.}$ ) on one processor 164             |

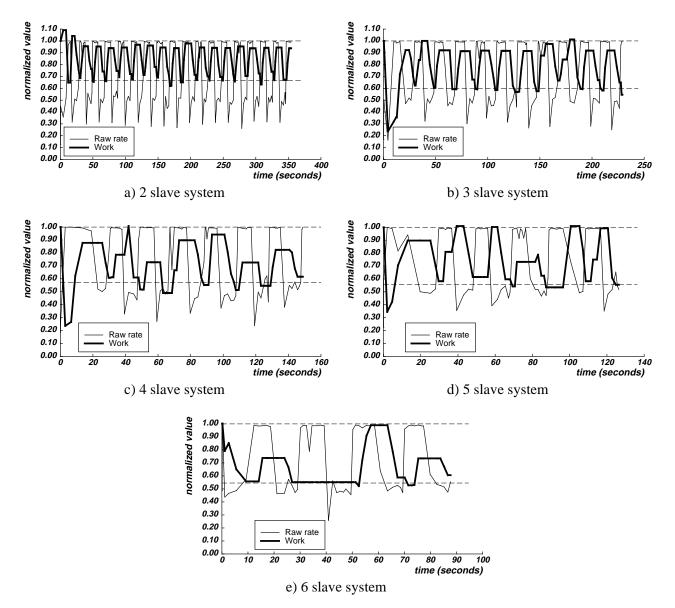

| 7.13 | Measured performance and work movement on processor with oscillating load                                      |

|      | Static allocation of work                                                                                      |

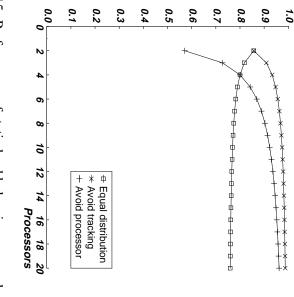

|      | Performance of static load balancing approaches                                                                |

|      | Dynamic load balancing model for predicting performance                                                        |

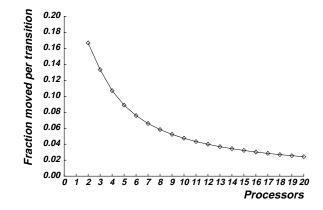

|      | Fraction of total distributed matrix moved with each transition of oscillating load 171                        |

|      | Work movement patterns for restricted work movement                                                            |

|      | Predicted efficiency in environment with oscillating load (period = $60 \text{ sec}$ ) on first processor. 175 |

|      | Predicted efficiency in environment with oscillating load (period = $20 \text{ sec}$ ) on first processor. 176 |

| 7.21 | Predicted efficiency in environment with oscillating load (period = 60 sec), assuming unre-                    |

|      | stricted work movement and higher response time estimates                                                      |

| 7.22 | Predicted efficiency in environment with oscillating load (period = 20 sec), assuming unre-                    |

|      | stricted work movement and higher response time estimates                                                      |

| 7.23 | Predicted efficiency in environment with oscillating load (period = 60 sec), assuming re-                      |

|      | stricted work movement and higher response time and work movement cost estimates 178                           |

| 7.24 | Predicted efficiency in environment with oscillating load (period = 20 sec) on first processor,                |

|      | assuming unrestricted work movement                                                                            |

|      | Decrease in work movement as number of processors increases                                                    |

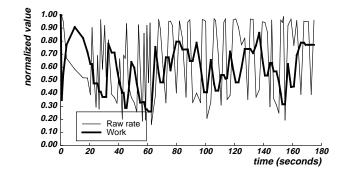

| 7.26 | Measured performance and work allocation on processor with rapidly oscillating load 183                        |

|      |                                                                                                                |

### **List of Tables**

| 2.1 | Application properties                                                                        |

|-----|-----------------------------------------------------------------------------------------------|

| 5.1 | State table for computing <i>h</i>                                                            |

| 5.2 | All possible ordered sets of instructions sent to each slave for restricted work movement 118 |

| 5.3 | Derivation of average number of hops in linear array of processors                            |

| 6.1 | Restructuring transformations                                                                 |

| 6.2 | Summary of data access costs for different data structures                                    |

| 7.1 | Elapsed time measurements for sequential versions of applications                             |

| 7.2 | Application and load balancing parameters selectable at startup time                          |

| 7.3 | Parameters used for load balanced versions of applications                                    |

| 7.4 | Modeling performance with static allocation of work.                                          |

| 7.5 | Work movement costs used in modeling performance                                              |

### Chapter 1

### Introduction

There has been a lot of success in developing parallel languages [48, 51, 52, 66] and parallelizing compilers [25, 62, 67, 79] for MIMD distributed memory machines. These tools have simplified the distribution of applications on tightly-coupled machines, such as the Thinking Machines CM-5 [66], the Intel iWarp [7, 62], and the Cray T3D [1, 44]. Workstation clusters, in which independent workstations are connected by a high-speed network, are emerging as a new type of loosely-coupled multicomputer. However, the tools for managing the distributed resources on these *network-based multicomputers* are in a primitive state. Many message passing libraries exist for networks of workstations, such as PVM [63], Nectarine [57], and Express [18], but it is not straightforward to port tools such as parallelizing compilers to workstation clusters because of the much higher communication costs and the heterogeneity and variability of the available resources. On workstation clusters, both computation and communication capabilities may vary with time due to other applications competing for resources. High speed networks, such as FDDI [49], Nectar [3], Gigabit Nectar [59], or the more recent ATM networks (e.g., [13]), only partially address the high communication costs because throughput is limited by software overhead for protocol processing [58] and message assembly and disassembly on the sending and receiving hosts. Thus, dynamic load balancing and careful management of communication are essential for efficient parallel execution on workstation clusters. Our research explores these issues in retargeting parallelizing compilers for workstation clusters.

On networks of workstations, load balancing tools have been developed on an ad-hoc basis for specific applications and require tuning by the programmer to perform well on specific systems [21, 39, 55]. More general load balancing packages must be developed so that a wider range of applications can be run efficiently

on a range of systems. Switching between applications and systems should require minimal interaction with the programmer. Ideally, the programmer would only need to specify a small set of parameters for the system so that applications can use available resources efficiently. In this thesis, we show that it is possible for a parallelizing compiler to generate efficient code that can dynamically shift portions of an application's workload between processors to improve performance. By using a parallelizing compiler as our starting point, we can handle many load balancing decisions automatically for a large range of applications. A parallelizing compiler can also restructure programs to increase grain size and, thus, reduce communication overheads. Dynamic load balancing does not always improve application performance. The performance with dynamic load balancing is limited by incomplete knowledge in the load balancer, delay in responding to changes in processor performance, and costs of shifting work between processors. The thesis describes several optimizations which help to address these limiting factors and provides analysis identifying when load balancing can be profitable for certain types of applications.

We have developed a load balancing system for applications consisting of parallelized DOALL and DOACROSS loops [54]. The system involves both the compiler and runtime system in selecting load balancing parameters, with minimal involvement by the programmer. Key performance parameters that can be controlled at run time include the grain size of the application, the frequency of load balancing, and the amount and frequency of work movement.

The rest of this chapter is organized as follows. In Section 1.1, we describe in more detail our assumptions regarding our target system, a cluster of workstations. Then, in Section 1.2, we describe the application domain for our load balancing system and describe how it is parallelized. Section 1.2 also describes notation used in this thesis and presents several example applications. In Section 1.3, we introduce our approach to load balancing. Section 1.4 maps our approach into a control model and identifies areas where control theory provides insight regarding selection of load balancing parameters. Section 1.5 describes how the performance of parallel programs is evaluated in this thesis, and Section 1.6 summarizes our measurements taken on the Nectar system [3]. Section 1.7 discusses related load balancing research. We describe the organization of the remainder of the thesis in Section 1.8.

### 1.1. FEATURES OF TARGET SYSTEM

### **1.1** Features of target system

The environment targeted by our research is a set of workstations connected by a network. We do not assume that we have a dedicated set of workstations, but rather a possibly heterogeneous set of independent, personal workstations. The competing loads on the processors can not be determined until run time. The processors may be shared with other users, but we assume that there is no other load balanced application running on the system. Much of our analysis assumes that the workstations run operating systems where CPU scheduling is based on a fixed time quantum and the scheduling mechanism derives from a round-robin approach; this is typical of multitasking operating systems, such as Unix [4, 32]. For simplicity, we assume that a message passing library for the target system is provided that hides the underlying topology of the network.

Our research does not address fault tolerance, either for the processors or the network. Both network and processor performance are expected to vary, but we assume that communication is reliable and that all processors are available throughout the computation. We assume that communication costs are high relative to access to local memory (or access to shared memory on a shared memory machine) and, thus, direct much effort to reducing communication overhead. Our system attempts to hide communication latencies by overlapping communication costs with computation, but if the network is near saturation, latencies may be too high to be hidden.

The specific system targeted by our prototype implementation is the Nectar system [3] at Carnegie Mellon University. Nectar consists of a high-speed crossbar network connecting a set of Unix workstations. Details of the Nectar environment will be presented in Chapter 7.

### **1.2** Application domain and compiler model

Our target application domain is loop-based code operating on array and scalar data units. Numerical code operating on matrices (e.g., LINPACK [16]) often fits this description. The applications are parallelized by distributing the iterations of one or more loops in the loop nest among the processors in the target system; this thesis considers the case where only one loop is distributed. The application code is replicated on all processors, but loop bounds of the distributed loop are modified so that the processors operate on mutually exclusive subsets of the distributed iterations. Aggregate data structures, e.g., arrays, referenced by the

output matrix by columns.

d by the literature [15, 42, 43, 45]: DOALL and ations (i.e., there is no data dependence between iti; all iterations of the loop may execute in parallel. ces, and a partial ordering of the loop iterations must be obtained by pipelining multiple executions of the output dependences, restructuring of code is necessary 1 as DOALL or DOACROSS loops. For example, in l reduction operation to remove an output dependence e addressed parallelization of loops with recurrences

ALL and DOACROSS loops on distributed memory 1 parallelizing compilers [25, 62, 67, 79] relieve the ited data structures and communication. With parallel e application is to be parallelized and must explicitly elements specified by lower case letters followed by individually bracketed subscripts, e.g. a[i][j]. The language of our parallel implementations is C. Matrices are represented as arrays in all cases, with matrix pseudocode (Figure 1.3b) for sequential versions of the applications and in C (Figure 1.3c) for parallelized versions because our assumed input language is Fortran-like (e.g., AL [67] or Fortran D [25]) and the In most cases, program examples will be shown in a Fortran-like language (Figure 1.3a) or Fortran-like

Figure 1.2: Matrix and vector notation for figures and equations.

b) vector notation

a) matrix notation

a) Fortran-like language b) Fortran-like pseudocode

c) C language

Figure 1.3: Representations for program examples.

### 1.2.2 DOALL loops

owner computes rule. Also, to reduce communication at run time, input data required by multiple iterations of the distributed loop may be replicated on all processors that reference the data requirements, the data on which the iterations operate is distributed in the same fashion, according to the be parallelized by assigning the iterations to processors in any fashion. To minimize communication Loops with independent iterations (no flow dependences, output dependences, or anti-dependences) can

of iterations is executed on each processor (Figure 1.4b). On a homogeneous, dedicated system, each processor is assigned the same number of iterations. Managing the parallelism with a block distribution simply requires adjusting loop bounds so that the appropriate subset The easiest way to parallelize a DOALL loop is to assign blocks of consecutive iterations to processors.

equal workloads throughout the computation. The stride and offset for the loop bounds must be adjusted so decreasing loop bounds. For these applications, the initial equal distribution of work by a block distribution the loop iterations are distributed to the processors in a round-robin, or *cyclic*, fashion so that processors have will cause load imbalance as the application executes on a homogeneous, dedicated system. In these cases, that each processor gets the appropriate set of iterations (Figure 1.4c). In some applications, the DOALL loop is executed multiple times, but with monotonically increasing or

b) Block distribution

c) Cyclic distribution

Figure 1.4: Distribution of DOALL loop.

method may be made independently for each DOALL loop. Our presentation will not explicitly address block-cyclic distributions or nested DOALL loops. Also, for nested DOALL loops, where the distribution is multi-dimensional, the choice of distribution

## 1.2.3 DOACROSS loops

portion of the loop it sends its results to the processor handling the next portion of the loop. Then the sender portions of different instances of the loop are computed in parallel. When a processor finishes with its to processors according to the owner computes rule, a single instance of the loop executes sequentially. proceeds with its portion of the next instance of the loop. the execution of the outer loop. The distributed loop retains the order required by its dependences, but However, when the distributed loop is nested inside another loop, parallelism can be obtained by pipelining the dependences must be maintained. If the data for the loop is distributed and iterations are assigned the iterations can not be run independently. The partial order of execution of the iterations required by If the iterations of a loop to be distributed have flow dependences, e.g., in the inner loop in Figure 1.5a,

communication between logically adjacent processors at the boundaries of the blocks. although other distributions are possible. The distribution is chosen to minimize communication costs For short dependence distances, a block distribution is usually the most efficient because it only requires Again, the simplest distribution of the iterations is a block distribution as shown in Figure 1.5b,

a) Sequential loop

Figure 1.5: Distribution of DOACROSS loop.

# **1.2.4** Dealing with recurrences

programmer with ways to specify simple parallel reductions such as addition, multiplication, minimum, and block distribution must be used. To avoid complicated analysis, some compilers (e.g., AL [67]) provide the is associative and commutative, a cyclic distribution can be used, but if the recurrence is just associative, a as a DOALL or DOACROSS loop depending on the remaining dependences in the loop. If the recurrence if a combining tree is used). When all recurrences have been removed from the loop, the loop can be treated loop terminates, the partial results from the processors are combined to compute the output (in  $O(\log P)$  time private variable on each processor, and each processor computes a portion of the recurrence using the data example, if the recurrence operation is associative, it can be replaced with a parallel reduction operation in sequential loops [8, 17, 50]. The basic process is to recognize recurrences (e.g., using pattern recognition) is removed from the loop. Much research has been directed towards recognizing parallelizable recurrences an efficient associative operator can be extracted from the source code [17]. maximum. However, automatic methods make it possible to parallelize many other types of recurrences if (Figure 1.6) with time complexity  $\frac{n}{P} + \log P$  [8, 17, 50]. The global output variable is replaced by a local and then to test whether the recurrence operators have the required properties for parallelization [50]. For Loops that have output dependences between iterations, i.e., have recurrences, can not be parallelized as from the iterations it executes (in  $O(\frac{n}{P})$  time if work is distributed to processors equally). Then, when the DOALL or as DOACROSS loops. However, in some cases, they can be restructured so that the dependence

## **1.2.5** Example applications

We discuss load balancing issues using three applications as examples: matrix multiplication (MM)

a) Sequential loop with recurrence b) Parallelized loop with reduction

Figure 1.6: Replacement of recurrence with reduction operation.

described above. In this section, we describe the three example applications and how they are parallelized routines in numerically intensive scientific codes and demonstrate the different types of parallelizable loops

## Matrix multiplication (MM)

Our matrix multiplication routine multiplies two  $n \times n$  matrices, **A** and **B**, to produce a third  $n \times n$  matrix,

$\mathbf{\Omega}$

### $\mathbf{C} = \mathbf{A} \times \mathbf{B}$

distributed loop is executed many times, and the distributed input data is reused with each invocation of the information, the compiler modifies the loop bounds for the j loop and generates code to distribute the data. independent results, the loop can be treated as a DOALL loop. To parallelize the application, we replicate product of a row of the A matrix and a column of the B matrix. Because each iteration of the j loop computes Sequential code for matrix multiplication is shown in Figure 1.7. Each element of the C matrix is the dot loop. All iterations of the distributed loop do the same amount of work each time they are executed. run time, for load balancing, the iterations may be redistributed in any fashion as well. In this example, the Because the loop is a DOALL loop, the compiler is free to distribute the iterations in any fashion and, at the **B** matrix. This parallelization is suggested to the compiler using distribution directives. Using this the A matrix and distribute the columns of the B matrix. The output matrix has the same distribution as

Figure 1.7: Sequential code for matrix multiplication (MM).

# Successive overrelaxation (SOR)

Successive overrelaxation (SOR), also called Simultaneous overrelaxation [47], is an iterative method used to solve Laplace's equation, the partial differential equation

$$\frac{\partial^2 U(x,y)}{\partial^2 x} + \frac{\partial^2 U(x,y)}{\partial^2 y} = 0$$

on values computed during the current relaxation phase. We have selected a version (from [67]) where each compared to the convergence condition. The order of computation of the elements of the mesh can affect the a matrix and initialized to an approximation of the solution. For each relaxation phase, each element of the dependences and order of execution for the sequential version of a single relaxation phase for an  $8 \times 8$ the accumulation of the error and norm values. When the recurrence is replaced by a reduction operation, and the old values of its right and lower neighbors (Figure 1.8). The example demonstrates recurrences for mesh point is computed as a weighted average of its old value, the new values of its left and upper neighbors. new mesh values may depend entirely on old mesh values (e.g. red/black SOR [30]), or may depend partially rate of convergence for the computation [30]. Depending on the order of computation of the mesh points, changes between the original and recomputed values are accumulated to compute an error value which is mesh is recomputed as a weighted average of the element and its horizontal and vertical neighbors. The on a square region with known boundary values. The region is described as an  $n \times n$  mesh, represented as matrix; each row of the matrix is computed from left to right. the loop still has loop-carried dependences, so it is treated as a DOACROSS loop. Figure 1.9a shows the

1.9b). Parallelism is extracted by pipelining the loop surrounding the distributed loop (Figure 1.9c). At In our parallelization of SOR, the input/output matrix is distributed to processors by columns (Figure

Then, decomposition determines an upper triangular matrix U and a lower triangular matrix L such that  $L \times U = A$ . is the first step in solving the equation  $A \times x = b$  for x. (The other step is backward substitution.) LU

### LU decomposition (LU)

Our third application example is LU decomposition, a type of Gaussian elimination. Gaussian elimination

Figure 1.9: Dependences and execution order for single successive overrelaxation (SOR) phase for  $8 \times 8$

matrix. Arrows indicate dependences between iterations. Numbers indicate execution order.

that communication is only needed at block boundaries.

(a) Sequential execution (b) Distributed (sequential) execution (c) Pipelined execution

can be replaced with two simpler equations:  $\mathbf{L} \times \mathbf{y} = \mathbf{b}$  can be solved for  $\mathbf{y}$  by forward substitution; then,  $\mathbf{U} \times \mathbf{x} = \mathbf{y}$  can be solved for  $\mathbf{x}$  by backward substitution.  $\mathbf{L}$  and  $\mathbf{U}$  need only be computed once when solving  $\mathbf{A} \times \mathbf{x} = \mathbf{b}$  with multiple  $\mathbf{b}$  input values. We have selected a version of LU decomposition (Figure 1.10) based on the SGEFA routine in the LINPACK benchmark set [16]. (In our version, the BLAS operations have been inlined and simplified.)

Our LU example is parallelized by distributing the rows of the A matrix. The "row elimination" loop, the most computation-intensive portion of the application, is split into two loops so that communication for interchanging values is isolated from the actual elimination computation. The resulting elimination loop is distributed as a DOALL loop; because it has no loop-carried dependences the execution order of the iterations is not a concern. However, communication is necessary between executions of the distributed loop, requiring the processors to synchronize. Also, because the loop bounds of the distributed loop and on the loop it contains depend on the indices of outer loops, the number of iterations of the distributed loop and the size of each iteration change with each execution of the loop.

### **1.3 Our load balancing approach**

Load balancing attempts to minimize the execution time of an application by maximizing the utilization of available resources for productive work. When poor utilization is detected, our load balancing system redistributes work by redistributing the distributed aggregate data structures (Figure 1.11); by the owner computes rule, the distributed loop bounds are modified on each of the processors to correspond with the data local to the processor. This approach to load balancing is beneficial because it keeps communication costs for the application low: since data and loop iterations are assigned to processors according to the owner computes rule, most data accessed by the iterations is local; and, in cases where iterations share data (i.e., applications with DOACROSS loops), work movement can be constrained so that the iterations are usually assigned to the same processor. Also, the units of work for load balancing are loop iterations so, by maintaining the original loop structure of the application, the overhead of switching between tasks is kept to a minimum, i.e., just incrementing a loop counter.

Load balancing works as follows. At predetermined points in the parallelized application code, the processors performing the distributed computation—the *slave processors*—assess their recent performance and send the performance information to a central load balancing process on the *master processor* which

specify the movement necessary to attain the new distribution. Slaves then shift work among themselves to the slaves in proportion to their relative capabilities and computes instructions for the slaves which for recently computed work. The central load balancer computes a new distribution where work is allocated decides how to redistribute work. Performance assessment is based on measurements of rates of computation according to the instructions. The cost of interactions between the slaves and the load balancer are removed

Figure 1.10: Sequential code for LU decomposition (LU).

g dependences in the loop nest so that the load balancer

ompiler and run-time system cooperate in selecting an

unication.

ancing code at appropriate locations in the parallelized frequency of load balancing.

### load balancing

ial feedback control system which uses the difference and 1.0 as its *actuating* or *error* signal. A simplified

2. The central load balancer is the *controller* for the he *plant*. The central load balancer manipulates the slave processors. The *disturbances* in the system are of load balancing is the *sampling rate* for the system.

Figure 1.12: Simplified model of load balancer as a digital feedback control system.

other slaves are underutilized ( $u_i < 1.0$ ). The *error* that is input to the controller is  $e_i$ , the fraction of by the slaves during one cycle of the control loop is the maximum time taken by any of the slaves. The each slave that is underutilized  $(1.0 - u_i)$ . The controller shifts work from more utilized processors to less time; thus, the slave (or slaves) with the maximum computation time is 100% utilized ( $u_i = 1.0$ ) and the utilization of each slave,  $u_i$ , is computed by dividing the computation time for the slave by the maximum utilized processors until all processors are fully utilized, i.e., load is balanced Figure 1.13 shows the control system in more detail. The total time for the computation performed

system, e.g., identifying the range of frequencies over which the system works well, how quickly the system to accurately characterize the system. We might be able to develop proofs regarding the performance of the for the system (for some definition of optimality). Using control system techniques, we might also be able responds to changes in performance, and how quickly the work distribution converges to the desired result. If we can create a simple control model for our system, we might be able to derive optimal parameters

degrees of freedom. In addition, the system is non-linear, making finding exact solutions to the differential equations for the system unlikely; most methods for solution of nonlinear systems involve engineering do not have unique solutions, and trial and error approaches must be used in their design due to the extra input multiple output (MIMO) system and can not be uncoupled into simpler systems. MIMO systems However, several factors make modeling and analysis of our system difficult. The system is a multiple

#### 1.5. EVALUATING PARALLEL PERFORMANCE