## Programmable, Energy-minimal Computer Architectures

Graham Gobieski

CMU-CS-22-145

August 2022

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Thesis Committee: Nathan Beckmann, Co-Chair Brandon Lucia, Co-Chair Todd Mowry Kenneth Mai Tony Nowatzki, External

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### Copyright © 2022 Graham Gobieski

This research was sponsored by an Apple PhD Fellowship, the National Science Foundation under award numbers CNS-1526342 and CCF-1815882, and the U.S. Army under award number W911NF1820218. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

## Abstract

Ultra-low-power (ULP) sensor devices are increasingly being deployed for a variety of use-cases that require sophisticated processing of sensed data. Regardless of the deployment, energy-efficiency is critical; for battery-powered devices, energy-efficiency determines device lifetime, while for energy-harvesting devices, energy-efficiency determines performance by dictating the frequency of recharging. Unfortunately, existing devices pay a severe energy tax for their programmability, wasting energy in instruction-fetch/decode, pipeline-control and data supply. Further, offloading computation from an edge-device to the cloud is not practical as communication costs an order-of-magnitude more energy than local compute. The solution is to redesign the ULP sensor system stack to increase the energy-efficiency of on-board compute and enable sophisticated processing of sensed data. This thesis proposes such a stack — from software to silicon — that leverages new execution models to reduce the tax of programmability and achieve extreme energy-efficiency. Specifically it contributes 1) SONIC, a software framework that enables machine inference on intermittentlyoperating, energy-harvesting devices, 2) MANIC, a vector-dataflow co-processor (and corresponding silicon prototype), 3) SNAFU, an ULP coarse-grain-reconfigurable-array (CGRA) generation framework and architecture, and 4) RIPTIDE, a co-designed dataflow compiler and energy-minimal CGRA. SONIC was the first demonstration of machine inference on a commercial, intermittently-operating device, but also exposed the flaws of such devices. MANIC fixed these problems by combining vector execution to amortize instruction fetch with dataflow execution to minimize data supply energy by forwarding intermediate values directly from producers to consumers. SNAFU extended MANIC's vector-dataflow to further reduce energy by minimizing the toggling of shared pipeline resources. Its generated CGRAs implement spatial-vectordataflow execution that lays out computation across a fabric of PEs, keeping each PE configured in the same way throughout kernel execution. Finally, RIPTIDE improves overall system efficiency by compiling and offloading to its CGRA, programs written in C with complex control-flow and irregular memory accesses. Together these contributions form the basis of a new ULP sensor system stack that is > 2 orders-ofmagnitude more efficient than existing systems, enabling new emerging applications that require intelligence "beyond-the-edge."

## Acknowledgements

There are many people to thank for helping me throughout my PhD. First my research advisors, Professors Brandon Lucia and Nathan Beckmann. Brandon and Nathan have taught me how to be a good researcher. They helped me find interesting problems and guided me in my pursuit of solutions. They have complementary advising styles that has a made us a formidable team. Brandon always has a deep understanding of the big picture, which has kept my research grounded. Nathan's detail-oriented approach has made my research stronger and more polished. The success I have enjoyed during my PhD would not have been possible without them.

I am grateful to my close collaborators, including Oguz Aatli, Souradip Ghosh, Professor Kenneth Mai, Danny Bankman, Professor Todd Mowry, and Professor Tony Nowatzki. Oguz, Ken, and Danny were pivotal in our successful tape-out of MANIC, guiding me throughout the tape-out process and helping me verify, debug, and optimize our design. Tony, Todd, and Souradip were central to the development of RIPTIDE. Bouncing ideas off of Tony and Todd during weekly research meetings, helped me refine ideas and improved the design of RIPTIDE. Souradip's contributions to RIPTIDE's compiler were critical to the project's success and I thoroughly enjoyed our work together.

I have been fortunate to receive an Apple PhD Fellowship in AI/ML and spend a summer at Apple working on machine learning architecture. Jaewon Shin, my manager, helped me navigate research in industry and encouraged me to be independent and pursue difficult but relevant problems.

I want to thank additional CMU colleagues and administrative staff. I thank Harsh Desai, Alexei Colin, and Emily Ruppel for answering my questions on microelectrics and for their support of my work on intermittent computing. I also want to thank the other PhD students in Brandon's and Nathan's groups for providing extremely useful feedback on my research during practice talks and weekly lunch meetings. Finally, I am grateful to Deborah Cavlovich for helping me navigate the logistics of the PhD.

There are several friends I want to highlight that provided advice and support throughout my graduate studies. Michael Rudow, Jack Kosaian, Matt Butrovich, Han Zhang, and Guilio Zhou are fellow CS PhD students and friends. They not only provided an outlet for discussing my PhD, but also helped me experience Pittsburgh. I am also grateful to George Yu. He provided me valuable advice and a different perspective during our biweekly discussions. He has also been the very best travel companion, willing to meet in whatever corner of the world.

Last but not least, I want to thank my parents and my brother. My parents, Beth and John, encouraged me to pursue a PhD and helped me through the lows and the highs of the process. My brother, Reid, is my best friend and has always been there in whatever situation. I am the man that I am today because of them.

# Contents

| A                       | Abstract iii                                                   |                                                                                                                                                                                                                                                                                   |                                                                                           |  |  |  |  |  |

|-------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--|--|--|--|--|

| Acknowledgements        |                                                                |                                                                                                                                                                                                                                                                                   |                                                                                           |  |  |  |  |  |

| 1                       | <b>Intr</b><br>1.1<br>1.2<br>1.3                               | coduction         Challenges         Objective of this work         Outline                                                                                                                                                                                                       | <b>1</b><br>1<br>3<br>5                                                                   |  |  |  |  |  |

| <b>2</b>                | Bac                                                            | kground                                                                                                                                                                                                                                                                           | 7                                                                                         |  |  |  |  |  |

|                         | <ol> <li>2.1</li> <li>2.2</li> <li>2.3</li> <li>2.4</li> </ol> | Low-power embedded devices2.1.1Device operation2.1.2Intermittent execution model2.1.3COTS ULP DevicesEdge inference2.2.1Algorithmic improvements to NN inference2.2.2Inference accelerators2.3.1Vector architectures2.3.2Dataflow architecturesCoarse-grain reconfigurable arrays | $\begin{array}{c} 7 \\ 7 \\ 8 \\ 9 \\ 10 \\ 10 \\ 10 \\ 11 \\ 11 \\ 12 \\ 12 \end{array}$ |  |  |  |  |  |

|                         | 2.4                                                            | 2.4.1Types of CGRAs2.4.2Low-power CGRAs2.4.3Compilation2.4.4Compare & contrast different CGRA designs                                                                                                                                                                             | 12<br>13<br>13<br>14<br>15                                                                |  |  |  |  |  |

| 3                       | SOI                                                            | ONIC: Deploying DNNs on intermittent embedded devices                                                                                                                                                                                                                             |                                                                                           |  |  |  |  |  |

|                         | 3.1                                                            | Motivation for intermittent inference                                                                                                                                                                                                                                             | 18<br>19<br>19                                                                            |  |  |  |  |  |

|                         | 3.2                                                            | System overview                                                                                                                                                                                                                                                                   | 22                                                                                        |  |  |  |  |  |

|                         | 3.3                                                            | Optimal DNN compression with GENESIS3.3.1Neural networks under consideration3.3.2Fitting networks on energy-harvesting systems3.3.3Choosing a neural network configuration                                                                                                        | 22<br>23<br>23<br>24                                                                      |  |  |  |  |  |

|                         | 3.4                                                            | Efficient intermittent inference with SONIC3.4.1The SONIC API3.4.2The SONIC runtime implementation                                                                                                                                                                                | $25 \\ 25 \\ 25$                                                                          |  |  |  |  |  |

|                         | 3.5                                                            | Hardware acceleration with TAILS3.5.1Automatic one-time calibration3.5.2Accelerating inference with LEA                                                                                                                                                                           | 28<br>29<br>29                                                                            |  |  |  |  |  |

|                         | 3.6                                                            |                                                                                                                                                                                                                                                                                   | $\frac{20}{29}$                                                                           |  |  |  |  |  |

| 3.6         Methodology |                                                                |                                                                                                                                                                                                                                                                                   |                                                                                           |  |  |  |  |  |

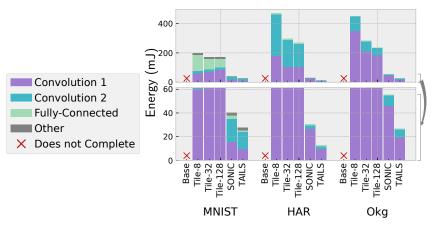

|   |              | 3.7.1 SONIC & TAILS accelerates intermittent inference           |

|---|--------------|------------------------------------------------------------------|

|   |              | 3.7.2 Loop continuation nearly eliminate intermittence overheads |

|   |              | 3.7.3 SONIC & TAILS use much less energy than tiling             |

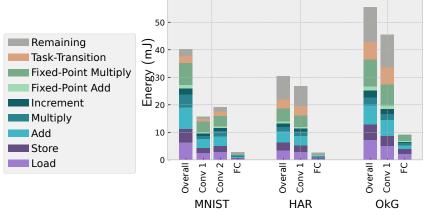

|   |              | 3.7.4 Where does SONIC's energy go?                              |

|   | 3.8          | Discussion                                                       |

|   |              |                                                                  |

| 4 |              | NIC: An energy-efficient, vector-dataflow co-processor           |

|   | 4.1          | Vector-Dataflow Execution                                        |

|   |              | 4.1.1 Vector execution                                           |

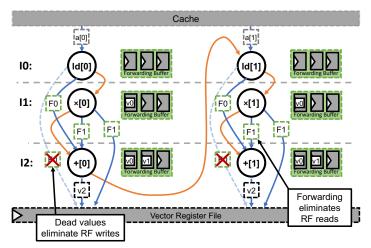

|   |              | 4.1.2 Dataflow instruction fusion                                |

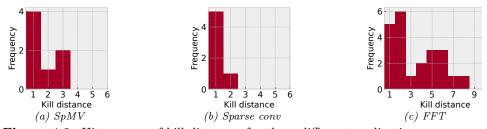

|   |              | 4.1.3 Vector register kill points                                |

|   |              | 4.1.4 Applications benefit from vector-dataflow                  |

|   |              | 4.1.5 Synchronization and memory consistency                     |

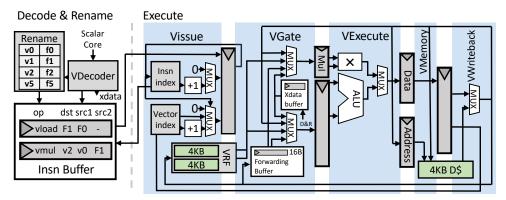

|   | 4.2          | MANIC Architecture                                               |

|   |              | 4.2.1 Vector ISA                                                 |

|   |              | 4.2.2 Microarchitecture                                          |

|   |              | 4.2.3 Memory system                                              |

|   |              | 4.2.4 Putting it together with an example                        |

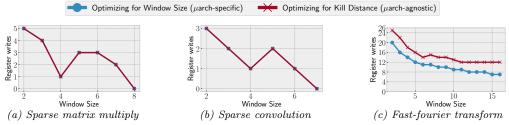

|   |              | 4.2.5 Microarchitecture-agnostic dataflow scheduling             |

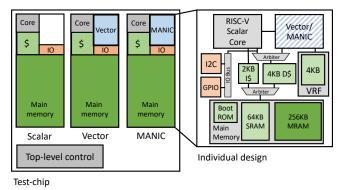

|   | 4.3          | MANIC-SILICON                                                    |

|   |              | 4.3.1 Chip design                                                |

|   |              | 4.3.2 Verification and bring-up of MANIC-SILICON                 |

|   | 4.4          | Methodology                                                      |

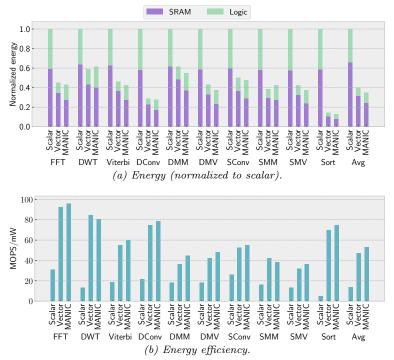

|   | 4.5          | Evaluation                                                       |

|   | 4.6          | Discussion                                                       |

| 5 | CN           | AFU generates ULP CGRAs                                          |

| 9 | 5.1          | Overview                                                         |

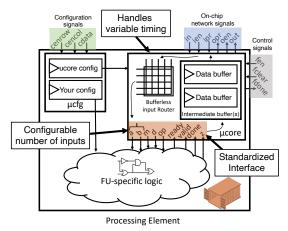

|   | $5.1 \\ 5.2$ | Designing SNAFU to maximize flexibility                          |

|   | 0.2          |                                                                  |

|   |              |                                                                  |

|   |              | 5.2.2 SNAFU'S PE standard library                                |

|   |              | 5.2.3 Generating a CGRA fabric                                   |

|   | 5 0          | 5.2.4 Compilation                                                |

|   | 5.3          | Designing SNAFU to minimize energy                               |

|   |              | 5.3.1 Spatial vector-dataflow execution                          |

|   |              | 5.3.2 Asynchronous dataflow firing without tag-token matching    |

|   |              | 5.3.3 Statically routed, bufferless on-chip network              |

|   |              | 5.3.4 Minimizing buffers in the fabric                           |

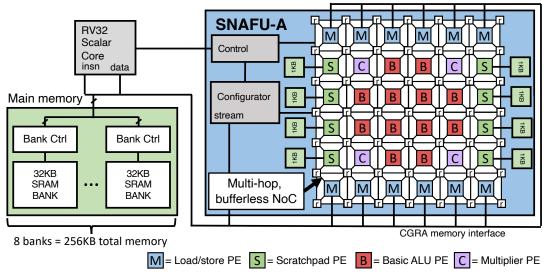

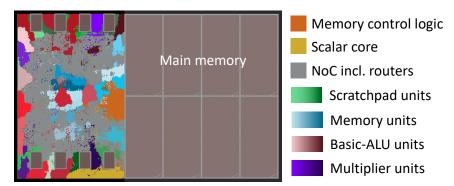

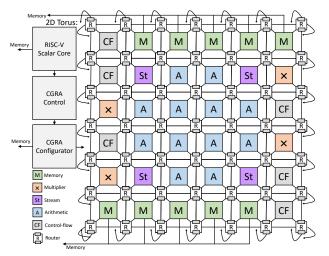

|   | 5.4          | SNAFU-ARCH: A Complete ULP System w/ CGRA                        |

Sensitivity studies

Experimental Methodology

The Cost of Programmability

5.4.1

5.4.2

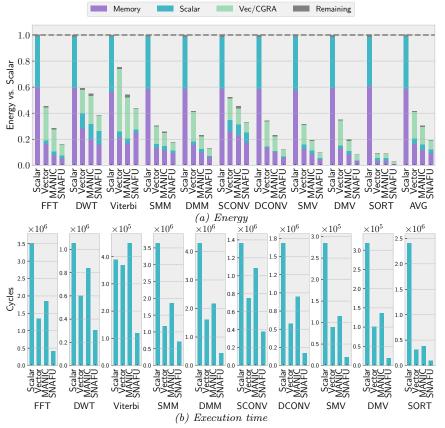

5.6.1

5.6.2

5.6.3

5.5 5.6

5.7

5.8

| 6 | Rip  | Tide:       | a programmable, energy-minimal dataflow compiler and                                                                              |

|---|------|-------------|-----------------------------------------------------------------------------------------------------------------------------------|

|   | arch | nitectu     | re 71                                                                                                                             |

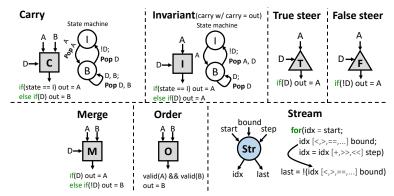

|   | 6.1  | RipTi       | de Instruction Set Architecture                                                                                                   |

|   |      | 6.1.1       | Control-flow operators                                                                                                            |

|   |      | 6.1.2       | Synchronization operators                                                                                                         |

|   |      | 6.1.3       | Stream operators                                                                                                                  |

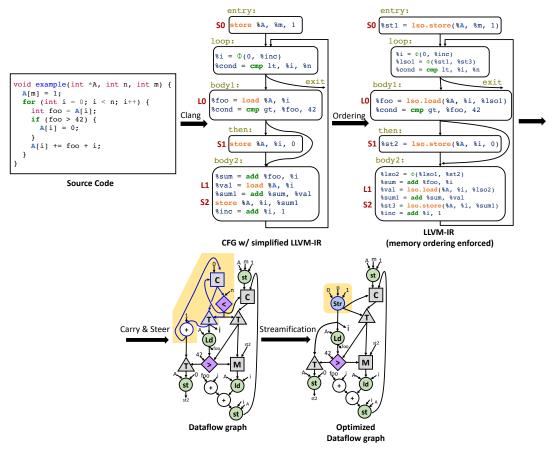

|   | 6.2  | RipTi       | de Compiler                                                                                                                       |

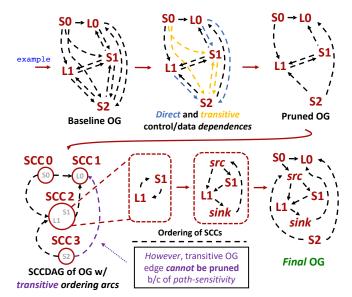

|   |      | 6.2.1       | Memory-ordering analysis                                                                                                          |

|   |      | 6.2.2       | Control-flow operator insertion                                                                                                   |

|   |      | 6.2.3       | Stream fusion                                                                                                                     |

|   |      | 6.2.4       | Mapping DFGs to hardware                                                                                                          |

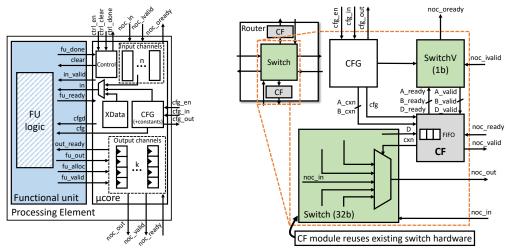

|   | 6.3  | RipTi       | de Microarchitecture                                                                                                              |

|   |      | 6.3.1       | Tagless dataflow scheduling    79                                                                                                 |

|   |      | 6.3.2       | Processing elements                                                                                                               |

|   |      | 6.3.3       | Bufferless NoC                                                                                                                    |

|   |      | 6.3.4       | Control flow in the NoC                                                                                                           |

|   | 6.4  | Exper       | imental Methodology                                                                                                               |

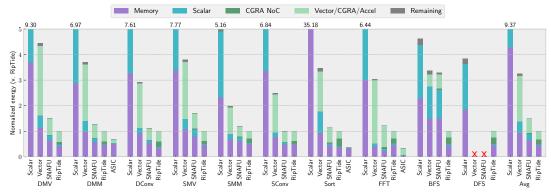

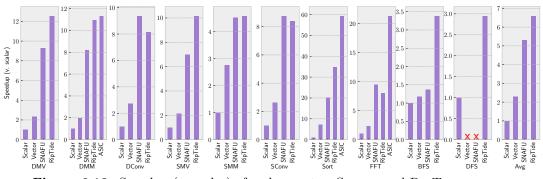

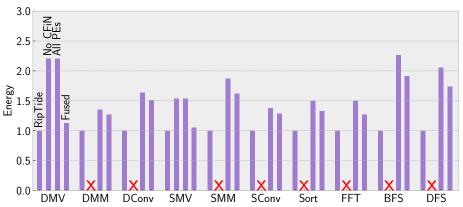

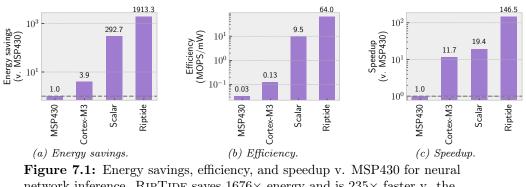

|   | 6.5  | Evalua      | $ation \dots \dots$         |

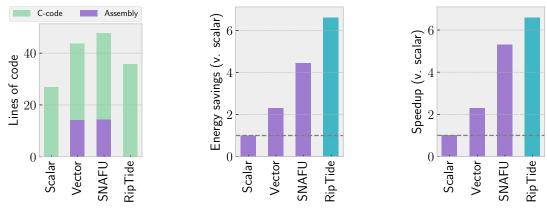

|   |      | 6.5.1       | Main results                                                                                                                      |

|   |      | 6.5.2       | RIPTIDE v. prior low-power CGRAs                                                                                                  |

|   |      | 6.5.3       | Compiler characterization                                                                                                         |

|   |      | 6.5.4       | Control flow in the NoC saves energy & area                                                                                       |

|   | 6.6  | Concl       | usion & Architectural Implications                                                                                                |

| 7 | Fut  | ure wo      | ork 91                                                                                                                            |

| • | 7.1  |             | ifying the progress made                                                                                                          |

|   |      | 7.1.1       | Is compute energy efficiency still a bottleneck?                                                                                  |

|   | 7.2  | • • • • • • | e research directions                                                                                                             |

|   | •    | 7.2.1       | Area                                                                                                                              |

|   |      | 7.2.2       | Performance                                                                                                                       |

|   |      | 7.2.3       | Compilation                                                                                                                       |

| 8 | Cor  | clusio      | n 97                                                                                                                              |

| 0 | COL  | iciusio     | 11 37                                                                                                                             |

| Α |      |             | t-based scheduling 99                                                                                                             |

|   | A.1  |             | $J$ 's mapper $\dots \dots \dots$ |

|   | A.2  |             | $\begin{array}{c} \text{IDE's mapper}  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $                           |

|   |      | A.2.1       | ILP formulation                                                                                                                   |

|   |      | A.2.2       | SAT formulation                                                                                                                   |

## Chapter 1

## Introduction

Ultra-low-power (ULP) sensor devices are increasingly being deployed for a variety of use-cases from in-body health sensing to civil infrastructure monitoring to tiny chipscale satellites [255]. These devices are composed of low-power sensors attached to an ULP microcontroller, which communicates to other edge devices or to the cloud via a low-power radio, all powered by a small battery or from energy harvested from the environment. The sensors on these devices are increasingly capable — ranging from high-definition image sensors [169] to multi-sensor arrays [131] — producing a growing volume of data. To make sense of the data, sophisticated processing, like machine learning (ML) inference using a deep neural network (DNN) or digital signal processing (DSP), is required. But sophisticated processing requires resources that existing ULP devices lack. In particular, ULP sensor systems are extremely energy-constrained – batteries limit device lifetimes and energy harvested from the environment is extremely scarce. One solution is to offload processing, but communication uses much more energy than local compute. Thus, the energy-efficiency of onboard compute is the key determinant of application success. However, existing, general-purposes systems suffer fundamental inefficiencies. And highly-specialized systems (i.e. ASICs) compromise on programmability, a requirement as applications emerge in the domain. So how can we achieve extreme energy-efficiency to enable sophisticated computations on ultralow-power systems without sacrificing programmability? The answer — a new system stack — is the objective of this work.

#### 1.1. CHALLENGES

There are a multitude of challenges, detailed below, to supporting sophisticated processing on ULP sensor devices. These devices are severely resource- and energyconstrained, complicating application development and limiting the lifetimes of deployed devices. There is a need for extreme energy-efficiency without sacrificing programmability. This is the central theme to the this thesis.

#### Offloading computation does not scale

Offloading computation from a ULP device to a more powerful nearby computer (e.g., at the "edge" or cloud) is one approach to the increased processing sophistication and sensed data volume of applications in the ULP domain. The more data a sensor produces, though, the more data the device must communicate. Unfortunately, transmitting data compromises security, clogs networks, and takes much more energy per byte than sensing, storing, or locally computing on those data [84,145]. While a high-powered device like a smartphone, with a high-bandwidth, long-range radio, can afford to offload data to the edge or cloud, this is not practical for power-, energy-, and bandwidth-limited sensor devices [74,84].

#### Local compute reduces cost of communication

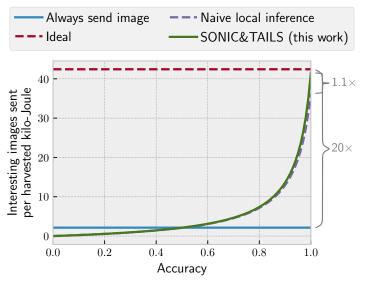

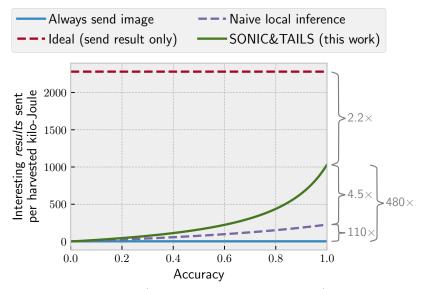

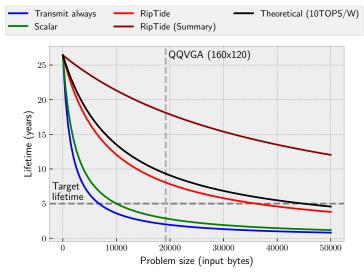

Since offloading is infeasible, the alternative is to process data *locally* on the sensor node itself. Our work, SONIC, demonstrates how systems can use commodity offthe-shelf microcontrollers (COTS MCU) to filter sensed data locally so that only meaningful data (as defined by the application) are transmitted. Processing data locally minimizes the high energy cost of communication, reducing energy by  $\approx 20 \times$ compared to a design that always offloads, but makes the application highly sensitive to the energy-efficiency of computation.

#### Energy-efficiency is critical to end-to-end system performance

Energy efficiency is the primary determinant of end-to-end system performance in ULP embedded systems. For battery-powered devices [56, 203], energy efficiency determines device lifetime: once a single-charge battery has been depleted the device is dead and it is impractical to replace the battery on millions (or more [219]) deployed devices. Even rechargeable batteries are limited in the number of recharge cycles, and a simple data-logging application can wear out the battery in just a few years [113, 172]. For energy-harvesting devices [48,101,103,249,256], energy efficiency determines device performance. These devices store energy in a capacitor and spend most of their time powered off, waiting for the capacitor to recharge. Greater energy efficiency leads to less time waiting and more time doing useful work [71].

#### Existing devices are energy-inefficient

However, ULP COTS MCUs used in many deeply embedded sensor nodes (e.g., TI MSP430, ARM M0+ & M4+) are energy-inefficient. These MCUs are generalpurpose, programmable devices that support a variety of applications. But this generality comes at at a high power, energy, and performance cost.

Programmability is expensive in three main ways [24, 92, 107]. First, *instruction* supply consumes significant energy: in the best case, the energy of an instruction cache hit, and in the worst case, the energy of a main memory read and instruction cache fill. Lacking sophisticated microarchitectural features such as superscalar and out-of-order execution pipelines [110, 233], the energy overhead of instruction supply constitutes a significant fraction of total operating energy. Second, data supply through register file (RF) access also consumes significant energy. And third, pipeline-control can burn significant energy as resources are reconfigured from cycle-to-cycle to run different operations. Together, instruction fetch/decode, data supply, and pipeline-control can consume at least 54.4% of the average execution energy across a variety of representative workloads for ULP devices.

#### Specialization can limit programmability

To combat the energy costs of generality, some recent work has turned to microarchitectural specialization, making a system energy-efficient at the expense of generality and programmability [39–41, 75, 143, 237]. Specialization customizes a system's control and datapath to accommodate a particular workload (e.g., deep neural networks [39,40]), eliminating inessential inefficiencies like instruction supply, RF access, and pipeline-control. The downsides of specialization are its high non-recurring engineering cost and its inability to support a wide range of applications. Given the emerging nature of applications (e.g., due to new machine learning algorithms [116]) in the ULP domain, specialization is premature. New architecture must be highly programmable, while at the same time being extremely energy-efficient.

#### Existing execution models are flawed

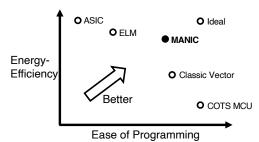

Programmability and energy efficiency might seem to be wholly incompatible, considering the gap between fixed-function ASIC designs and COTS scalar designs.

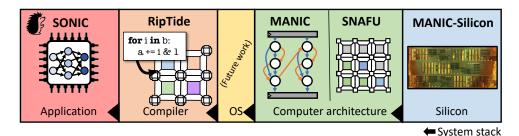

**Figure 1.1:** This thesis contributes a new energy-efficient system stack: SONIC is a software framework that enables intermittent inference, RIPTIDE compiles C-code to ULP CGRAs, MANIC is an ULP vector-dataflow co-processor, SNAFU generates ULP CGRAs, and MANIC-SILICON is a silicon prototype of MANIC.

However, the trade-off is not as pronounced as these designs would lead one to believe. Their execution models are at the extremes; the fixed-function execution model of ASIC designs limits programmability, while the scalar execution model of COTS MCUs wastes significant energy. There is room in the middle for alternative execution models that balance programmability and energy-efficiency. For example, one starting point is vector execution, which slightly reduces programmability, but amortizes instruction supply energy improving overall energy-efficiency. Developing new execution models, therefore, is critical to resolving the tension between programmability and energy-efficiency.

#### Choosing the right programming interface

Programmability needs to come in the correct form. It is more than just configurability. A design that's highly configurable, but difficult to program from a high-level language will have limited adoption. Legacy software needs to be supported out-ofthe-box with minimal changes so that developers can quickly adopt new hardware. However, there are downsides (e.g., incomplete information on memory-ordering and parallelism) to sticking with established programming interfaces. Choosing the right programming interface and building a compiler to target new hardware is as important as the hardware itself.

#### **1.2. OBJECTIVE OF THIS WORK**

This work proposes a complete system stack that leverages new execution models to maximize energy-efficiency without significantly sacrificing programmability. This approach enables new applications in the ULP domain as improved energy efficiency makes sophisticated workloads practical, while maintaining support for programmability allows for iteration, development of new algorithms, and quick deployment. Our work fills out the stack – from software to compilation to computer architecture and to silicon implementation. Together these works support the following thesis:

High energy-efficiency can be achieved across the system stack from software to silicon without significantly compromising on programmability by leveraging new execution models to reduce instruction fetch/decode, pipeline-control, and data supply energies.

The following contributions form the basis for the thesis and the new system stack.

#### [Software] SONIC is the first demonstration of DNN inference on an energyharvesting device (Ch. 3):

SONIC is the software-component of the new ULP sensor system stack. It is an intermittence-aware software system with specialized support for DNN inference. SONIC runs optimized networks found using GENESIS, a tool that automatically compresses networks to balance inference accuracy and energy. SONIC introduces loop continuation, a new technique that dramatically reduces the cost of guaranteeing correct intermittent execution for loop-heavy code like DNN inference. Across three neural networks on a commercially available MCU, SONIC reduces inference energy by  $6.9 \times$  over the prior state-of-the-art.

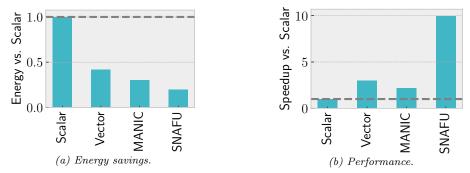

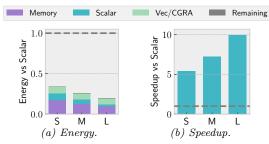

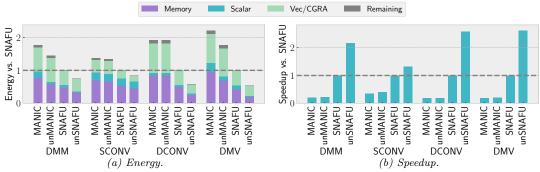

[Architecture] MANIC is an energy-efficient vector-dataflow co-processor (Ch. 4): MANIC contributes new computer architecture to the ULP system stack. It is an efficient vector-dataflow architecture for ultra-low-power embedded systems, achieving high energy-efficiency without sacrificing programmability and generality. MANIC introduces vector-dataflow execution, allowing it to exploit the dataflows in a sequence of vector instructions and amortize instruction fetch and decode over a whole vector of operations. By forwarding values from producers to consumers, MANIC avoids costly vector register file reads. By carefully scheduling code and avoiding dead register writes, MANIC avoids costly vector register writes. On average, MANIC is 3.4× more energy efficient than a scalar baseline and 12% more energy-efficient than a vector baseline.

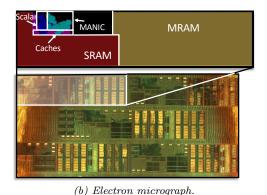

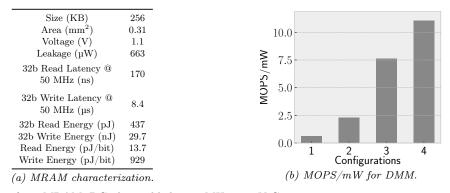

#### [Silicon] MANIC-SILICON proves the energy-efficiency of MANIC (Sec. 4.3):

MANIC-SILICON represents the silicon component of the new ULP sensor system stack. It is a prototype of the MANIC architecture that demonstrates the energy-efficiency of the design. MANIC-SILICON is a complete, standalone system possessing a RISC-V scalar core, the MANIC co-processor, a data cache, an instruction cache, and main memory composed of 64KB of SRAM and 256KB of non-volatile embedded MRAM. The design is implemented in Intel 22FFL high-threshold-voltage process and achieves a max efficiency of 256 MOPS/mW drawing just  $19\mu$ W at 4MHz.

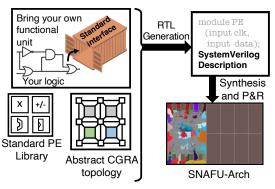

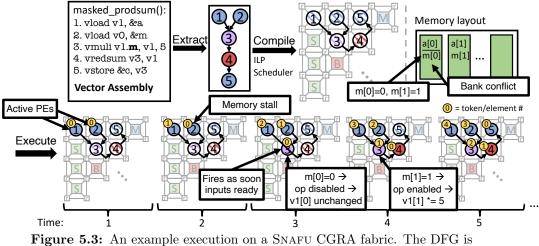

#### [Architecture] SNAFU generates ULP CGRAs (Ch. 5):

SNAFU is another new computer architecture in the ULP system stack. SNAFU generates ULP coarse-grain reconfigurable arrays (CGRAs) that implement spatial-vector-dataflow execution, building on MANIC's vector-dataflow execution model. In spatial-vector-dataflow execution, a dataflow graph (DFG) is mapped spatially across the fabric of processing elements, applying the same DFG to many input data values, and routing intermediate values directly from producers to consumers. This minimizes instruction and data-movement energy, just like MANIC, and reduces pipeline-control energy by eliminating unnecessary switching activity as operations do not share execution hardware. SNAFU uses 41% less energy and runs  $4.4 \times$  faster than MANIC.

#### [Architecture & Compilation] RIPTIDE is an energy-minimal dataflow compiler & CGRA architecture (Ch. 6):

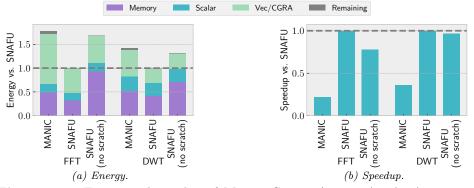

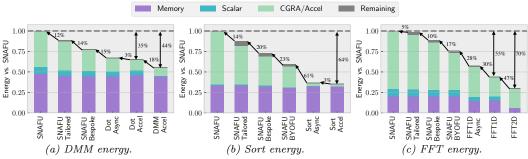

RIPTIDE rounds out the system stack, providing an ULP CGRA *architecture* and co-designed *compiler* that compiles high-level C-code to the new hardware. It proposes a new set of program primitives that support arbitrary controlflow, irregular memory accesses, common program idioms, and memory ordering without needing to tag values to save energy; this requires careful analysis by the compiler to guarantee correctness, particularly to enforce control-flow and memory ordering. To save even more energy, RIPTIDE offloads control-flow operations into the on-chip network. RIPTIDE observes that these operations are simple but prevalent, so it is wasteful to assign them to processing elements. Instead, RIPTIDE reuses existing hardware in the on-chip network to directly implement control-flows operations. Compared to SNAFU, RIPTIDE uses 25% less energy and is also 17% faster without requiring hand-coded assembly.

Together SONIC, MANIC, MANIC-SILICON, SNAFU, and RIPTIDE form the new energy-efficient system stack. This stack is capable of running C programs within  $2.3 \times$  of the energy of ASICs, enabling sophisticated applications involving DNN inference to last 5 to 10 years on a single AA battery. This combination of programmbility and state-of-the-art energy efficiency represents a paradigm-shift for ULP sensor systems. Deployed devices do not need to be frequently replaced or recharged, reducing maintenance costs and carbon footprints. At the same time, applications can be updated in the field, allowing the device to adapt to environmental changes and improve onboard processing. In short, this new system stack will facilitate development of emerging applications in the ULP sensor domain.

#### 1.3. OUTLINE

This thesis is divided into eight chapters, including this introduction. The second chapter provides useful background on embedded systems, intermittent computing, vector architectures, dataflow architectures, and coarse-grain reconfigurable arrays. The next four chapters describe SONIC, MANIC & MANIC-SILICON, SNAFU, and RIP-TIDE in detail. The order of these chapters follows the timeline of development. This structure will make clear the connection between each work: SONIC, despite being the first to demonstrate DNN inference on an energy-harvesting device, exposed the drawbacks of existing ULP devices' scalar execution model; MANIC solved these drawbacks with vector-dataflow execution; SNAFU improved on MANIC with spatial-vector-dataflow execution; and RIPTIDE built on SNAFU to further improve general-purpose programmability and overall system energy-efficiency. Finally, the last two chapters discuss exciting future research directions in ULP computer architecture and CGRAs and then conclude.

### Chapter 2

## Background

This chapter discusses relevant prior work that this thesis builds on. The chapter is split into discussions on 1) low-powered embedded devices, 2) edge inference, 3) related efficient programmable architectures, and 4) coarse-grain reconfigurable arrays. The first includes a general overview of ULP sensor devices and an introduction to intermittent computing. The second discusses algorithmic improvements and hardware accelerators for efficient neural network inference. The third describes relevant vector machine and dataflow architectures. And the fourth expands on a specific class of spatial-dataflow architectures, called coarse-grain reconfigurable arrays.

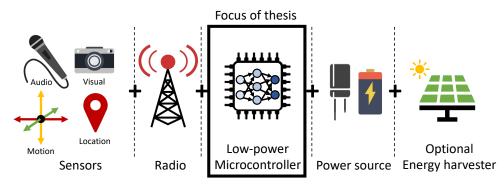

**Figure 2.1:** Typical ULP device is composed of 1) series of sensors (e.g., camera, microphone, GPS, accelerometer, etc.), 2) low-power radio (e.g., LoRaWAN or BLE), 3) low-power microcontroller, the focus of this thesis, 4) power source like a battery or capacitor and 5) an optional energy harvester like a solar cell.

#### 2.1. LOW-POWER EMBEDDED DEVICES

Low-power embedded sensor devices as shown in Fig. 2.1 are composed of: 1) low-powered sensors (e.g. HiMax HM01B0 camera [3]), 2) a low-powered radio (e.g. LoRaWAN [11] or BLE [229]), 3) an ULP microcontroller (e.g. ARM M0 [1] or TI-MSP430 [110], 4) a power source like a coin-cell battery or capacitor, and 5) an optional energy harvester (e.g. solar cell or RF harvester [197]). Energy dictates the viability of these devices. For battery-powered devices energy dictates lifetime, and for energy-harvesting devices that operate intermittently, energy dictates performance by controlling the time spent waiting for energy to be collected. On top of this, the MCUs of these are devices are simple, severely resource-constrained and energy-inefficient.

#### 2.1.1 Device operation

ULP sensor devices operate on a duty cycle: periodically sensors collect data from the environment, the microcontroller processes the data, and then data is transmitted via the low-power radio. This interval of data collection is dictated by application requirements (i.e. how often a particular event will take place), the required lifetime for the device (particularly for battery-powered devices), and energy-consumption of the different components of the device. Application requirements have to be carefully balanced with the energy consumption of the MCU, sensors, and radio.

**Battery-backed systems:** Some devices rely on batteries [56,113,203]. These devices can quickly deplete their battery even if the application is simply logging data. Battery lifetimes can be improved by adding a energy harvester, like a solar cell or radio-frequency harvester, that can recharge the battery. However, rechargeable batteries have limited recharge cycles and may not be able to cope with extreme environmental conditions (e.g. too hot/cold temperatures).

Capacitor-backed systems: Instead a capacitor can be used to buffer energy from an energy harvester and power the device. Capacitors have an effective lifetime (> 10 years) that often exceeds the lengths of application deployments. But they do not offer the same energy density as batteries. In a capacitor-backed system, the application often must wait for energy to be collected in the capacitor by the energyharvester. This makes application performance dependent on the availability of energy in the environment. Energy availability is not constant — input power can vary with environmental conditions. For example, weather and time-of-day significantly (by several orders of magnitude) impact the amount of energy a solar cell can harvest. These operating conditions complicate execution and affect the device's ability to quickly react to changing environmental conditions.

#### 2.1.2 Intermittent execution model

Systems that harvest energy and store that energy in a hardware buffer (e.g. capacitor) usually operate intermittently. This is because device operating power usually exceeds power harvested from the environment. To operate despite this weak input power, a device slowly accumulates energy in a hardware buffer and operates when the buffer is full. The device drains the buffer as it operates, then it turns off and waits for the buffer to fill again.

Software executes in the *intermittent execution model* on these energy-harvesting devices [36, 114, 148, 158, 159, 200]. In intermittent execution, software progresses in bursts, resetting at frequent power failures. Existing devices [110, 230] mix volatile state (e.g. registers and SRAM) and non-volatile memory (e.g. FRAM). A power failure clears volatile state while non-volatile memory persists. Repeated power failures impede progress [200], and may leave memory inconsistent due to partially or repeatedly applied non-volatile memory updates [148]. These progress and consistency issues lead to incorrect behavior that deviates from any continuously-powered execution [46]. Specifically, write-after-read (WAR) dependences lead to inconsistent memory and differing control-flow as re-execution can expose the value from the latter write to the read, which is not possible in continuously-powered execution.

Prior work addressed progress and memory consistency using software checkpoints [105, 148, 235], non-volatile processors (NVPs) [149, 150], and programming models based around atomic tasks [47, 104, 151, 151]. Non-volatile processors require technology process changes and constantly pay a tax for their non-volatility (i.e., nonvolatile elements cost more energy than volatile elements). Software-checkpointing and task-based runtime systems, on the other hand, can be deployed on existing devices with limited impact on energy since the amount of volatile state is small.

#### Checkpointing systems

Checkpoint-based systems insert checkpoints into programs using compiler, runtime, and hardware support. Just-in-time (JIT) checkpointing is the most popular strategy. In JIT checkpointing, hardware monitors the voltage of the capacitor and when the voltage dips below a predetermined threshold indicating a power failure is imminent, triggers an interrupt that checkpoints program state. The interrupt writes back the volatile state of the program, including program counter and stack, to non-volatile memory. Then when power resumes, the runtime system restores the volatile state and jumps back to the place in execution where power failed. This system is often transparent to the programmer, but may complicate (or even lead to incorrect) use of peripherals [220] and interrupts.

#### Task-based runtime systems

An alternative to checkpointing are task-based runtime systems. These systems avoid frequent checkpoints by restarting from a task's start after power failure, at which point all register and stack state must be re-initialized. To ensure memory consistency, tasks ensure that the effect of a partial task execution is not visible to a subsequent re-execution. Specifically, data that are read then written (i.e., a WAR dependence) may expose the result of an interrupted task. Task-based systems avoid "the WAR problem" with redo-logging [151] and static data duplication [47].

Task-based systems guarantee correct execution, but at a significant run-time cost. Redo-logging and static duplication both increase memory and compute in proportion to the amount of data written. Transitioning from one task to the next takes time, so short tasks that transition frequently suffer poor performance. Long tasks better amortize transition costs, but re-execute more work after a power failure. Worse, a task that is too long faces *non-termination* if the energy it requires exceeds the energy that the device can buffer. The programmer, therefore, needs to be careful in splitting a program into atomic tasks.

#### 2.1.3 COTS ULP Devices

In addition to being energy-constrained, ULP sensor devices are also severely resource constrained. ARM's Cortex M0 [1] or TI's MSP430 [110] are the most commonly used processors in existing ULP sensor systems [49,100,102,103,206,230]. Such MCUs' frequency is typically 1–16MHz, leaving a substantial performance gap compared to, e.g. a full-fledged, 2GHz Xeon-based system. The MCU usually also houses all the memory available to the system, including embedded SRAM, which is volatile, and embedded non-volatile memory (e.g. FRAM). Embedded memories are small and capacity varies by device. A typical MSP430 low-power MCU includes just 1–4KB of SRAM and 32–256KB of FRAM. While continuously powered (i.e., wired) embedded systems may interface with larger memories via a serial bus ( $I^2C$  or SPI), most ULP sensor devices do not due to their high access energy and latency. The typical operating power of an COTS ULP device is around 3–5mW.

#### Architecture

COTS ULP devices achieve ULP operation by being simple. They have an 3 to 5 stage, in-order scalar core, which may lack instruction and/or data caches. Some MCUs also come with a vector co-processor such as TI's Low Energy Accelerator (LEA) [111] or support for vector extensions like Arm's Neon [17] vector ISA. Additionally, some MCUs also include DMA engines and accelerators for tasks like AES encryption [110]. Despite these additional features, the energy consumption of the scalar core (and it's memory accesses) dominates total MCU energy. This is because the scalar execution model pays a high price for general-purpose programmability, constantly refetching and redecoding the same instructions and communicating intermediates via a centralized register file. The purpose of this thesis is to reduce this tax for general-purpose programmability. Chapters Ch. 4, Ch. 5, and Ch. 6 propose new computer architectures that maximize efficiency while maintaining a high-degree of programmability.

#### 2.2. EDGE INFERENCE

As ULP sensor devices become pervasive they will increasingly need to make intelligent decisions. Deep neural network (DNN) inference is the state-of-the-art approach for such intelligence. They are the standard for applications ranging from understanding speech to image recognition [129,215,223]. With their accuracy, however, comes a high computational cost. Neural networks require millions or billions of parameters and operations. This makes deploying neural networks onto resource-constrained, energy-harvesting devices difficult. Fortunately there has been much work on reducing network footprint and improving the performance and energy-efficiency of inference.

#### 2.2.1 Algorithmic improvements to NN inference

Since DNNs are robust to noise, algorithmic optimizations can be made that reduce NN memory footprint and increase inference performance without significantly impacting accuracy. Inference does not need full-precision floating point [66,95] and near-zero weights can often be "pruned" [29,96,168,171] without losing much accuracy. Layers can also be factored or split into several smaller, less-computationally intense layers [45,222,224]. Finally, networks can be redesigned [108,207,227] from the ground up to minimize storage and computation. These networks leverage smaller convolutional filters, but make up for accuracy degradation by being wider or deeper. This is worthwhile because there is a quadratic relationship between convolutional filter size (i.e., side length) and computational cost.

These algorithmic improvements sometimes come with modifications to the training regime to further increase accuracy. Networks can be fine-tuned during the final stages (final 20-30% of epochs) of training to adapt to algorithmic changes. During fine-tuning, the forward direction (i.e., inference) adopts the algorithmic change (e.g. reduced precision or pruning), while the backward direction remains the same. This allows the network to adjust its weights to the algorithmic change.

More exotic training regimes have also been explored to enforce additional properties to help inference performance. Binary networks [142] learn binary (-1, +1)weights that simplify multiplication to a single **and** operation. Structured sparsity can also be enforced [67, 171]. Pruning can lead to extremely sparse layers without much structure which can lead to irregular memory accesses. By enforcing structure on this sparsity during training, irregular memory accesses can be reduced.

Ch. 3 discusses the application of several algorithmic changes to compress neural networks to fit into device memory. It describes a tool, called GENESIS, that prunes, factors, and reduces the precision of neural networks, fine-tuning network weights to improve accuracy.

#### 2.2.2 Inference accelerators

The computer architecture community has also responded to the need for efficient DNN inference. Some architectures focus on dense computations [39–41], others on sparse computations [75, 95, 130, 257], and still others on CNN acceleration [14, 15, 73, 190, 201, 218]. Industry has followed this trend, embracing custom silicon for DNNs [117]. The key to the efficiency of these architectures is to maximize data reuse and optimize data movement. For example, Eyeriss [40] introduces row-stationary dataflow to maximize reuse on a spatial fabric, while MAERI [130] designs a new on-chip network specialized for several DNN dataflows (including hardto-accelerate LSTMs).

The circuits community has also responded, taping out extremely specialized accelerators with orders of magnitude higher energy-efficiency. These designs use low-level VLSI techniques (e.g. sub-threshold computing [78]), custom analog or mixed-signal circuits [27], or exploit emerging technologies (e.g. ReRAM crossbars [252, 253]) to achieve TOPS/W. Unfortunately this extreme energy efficiency comes at the expense of programmability (and perhaps reliability, in the case of analog circuits). In fact, some accelerators specialize to the particular NN architecture [27].

The work described in Ch. 4, Ch. 5, and Ch. 6 take a different approach and focus on entirely different power domain (mW v.  $\mu$ W). Energy-efficiency is achieved without sacrificing programmability. This makes these designs applicable to many different applications, future-proof to algorithmic developments, and reduces the upfront nonrecurring engineering cost.

#### 2.3. EFFICIENT PROGRAMMABLE ARCHITECTURES

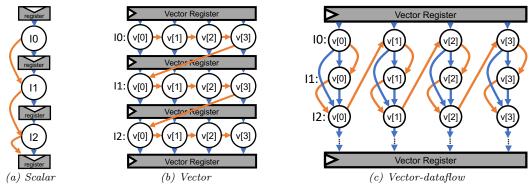

There is a long history of computer architectures that increase performance and/or improve energy-efficiency while maintaining programmability. Specifically, prior work on vector and dataflow architectures inform the work of this thesis and specifically MANIC, SNAFU, and RIPTIDE. These architectures exploit structure in the program (among data and control-flow) to change the execution model to reduce or even eliminate instruction and data supply energies without sacrificing general-purpose programmability.

#### 2.3.1 Vector architectures

Vector machines exploit data parallelism to amortize instruction supply energy (i.e., fetch, decode, and issue) across many operations. Early vector machines targeted super computing [55], but most commercially available architectures (e.g. AVX [79] and GPUs [53]) today support vectors. These vector designs target performance and operate at a power budget orders-of-magnitude higher than that contributed by this thesis. Nonetheless, all vector designs require large vector register files (VRF) exacerbating register file access cost, especially in designs that require a VRF with many ports. Thus, reducing VRF cost and complexity has been a primary focus of prior vector designs [18, 128].

T0 [18,246] is a vector architecture with reconfigurable pipelines. Software controls datapaths to chain operations, eliminating VRF access within a chain. However, microarchitectural details of the datapath are exposed to software, requiring major software changes and recompilation.

CODE [128] reduces VRF cost by distributing the VRF among heterogeneous functional units. This design is transparent to software because CODE renames operands at instruction issue to use registers near an appropriate functional unit. Distribution lets CODE reduce VRF ports, but requires a routing network to send values between functional units.

AVA [133] is a high-performance out-of-order vector processor that adapts the vector length and the number of vector registers stored in the VRF to the application. Some applications require long vectors, while others want moderate sizes. AVA trades additional vector length for fewer vector registers, spilling registers to memory as needed and then smartly pre-fetching them. Although AVA reduces energy and area, its primary goal is performance (by supporting variable-sized vector lengths).

Finally, there has been much work on reducing the cost and improving the scalability of GPU register files. This includes virtualizing the RF [115, 238] so that physical registers can be shared, compressing registers [139] to maximize utilization of the physical RF, and coalescing RF reads and writes [19] to minimize RF accesses. Relative to the large (100s of KB), many-ported (32+ ports) register files of GPUs, these optimizations require minimal additional hardware, but do not scale to ULP domain where energy efficiency is higher priority than performance.

#### 2.3.2 Dataflow architectures

Dataflow architectures, like vector machines, also have a long history [68–70, 177] that includes changes to the programming and execution model to eliminate control and data movement overheads. In particular, dataflow is prevalent today as part out-of-order (OoO) execution engines, where restricted dataflow improves performance and reduces RF pressure [20, 33, 124, 210, 212]. However, pure dataflow architectures have not found the same commercial success, but spatial-dataflow architectures still show great promise for improving energy efficiency and performance.

Dennis proposed the first dataflow architecture in 1975, introducing a small set of primitives to implement arbitrary control-flow by conditionally routing values to consumers [70]. In 1990, the MIT tagged-token dataflow machine showed how to practically implement dataflow in hardware [178]. The design relies on the use of a domain-specific language, called Id [176], to describe program dataflow and cap resource use to avoid resource-based deadlocks from unbounded parallelism [188].

Later, Wavescalar [221] and Trips [208] identified dataflow locality as the key determinant of sequential code performance. Wavescalar compiles C/C++ programs to WaveCache, a grid of simple compute units and memory that co-locates computation with data. Wavescalar handles arbitrary control-flow by tagging data (to distinguish instances of a value across loop iterations) and enforcing memory ordering by converting memory dependences to data dependences during compilation. Despite preserving dataflow locality, Wavescalar was not designed to minimize energy — the architecture relies on expensive tag-token matching and still fetches instructions, constantly reconfiguring compute pipelines.

Trips extracts hyperblocks (multiple basic blocks without backedges) from programs and executes these hyperblocks in dataflow-fashion across a mesh of processing elements. Trips heavily relies on speculation to increase performance; in-flight operations number in the hundreds or even thousands. This amount of speculation inevitably wastes energy by discarding mispeculated work. Further, Trips constantly reconfigures PE pipelines for each hyperblock, toggling control and data signals.

In contrast, ELM [23] is a dataflow architecture specifically designed for low-power, embedded operation. ELM uses restricted SIMD execution and operand forwarding to provide dataflow-like execution. ELM's complex register file hierarchy and forwarding mechanism are software-controlled, exposing microarchitectural details to the programmer and requiring significant changes to the compiler toolchain.

#### 2.4. COARSE-GRAIN RECONFIGURABLE ARRAYS

Since Wavescalar, Trips, and ELM there has been a resurgence of spatial-dataflow architectures, called coarse-grain reconfigurable arrays (CGRAs), because they offer better energy efficiency and performance with lower hardware complexity. A CGRA architecture [26, 44, 52, 60, 76, 86, 88, 119, 154, 161, 162, 164, 174, 175, 182, 189, 192, 198, 204, 209, 216, 225, 226, 240, 241, 247, 248] is a spatial array of processing elements (PEs) connected by an on-chip interconnect (NoC). A PE in a CGRA consumes inputs and produces outputs consumed by another PE, forming a pipeline corresponding to program dataflow. CGRA efficiency derives from avoiding control and data-movement overheads. A CGRA reduces instruction overheads by mapping operations to a PE, avoiding the need for instruction fetch and decode and simplifying control. A CGRA mitigates data movement overheads by avoiding large register files, instead moving operands through a NoC directly from producer PE to consumer PEs.

A wide variety of CGRA architectures target different domains. CGRAs exist as standalone cores [162, 208, 221, 242], co-processors [50, 51, 86, 90, 97, 154, 183, 225],

components of a processor pipeline [88, 137, 144] or memory hierarchy [146], or as coprocessors [52, 58–60, 174, 175, 182, 192, 198, 204, 216, 239, 240, 248, 251]. These contexts expose a wide range of hardware design choices, including PE operation set, PE complexity, and NoC topology. Further, PEs may be homogeneous or heterogeneous; the latter is more area- and energy-efficient, but creates a combinatorally large design space [26]. PEs typically include functional units for arithmetic, logic, and memory access, but can also include specialized functionality [58–60, 81, 204, 239, 247, 251]. Later chapters (Ch. 5 and Ch. 6) of this thesis will address CGRA design decisions in detail to maximize energy-efficiency.

#### 2.4.1 Types of CGRAs

CGRA designs can be categorized in four ways, as identified by [248]. They distiguished by how they schedule operations and whether PE resources are shared. Specifically the four types of CGRAs are: systolic (statically scheduled & dedicated PEs), shared-systolic (statically scheduled & PEs shared), tagged-dataflow (dynamically scheduled & PEs shared), and ordered-dataflow (dynamically scheduled & dedicated PEs).

Systolic: Systolic designs [52,86,162,182,193] rely on the compiler to schedule operations in space and time. These designs achieve high performance and energy-efficiency by eliminating dynamic control, but make compilation challenging. To maximize utilization, the compiler must reason about operation latencies, but these latencies might not be available at compilation time and might not be fixed (e.g. memory access latency depends on where data exists in the hierarchy). This limits the applications that can be mapped to these designs.

Shared-systolic: Shared-systolic designs [119, 154, 161, 164, 216] ([248] refers to these as "CGRAs") add additional layer of complexity to systolic designs. To maximize utilization of available hardware, the compiler generates schedules where operations can time-multiplex on the same PE resources. This makes scheduling even more challenging v. systolic designs.

**Tagged-dataflow:** Tagged-dataflow designs [177,189,208,221,240] dynamically schedule operations in time (and potentially in space) and time-multiplex PE resources. These designs tag data tokens and then match tags to distinguish between multiple instances of a single value, dynamically firing/enabling an operation when tags of inputs match. This tagging mechanism maximizes performance, allowing speculation and the re-ordering of operations and even entire loop iterations. However, this sort of dynamic tracking of values requires a high power budget (100s of mW v.  $\approx$ 1mW of ULP domain) and comes at a significant energy cost.

**Ordered-dataflow:** Ordered-dataflow designs [81, 88, 198] are the final category of CGRAs. They do not share PE resources and dynamically schedule operations in time, but disallow the re-ordering of tokens. This makes compilation easier (v. systolic and shared-systolic) since the compiler need not reason about operation latencies and is cheaper to implement in hardware (v. tagged-dataflow) since there is no need for tag matching (because tokens arrive in order). These benefits make ordered-dataflow a good choice for the ULP domain and are the reasons why SNAFU (Ch. 5) and RIPTIDE (Ch. 6) implement it.

#### 2.4.2 Low-power CGRAs

The CAD and circuit communities [62, 119, 123, 187] have also contributed lowpower CGRA designs. These designs are usually systolic or shared-systolic and operate at 10s of mW (still order of magnitude more than ULP domain). They use VLSI techniques to reduce power (e.g. low-voltage design, fine-grain clock/power gating) that are complementary to the CGRA designs (SNAFU and RIPTIDE) in this thesis. This thesis focuses on *architecture* that minimizes energy and maintains flexibility. In fact, Ch. 5 describes SNAFU, which has a goal of letting designers generate ULP CGRAs at reduced VLSI effort.

#### 2.4.3 Compilation

Compiling for CGRAs is challenging. Some architectures require domain-specific languages [126, 176], while others place constraints on the types of programs that can be compiled (i.e., no outer loops, or memory ordering is not enforced). This makes compilation tractable, but also limits the applications supported.

Compilation for CGRAs is similar to hardware synthesis. The compiler must find a layout of operations that fits within fabric resources with valid routes between all producers and consumers. In performance-focused CGRAs, the compiler must also reason about timing to maximize utilization and minimize initiation interval (minimum interval between subsequent loop iterations). With this vast search space, optimization-based methods often do not converge in a reasonable time [180, 185]. Most CGRA compilers use heuristics [26, 153, 180, 185, 191, 226, 245, 247] that can fail or produce poor mappings. Recent work proposed graph convolutional networks as a solution [160]. This thesis will (Ch. 5 and Ch. 6) describe integer-linear programming and SAT-based approaches to mapping a program to PE resources. Mapping is tractable because the compiler does not need to reason about timing or utilization for the proposed architectures (SNAFU and RIPTIDE).

#### Dataflow control-flow models

Compilation is also affected by the underlying control-flow model. There are three competing control-flow models for dataflow execution: predication, selection ( $\phi$ ), and steering ( $\phi^{-1}$ ). Each has benefits and drawbacks. Steering is the best choice for an energy-constrained context because it avoids routing values to the not-taken branch paths, but it can require extra routing by the compiler.

**Predication routes values unnecessarily:** Predication is popular, especially in GPU and vector architectures [79,99], converting conditional code to straightline code to simplify execution. In predication, only one side of a branch fully executes while the other side partially executes, passing through results from the enabled side to downstream consumers. Predication simplifies control flow in CGRAs because tokens arrive on every path, simplifying operand ordering. But predication has a performance and energy cost because values flow unnecessarily through the not-taken path. SNAFU (Ch. 5) uses predication for control flow, supporting simple, affine loops.

Selection ( $\phi$ ) burns energy on paths not taken: Selection executes both sides of a branch fully, sending results to a mux that chooses between results using the branch decider. Selection maximizes performance because the branch condition and each side of the branch execute speculatively in parallel. However, selection wastes energy by throwing away work.

Steering  $(\phi^{-1})$  is most energy efficient: Steering was proposed in the original dataflow paper [70] and has been used notably in a few dataflow architectures [34, 90, 162, 183, 221]. Steering routes values to only the taken path of a branch based on the branch's decider. Steering serializes execution of the taken path on the branch decider, but avoids executing any operations on the not-taken path. RIPTIDE (Ch. 6) implements steering to minimize energy, as steering never fires unneeded operations.

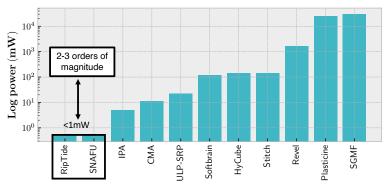

**Figure 2.2:** This thesis presents work (SNAFU and RIPTIDE) that targets the ULP domain, 2–3 orders of magnitude less than prior work.

|                                                     | Ultra-low-power CGRAs                                        |                                                               |                                                        | High-performance CGRAs              |                                  |                    |                                     |                                     |

|-----------------------------------------------------|--------------------------------------------------------------|---------------------------------------------------------------|--------------------------------------------------------|-------------------------------------|----------------------------------|--------------------|-------------------------------------|-------------------------------------|

|                                                     | SRP [123]                                                    | CMA [187]                                                     | IPA [62]                                               | HyCube [243]                        | Revel [248]                      | SGMF [240]         | Snafu [81]                          | RipTide [83]                        |

| Fabric size                                         | 3×3                                                          | 8×10                                                          | 4×4                                                    | 4×4                                 | $5 \times 5$                     | 8×8&<br>32 mem     | N×N (6×6<br>evaluated)              | N×N (6×6<br>evaluated)              |

| NoC                                                 | Neighbors<br>only                                            | Neighbors<br>only                                             | Neighbors<br>only                                      | Static,<br>bufferless,<br>multi-hop | Static &<br>dynamic<br>NoCs (2×) | Dynamic<br>routing | Static,<br>bufferless,<br>multi-hop | Static,<br>bufferless,<br>multi-hop |

| PE assignment                                       | Static                                                       | Static                                                        | Static                                                 | Static                              | Static or<br>dynamic             | Dynamic            | Static                              | Static                              |

| Time-share PEs?                                     | Yes                                                          | Yes                                                           | Yes                                                    | Yes                                 | Yes                              | Yes                | No                                  | No                                  |

| $\mathbf{Scheduling}/\mathbf{PE} \ \mathbf{firing}$ | Static                                                       | Static                                                        | Static                                                 | Static                              | Static or<br>dynamic             | Dynamic            | Dynamic                             | Dynamic                             |

| Heterogeneous PEs?                                  | No                                                           | No                                                            | No                                                     | No                                  | Yes                              | Yes                | Yes                                 | Yes                                 |

| Program support                                     | $\begin{array}{c} \rm VLIW/Simple\\ \rm loops^1 \end{array}$ | $\begin{array}{c} \rm VLIW/Simple \\ \rm loops^1 \end{array}$ | Simple $loops^1$                                       | Simple loops <sup>1</sup>           | Loops that fit<br>patterns       | Arbitrary          | Vectorizeable<br>loops              | Arbitrary                           |

| Power                                               | 22 mW                                                        | $11\mathrm{mW}$                                               | 3-5  mW                                                | 140 mW                              | $1.66\mathrm{W}$                 | $20\mathrm{W}$     | $<1\mathrm{mW}$                     | $<1\mathrm{mW}$                     |

| MOPS/mW (approx.)                                   | 30–100<br>MIPS/mW                                            | $_{\rm MIPS/mW}^{100-200}$                                    | $\begin{array}{c} 140 \\ \mathrm{MIPS/mW} \end{array}$ | 26 (system)                         | $\frac{12/16}{(fabric/system)}$  | _                  | 134/97<br>(fabric/system)           | 254/117<br>(fabric/system)          |

<sup>1</sup> Simple loops are singly-nested and have few loop-carried dependence.

Table 2.1: Architectural comparison of prior work to SNAFU and RIPTIDE.

#### 2.4.4 Compare & contrast different CGRA designs

Fig. 2.2 and Table 2.1 summarize the CGRA design space, comparing different CGRA designs to work of this thesis, SNAFU and RIPTIDE. In particular, the figures highlight what makes the ULP sensor domain different. Specifically, most prior CGRAs target much higher power domains (0.1-1W [119, 182, 225, 247, 248] or even up to 100 W [198, 240]), and their design decisions do not translate well to the ULP domain. The few CGRAs targeting ULP operation ( $\approx 1 \text{ mW}$ ) [62, 123, 187] are not flexible and leave energy savings on the table. They places restrictions on programs, e.g., supporting only simple, single-nested loops.

In contrast, this thesis presents SNAFU and RIPTIDE, which are designed from the ground-up to minimize energy (even at the expense of area and performance) while maximizing flexibility. SNAFU and RIPTIDE, like DSAGEN [247], generate CGRAs, but instead of targeting performance, they target ULP operation. They minimize PE energy by statically assigning operations to specific PEs and, unlike prior low-power CGRAs [62,119,123,187,225], minimize switching by not sharing PEs between operations. Likewise, to minimize NoC energy, SNAFU & RIPTIDE implement a statically configured, bufferless, multi-hop NoC, similar to HyCube [119]. This NoC is a contrast with prior ULP CGRAs [62, 123, 187] that restrict communication to a PE's immediate neighbors. Unlike many prior CGRAs that are statically scheduled, SNAFU & RIPTIDE implement dynamic dataflow firing to support variable latency FUs. Dynamic dataflow firing is essential to SNAFU & RIPTIDE's flexibility and ability to support arbitrary, heterogeneous PEs in a single fabric. SNAFU & RIPTIDE avoid expensive tag-token matching [88, 198] by disallowing out-of-order execution, unlike high-performance designs [177, 189, 221, 240]. Lastly, RIPTIDE targets more than simple, vectorizable loops [62, 119, 123, 187], compiling programs directly from C and

supporting deeply-nested loops and irregular memory accesses. The end result is that SNAFU & RIPTIDE are flexible and general-purpose, while still achieving extremely low operating power and high energy-efficiency.

### Chapter 3

# SONIC: Deploying DNNs on intermittent embedded devices<sup>12</sup>

The maturation of energy-harvesting technology and the recent emergence of viable intermittent computing models creates the opportunity to build sophisticated batteryless systems with most of the computing, sensing, and communicating capabilities of existing battery-powered systems. Many future IoT applications require frequent decision making, e.g., when to trigger a battery-draining camera, and these decisions must be taken locally, as it is often impractically expensive to communicate with other devices. Future IoT applications will require *local* inference on raw sensor data, and their performance will be determined by inference accuracy. Using energy numbers from recent state-of-the-art systems, we show that such local inference can improve end-to-end application performance by  $480 \times$  or more.

Recently, deep neural networks (DNNs) [129, 215, 223] have made large strides in inference accuracy. DNNs enable sophisticated inference using limited, noisy inputs, relying on rich models learned from many examples. Unfortunately, while DNNs are much more accurate than traditional alternatives [89, 163], they are also more computationally demanding.

Typical neural networks use tens of millions of weights and require billions of compute operations [129,215,223]. These networks target high-powered, throughput-optimized processors like GPUs or Google's TPU, which executes up to 9 trillion operations per second while drawing around 40 watts of power [117]. Even a small DNN (e.g., LeNet [134]) has over a million weights and millions of operations. The most efficient DNN accelerators optimize for performance as well as energy efficiency and consume hundreds of mW [39,40,75,95].

**Challenges:** In stark contrast to these high-performance systems, energy-harvesting devices use simple microcontrollers (MCUs) built for extreme low-power operation. DNN inference on these devices is unexplored, and several challenges must be overcome to enable emerging IoT applications on energy-harvesting systems built from commodity components. Most importantly, energy-harvesting systems operate *intermittently* as power becomes available, complicating the development of efficient, correct software. The operating period depends on the properties of the power system, but is short—typically around 100,000 instructions. As a result, *existing DNN inference implementations do not tolerate intermittent operation*.

Recent work proposed software systems that guarantee correct execution on intermittent power for arbitrary programs [47, 104, 105, 148, 151, 235]. These systems add significant runtime overheads to ensure correctness, slowing down DNN inference by

<sup>&</sup>lt;sup>1</sup>[82] G. Gobieski, N. Beckmann, and B. Lucia, "Intermittent deep neural network inference," in SysML, 2018.

$<sup>^2[84]</sup>$  G. Gobieski, B. Lucia, and N. Beckmann, "Intelligence beyond the edge: Inference on intermittent embedded systems," in ASPLOS, 2019.

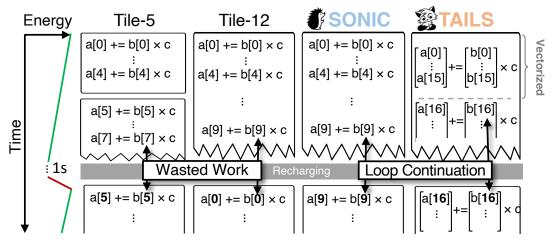

on average  $10 \times$  in our experiments. What these systems have missed is the opportunity to *exploit the structure of the computation to lower the cost of guaranteeing correctness.* This missed opportunity is especially costly for highly structured and loop-heavy computations like DNN inference.

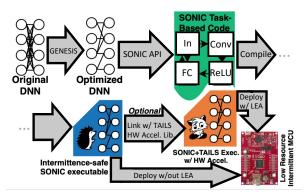

**Our approach and contributions:** We present the first demonstration of intermittent DNN inference on real-world neural networks running on a widely available energy-harvesting system. We make the following contributions:

- We first analyze where energy is spent in an energy-harvesting system and show that inference accuracy largely determines IoT application performance (Sec. 3.1). This motivates using DNNs despite their added cost over simpler but less accurate inference techniques.

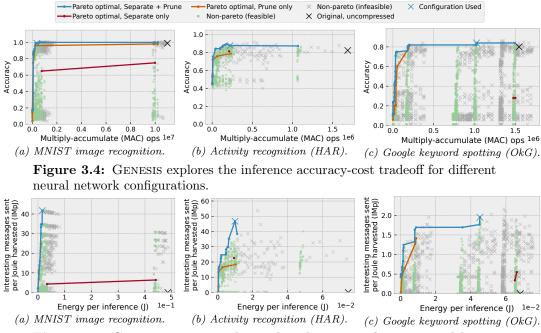

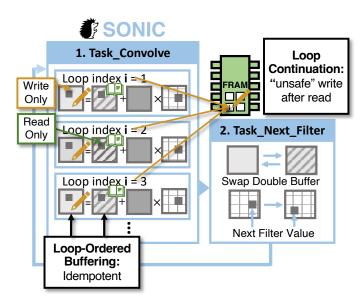

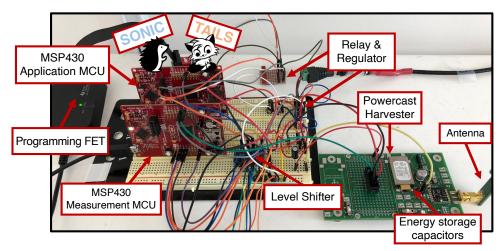

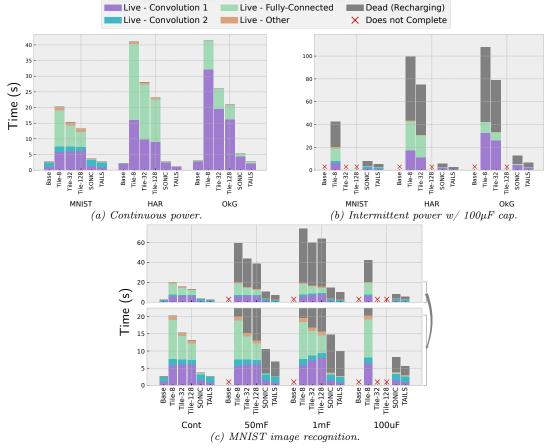

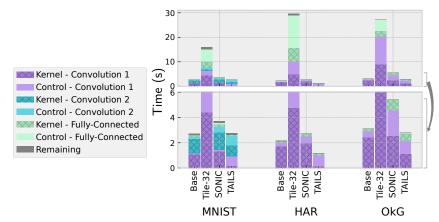

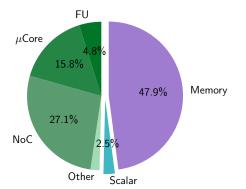

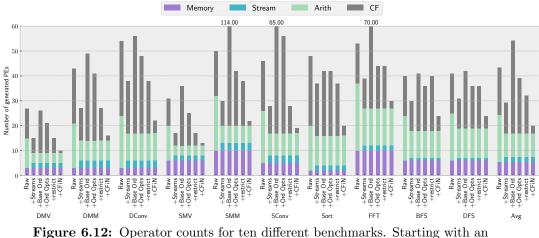

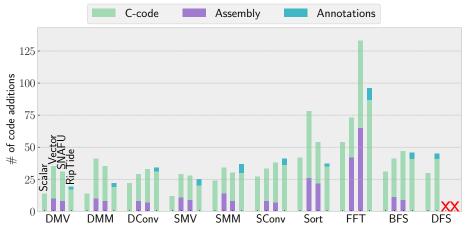

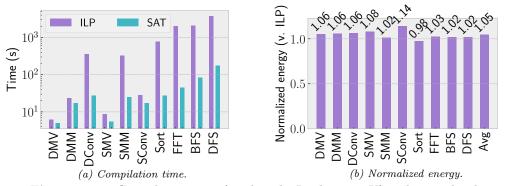

- Building on this analysis, we present GENESIS, a tool that automatically compresses networks to maximize IoT application performance (Sec. 3.3). GENESIS uses known compression techniques [29, 45, 96, 168]; our contribution is that GENESIS optimally balances inference energy v. accuracy.