## **Hardware Support for Thread-Level Speculation**

J. Gregory Steffan

CMU-CS-03-122

April 2003

School of Computer Science Computer Science Department Carnegie Mellon University Pittsburgh, PA 15213

#### **Thesis Committee:**

Todd C. Mowry, Chair Seth C. Goldstein David O'Hallaron Joel Emer, Intel

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Copyright © 2003 J. Gregory Steffan

This research was sponsored by the National Aeronautics and Space Administration (NASA) under grant nos. NAG2-1230 and NAG2-6054, and by a generous donation from the Intel Corporation. The views and conclusions contained herein are those of the author and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of any sponsoring party or the U.S. Government.

**Keywords:** thread-level speculation, chip-multiprocessing, automatic parallelization, distributed computing, cache coherence, value prediction, dynamic synchronization, instruction prioritization.

## **Abstract**

Novel architectures that support multithreading, for example *chip multiprocessors*, have become increasingly commonplace over the past decade: examples include the Sun MAJC, IBM Power4, Alpha 21464, and Intel Xeon, HP PA-8800. However, only workloads composed of independent threads can take advantage of these processors—to improve the performance of a single application, that application must be transformed into a *parallel* version. Unfortunately the process of parallelization is extremely difficult: the compiler must prove that potential threads are independent, which is not possible for many *general-purpose programs* (e.g., spreadsheets, web software, graphics codes, etc.) due to their abundant use of pointers, complex control flow, and complex data structures. This dissertation investigates hardware support for *Thread-Level Speculation* (TLS), a technique which empowers the compiler to optimistically create parallel threads despite uncertainty as to whether those threads are actually independent.

The basic idea behind the approach to thread-level speculation investigated in this dissertation is as follows. First, the compiler uses its global knowledge of control flow to decide how to break a program into speculative threads as well as transform and optimize the code for speculative execution; new architected instructions serve as the interface between software and hardware to manage this new form of parallel processing. Hardware support performs the run-time tasks of tracking data dependences between speculative threads, buffering speculative state from the regular memory system, and recovering from failed speculation. The hardware support for TLS presented in this dissertation is unique because it scales seamlessly both within and beyond chip boundaries—allowing this single unified design to apply to a wide variety of multithreaded processors and larger systems that use those processors as building blocks. Overall, this cooperative and unified approach has many advantages over previous approaches that focus on a specific scale of underlying architecture, or use either software or hardware in isolation.

This dissertation: (i) defines the roles of compiler and hardware support for TLS, as well as the interface be-

tween them; (ii) presents the design and evaluation of a unified mechanism for supporting thread-level speculation which can handle arbitrary memory access patterns and which is appropriate for any scale of architecture with parallel threads; (iii) provides a comprehensive evaluation of techniques for enhancing value communication between speculative threads, and quantifies the impact of compiler optimization on these techniques. All proposed mechanisms and techniques are evaluated in detail using a fully-automatic, feedback-directed compilation infrastructure and a realistic simulation platform. For the regions of code that are speculatively parallelized by the compiler and executed on the baseline hardware support, the performance of two of 15 general-purpose applications studied improves by more than twofold and nine others by more than 25%, and the performance of four of the six numeric applications studied improves by more than twofold, and the other two by more than 60%—confirming TLS as a promising way to exploit the naturally-multithreaded processing resources of future computer systems.

## Acknowledgements

Flinn, Ted Wong, and Kip Walker.

As I reflect over the past five years, I realize how numerous are the people that I must thank for contributing to this work in many ways. I am indebted to my advisor, Todd Mowry, for the quality of my graduate career. His wisdom and optimism guided me through two graduate schools and degrees, while teaching me how to do good research and share it with the world. I am also grateful to Todd for arranging two enlightening internships, for his commitment to my professional development, and for his friendship. I also thank the members of my thesis committee, Joel Emer, David O'Hallaron, and Seth Goldstein, for their contributions to this dissertation and for steering it to successful completion. This work would not have been possible without the efforts of others. I'd like to express my sincere gratitude to Chris Colohan and Antonia Zhai for building and tuning the compiler infrastructure used in this dissertation, and for years of enjoyable collaboration, advice, and companionship. I also thank the rest of the STAMPede'rs for listening to practice talks, being an effective sounding board for new ideas, and for their support—technical and otherwise. For

I am quite fortunate to have worked with two phenomenal groups of people in industry. Earl Killian and the architecture groups at MIPS (a division of SGI at the time) provided me with an introduction to computer architecture in the real world, and Joel Emer and the VSSAD architecture group (DEC—Compaq—Intel) helped develop initial support for TLS in a shared cache, and also demonstrated how to mix research and fun; all have my sincere gratitude.

making my days at CMU memorable (whether working or not) I thank Angela Demke-Brown, Chris Palmer, Jason

There are also many people from whom I have benefited beyond academics. I thank Joe, Carrie, Addie, John, and Pete for much needed relief from computers during my stay in Pittsburgh. Since leaving the University of Toronto, Derek, Dan, Rob, Alex, Steve, Chris F., Masis, Stan, Sergio, and Aryn showed continued friendship and thoughtfulness. For their constant support, endless creativity, and mostly for keeping life interesting, I deeply thank my friends

Alana, Angela S., Champ, Chris B., Chris E., Eastman, Fiona, Jake, Jason, Kathy, Katie, Kev C., Kev H., Laurel, Liisa, Lucky, Mark, Maya, Mayte, Natalie, Rick, Rose, Ryan, Scooter, Scott, Stacey, Tim, and Tyler.

My time in graduate school would not have been possible without the support of family. I thank my parents-in-law Hans and Lea Schwarzbauer as well as my sister-in-law Dawn for many years of warmth and understanding. I also thank my parents Sac and Susan Steffan and my brother Ryan for providing constant encouragement, and helping me to remember what is truly important. Finally, I thank my wife Nancy who through infinite patience and unconditional love has given me the confidence to rise to many challenges.

## **Contents**

| 1 | Intr | roduction                           | 1  |

|---|------|-------------------------------------|----|

|   | 1.1  | Example                             | 2  |

|   | 1.2  | Related Work                        | 3  |

|   |      | 1.2.1 Loosely-Related Work          | 3  |

|   |      | 1.2.2 Prior Related Work            | 4  |

|   |      | 1.2.3 Concurrent Related Work       | 6  |

|   | 1.3  | Research Goals                      | 7  |

|   | 1.4  | Overview                            | 8  |

| 2 | Thre | ead-Level Speculation               | 9  |

|   | 2.1  | Introduction                        | 9  |

|   | 2.2  | Execution Model                     | 9  |

|   | 2.3  | Software Interface                  | 11 |

|   |      | 2.3.1 Required Interface Mechanisms | 11 |

|   |      | 2.3.2 TLS Instructions              | 17 |

|   |      | 2.3.3 Examples                      | 18 |

|   | 2.4  | Compiler Support                    | 22 |

|   | 2.5  | Experimental Framework              | 24 |

|   |      | 2.5.1 Benchmarks                    | 24 |

|   |      | 2.5.2 Simulation Models             | 32 |

|   | 2.6 | Potent   | ial Performance                                         | 34 |

|---|-----|----------|---------------------------------------------------------|----|

|   | 2.7 | Summ     | ary                                                     | 35 |

| 3 | Sup | port for | Thread-Level Speculation in a Chip-Multiprocessor       | 36 |

|   | 3.1 | Introdu  | action                                                  | 36 |

|   |     | 3.1.1    | An Example                                              | 37 |

|   |     | 3.1.2    | Potential Performance                                   | 38 |

|   |     | 3.1.3    | Related Work                                            | 41 |

|   |     | 3.1.4    | Overview                                                | 42 |

|   | 3.2 | Cohere   | ence Scheme For Scalable TLS                            | 43 |

|   |     | 3.2.1    | Underlying Architecture                                 | 43 |

|   |     | 3.2.2    | Overview of Our Scheme                                  | 43 |

|   |     | 3.2.3    | Cache Line States                                       | 45 |

|   |     | 3.2.4    | Coherence Messages                                      | 45 |

|   |     | 3.2.5    | Baseline Coherence Scheme                               | 46 |

|   | 3.3 | Impler   | nentation                                               | 49 |

|   |     | 3.3.1    | Epoch Numbers                                           | 49 |

|   |     | 3.3.2    | Implementation of Speculative State                     | 49 |

|   |     | 3.3.3    | Preserving Correctness                                  | 50 |

|   |     | 3.3.4    | Allowing Multiple Writers                               | 52 |

|   | 3.4 | Evalua   | ation of Baseline Hardware Support                      | 53 |

|   |     | 3.4.1    | Performance of the Baseline Scheme                      | 53 |

|   |     | 3.4.2    | Overheads of Thread-Level Speculation                   | 58 |

|   | 3.5 | Tuning   | g the Coherence Scheme                                  | 61 |

|   |     | 3.5.1    | Support for Multiple Writers                            | 61 |

|   |     | 3.5.2    | Speculative Coherence without Speculative Messages      | 64 |

|   |     | 3.5.3    | Speculative Invalidation of Non-Speculative Cache Lines | 65 |

|   | <b>5</b> 1 | Interedu | ration                                               | 110 |

|---|------------|----------|------------------------------------------------------|-----|

| 5 | Imp        | roving \ | Value Communication                                  | 110 |

|   | 4.4        | Chapte   | er Summary                                           | 108 |

|   |            | 4.3.4    | Impact of Page Layout                                | 106 |

|   |            | 4.3.3    | Sensitivity to Inter-Node Communication Latency      | 105 |

|   |            | 4.3.2    | Scaling Up to Multi-Node Architectures               | 103 |

|   |            | 4.3.1    | Performance of Floating Point Benchmark Applications | 102 |

|   | 4.3        | Scaling  | g Beyond Chip Boundaries                             | 102 |

|   |            | 4.2.4    | Impact of Increasing Associativity                   | 100 |

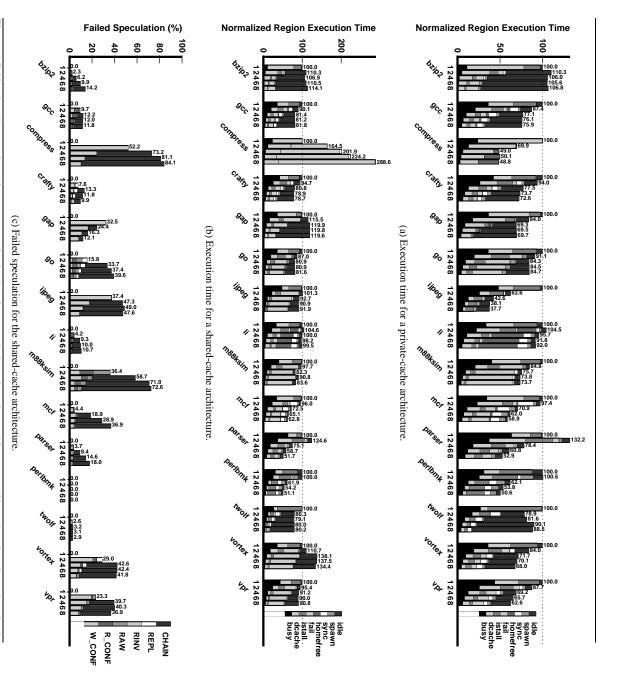

|   |            | 4.2.3    | Tolerating Read and Write Conflicts                  | 97  |

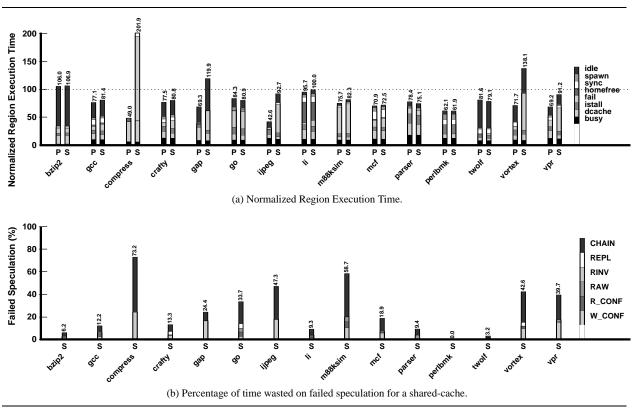

|   |            | 4.2.2    | Performance of Shared Data Cache Support for TLS     | 93  |

|   |            | 4.2.1    | Implementation                                       | 90  |

|   | 4.2        | Suppor   | rt for a Shared Data Cache                           | 90  |

|   | 4.1        | Introdu  | action                                               | 89  |

| 4 | Supp       | port for | Scalable Thread-Level Speculation                    | 89  |

|   | 3.8        | Chapte   | r Summary                                            | 87  |

|   |            | 3.7.5    | Implementation of the Homefree Token                 | 87  |

|   |            | 3.7.4    | Handling Violations                                  | 83  |

|   |            | 3.7.3    | Implementing the Forwarding Frame                    | 81  |

|   |            | 3.7.2    | Snoopy, Write-Through Coherence                      | 80  |

|   |            | 3.7.1    | Less Aggressive Designs                              | 78  |

|   | 3.7        | Implen   | nentation Alternatives                               | 76  |

|   |            | 3.6.3    | Reorder Buffer Size and Complexity                   | 71  |

|   |            | 3.6.2    | Memory System                                        | 69  |

|   |            | 3.6.1    | Inter-Processor Communication Latencies              | 66  |

|   | 3.6        | Sensiti  | vity to Architectural Parameters                     | 66  |

|   |     | 5.1.1    | The Importance of Value Communication for Thread-Level Speculation                 | 110 |

|---|-----|----------|------------------------------------------------------------------------------------|-----|

|   |     | 5.1.2    | Techniques for Improving Value Communication                                       | 112 |

|   | 5.2 | A Clos   | ser Look at Improving Value Communication                                          | 114 |

|   |     | 5.2.1    | Impact of Compiler Optimization                                                    | 114 |

|   |     | 5.2.2    | Importance of Issuing Around Wait Instructions                                     | 115 |

|   |     | 5.2.3    | The Potential for Further Improvement by Hardware                                  | 117 |

|   | 5.3 | Techni   | ques for When Prediction Is Best                                                   | 118 |

|   |     | 5.3.1    | Related Work                                                                       | 118 |

|   |     | 5.3.2    | Design Issues and Experimental Framework                                           | 119 |

|   |     | 5.3.3    | Memory Value Prediction                                                            | 119 |

|   |     | 5.3.4    | Prediction of Forwarded Values                                                     | 123 |

|   |     | 5.3.5    | Silent Stores                                                                      | 126 |

|   | 5.4 | Techni   | ques for When Synchronization Is Best                                              | 127 |

|   |     | 5.4.1    | Hardware-Inserted Dynamic Synchronization                                          | 128 |

|   |     | 5.4.2    | Prioritizing the Critical Forwarding Path                                          | 130 |

|   | 5.5 | Combi    | ning the Techniques                                                                | 133 |

|   | 5.6 | Chapte   | er Summary                                                                         | 135 |

| 5 | Con | clusions | ·                                                                                  | 137 |

| , |     |          |                                                                                    |     |

|   | 6.1 |          | butions                                                                            |     |

|   |     | 6.1.1    | A Cooperative Approach to TLS                                                      | 138 |

|   |     | 6.1.2    | Unified Hardware Support for TLS                                                   | 138 |

|   |     | 6.1.3    | A Comprehensive Evaluation of Techniques for Improving Value Communication Between |     |

|   |     |          | Speculative Threads                                                                | 138 |

|   | 6.2 | Future   | Work                                                                               | 139 |

|   |     | 6.2.1    | Compiler Support                                                                   | 139 |

|   |     | 6.2.2    | Hardware Support for Improving Cache Locality                                      | 141 |

|   |      | 6.2.3 Online Feedback and Dynamic Adaptation | 141 |

|---|------|----------------------------------------------|-----|

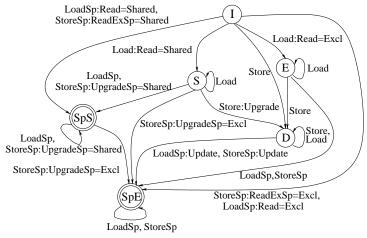

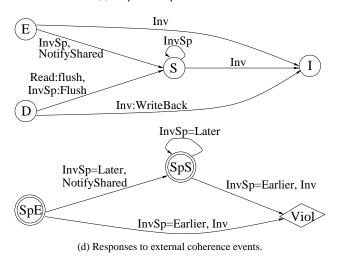

| A | Full | Coherence Scheme                             | 142 |

|   | A.1  | Line State in the Cache                      | 142 |

|   | A.2  | Processor Actions                            | 144 |

|   | A.3  | Cache Actions                                | 145 |

|   | A.4  | Other Actions                                | 148 |

|   | A.5  | State Transition Diagram                     | 149 |

|   | A 6  | Coherence in the External Memory System      | 152 |

# **List of Figures**

| 1.1  | Example of thread-level speculation (TLS)                                                                   | 2  |

|------|-------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Glossary of terms                                                                                           | 10 |

| 2.2  | TLS execution model                                                                                         | 10 |

| 2.3  | Speculative parallelization of a simple loop                                                                | 12 |

| 2.4  | Interface for cancelling superfluous epochs                                                                 | 13 |

| 2.5  | Interface for passing the homefree token                                                                    | 14 |

| 2.6  | TLS instructions for thread and stack management                                                            | 15 |

| 2.7  | TLS instructions for speculation management                                                                 | 16 |

| 2.8  | TLS instructions for value forwarding                                                                       | 16 |

| 2.9  | Threads in a basic for loop                                                                                 | 18 |

| 2.10 | Threads in a for loop with an unknown ending condition                                                      | 19 |

| 2.11 | A loop that re-uses threads                                                                                 | 20 |

| 2.12 | A loop requiring forwarding                                                                                 | 21 |

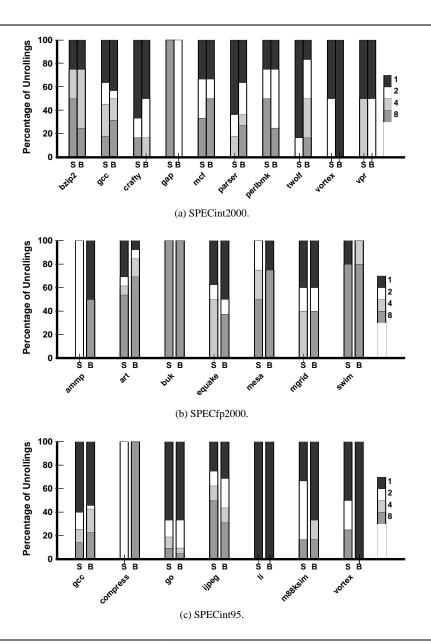

| 2.13 | Breakdown of unrollings used in the $select$ benchmarks. $S$ is the sequential version and $B$ is the       |    |

|      | baseline TLS version                                                                                        | 30 |

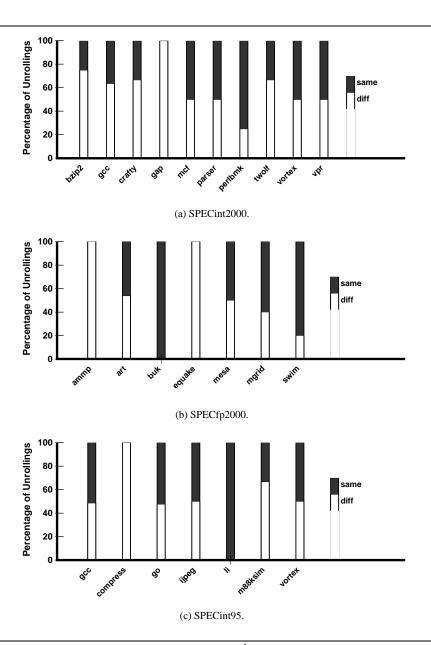

| 2.14 | Comparing the sequential and TLS versions of the <i>select</i> benchmarks, this graph shows the fraction of |    |

|      | the unrollings used that are the same or different.                                                         | 31 |

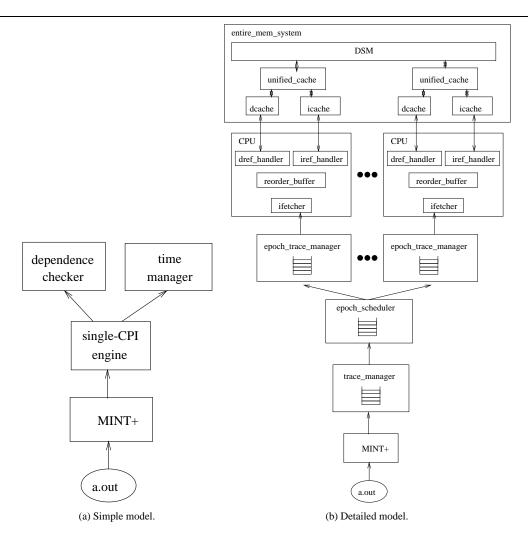

| 2 15 | Simulation Models                                                                                           | 32 |

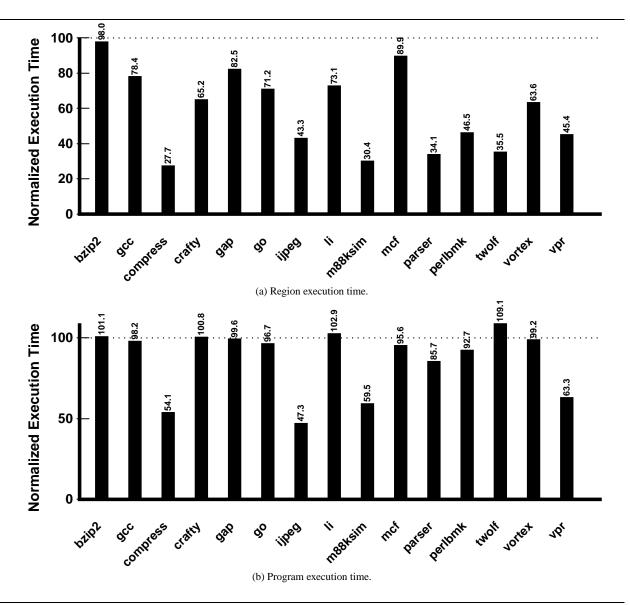

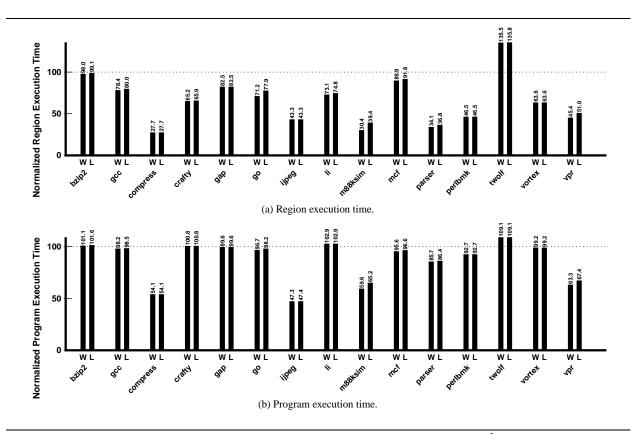

| 2.16 | Improvement in (a) region and (b) program execution time of the 1LS version of the select bench-             |    |

|------|--------------------------------------------------------------------------------------------------------------|----|

|      | marks, according to the simple simulator.                                                                    | 34 |

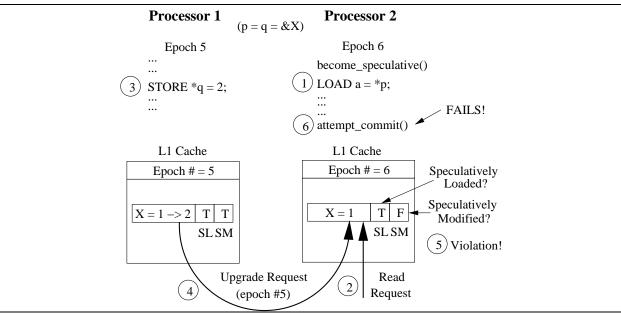

| 3.1  | Using cache coherence to detect a RAW dependence violation                                                   | 38 |

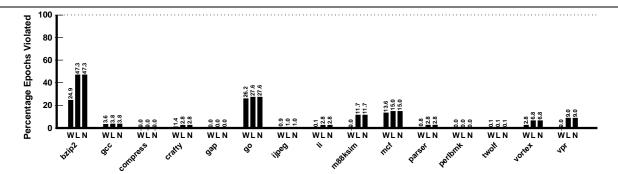

| 3.2  | Percentage of epochs that are violated. W tracks true dependences at a word granularity, L tracks true       |    |

|      | dependences at a cache line granularity, and $N$ builds on $L$ by dissallowing implicit forwarding           | 39 |

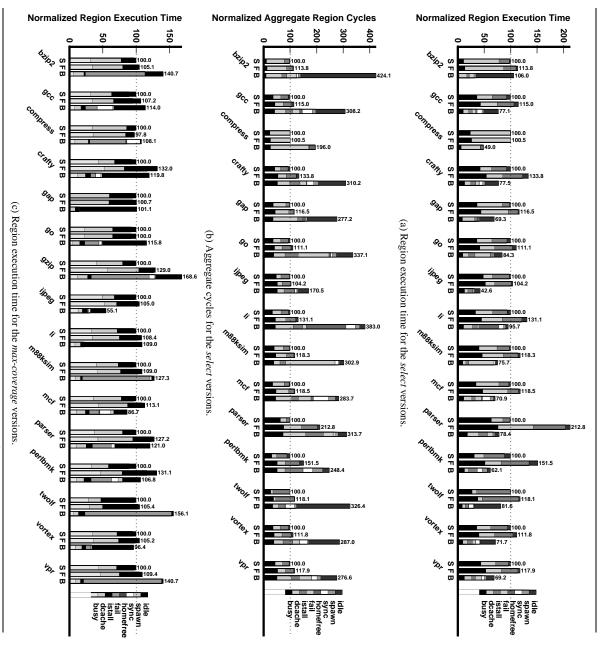

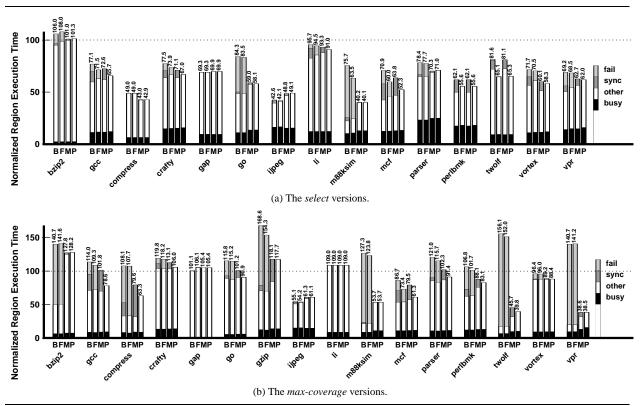

| 3.3  | Improvement in (a) region and (b) program execution time of the TLS version of the select bench-             |    |

|      | marks, according to the simple simulator— $W$ tracks dependences at a word granularity, $L$ tracks de-       |    |

|      | pendences at a cache line granularity                                                                        | 40 |

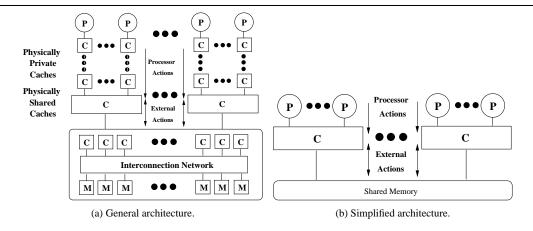

| 3.4  | Base architecture for the TLS coherence scheme.                                                              | 42 |

| 3.5  | Our coherence scheme for supporting thread-level speculation                                                 | 44 |

| 3.6  | Comparing Epoch Sequence Numbers                                                                             | 50 |

| 3.7  | Encoding of cache line states. In (b), X means "don't-care"                                                  | 51 |

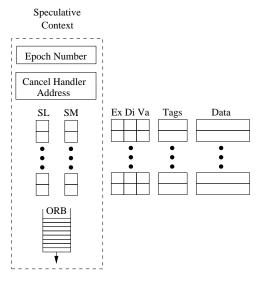

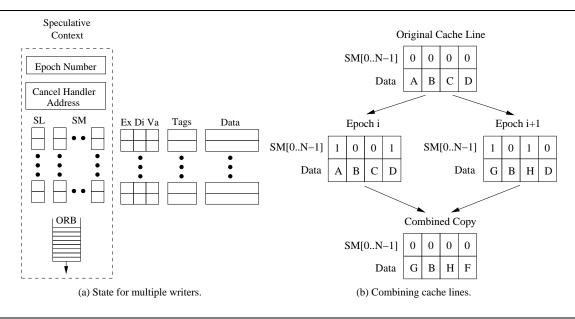

| 3.8  | Support for multiple writers                                                                                 | 52 |

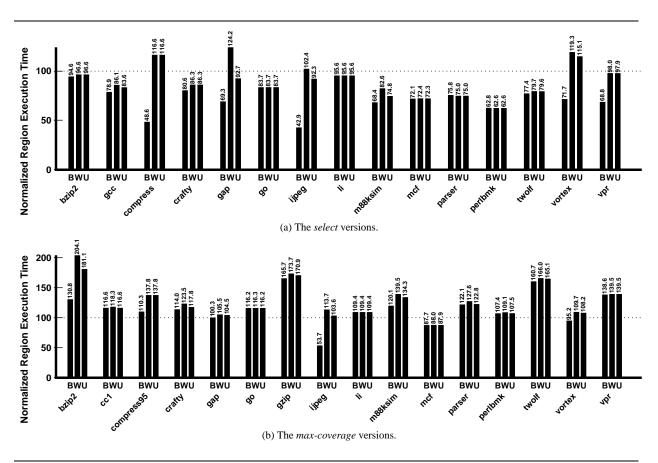

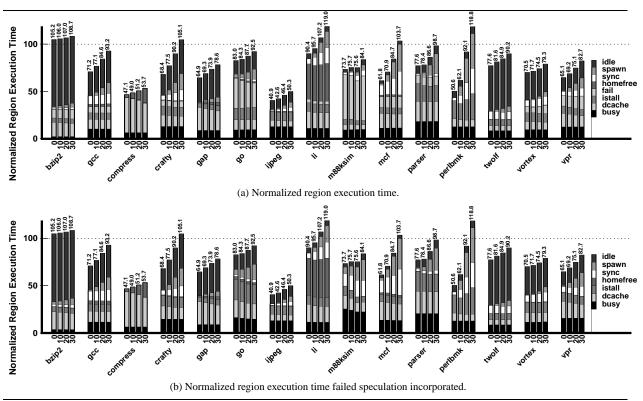

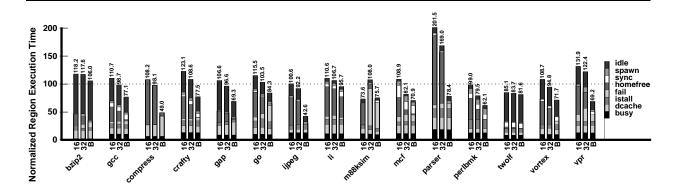

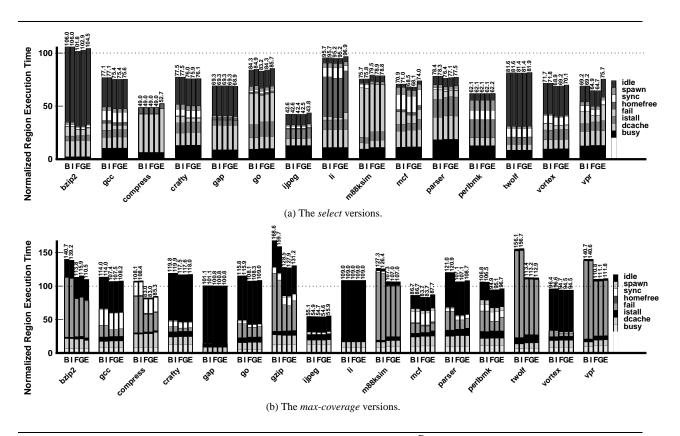

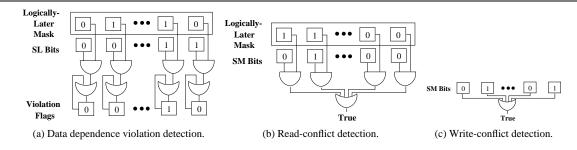

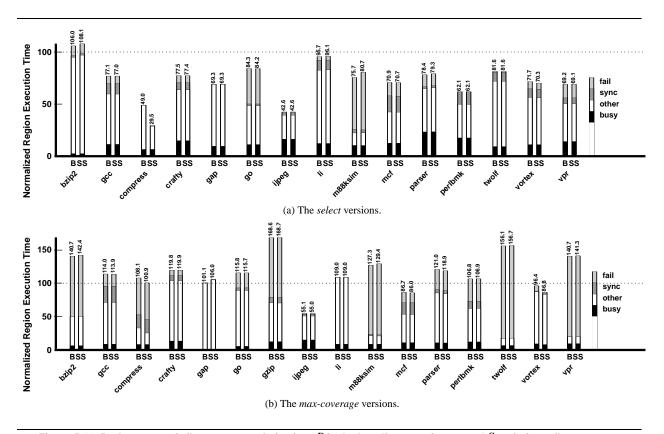

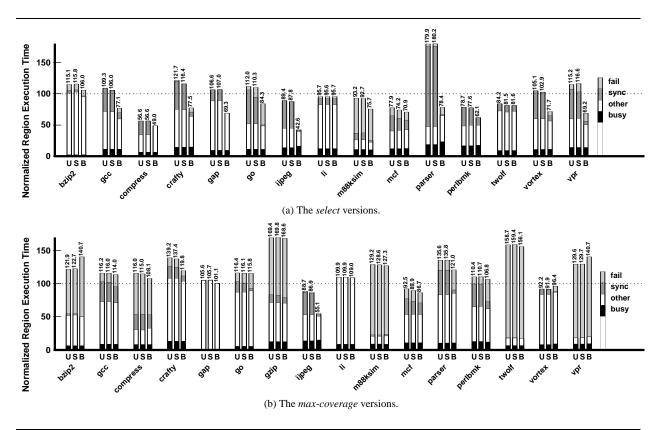

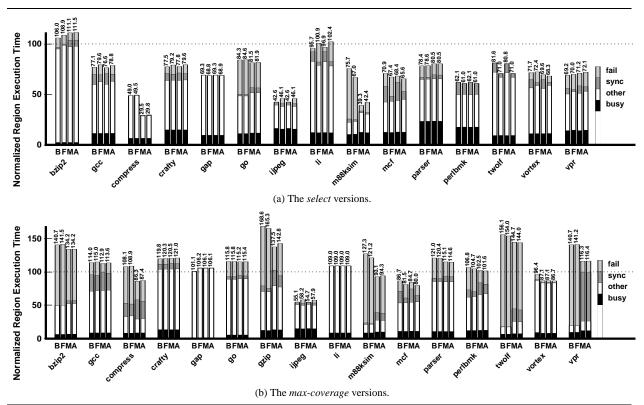

| 3.9  | Impact on region execution time of our baseline hardware support for TLS. S is the original sequential       |    |

|      | version, $F$ is the speculative version run sequentially, and $B$ is the speculative version run in parallel |    |

|      | on four processors                                                                                           | 55 |

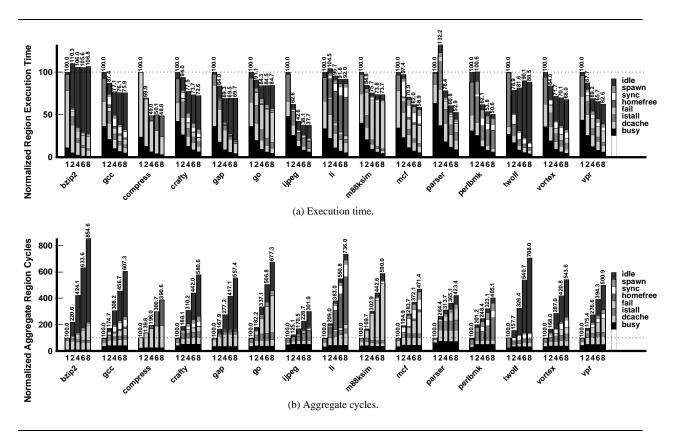

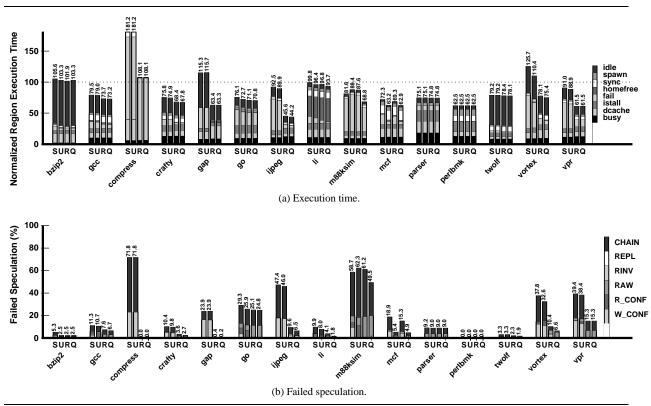

| 3.10 | Varying the number of processors from one through eight. The baseline architecture has four processors.      | 57 |

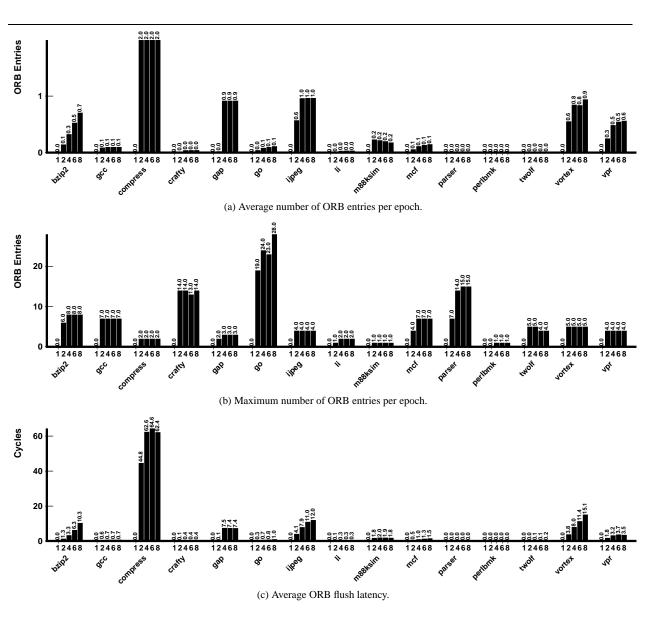

| 3.11 | Size and flush latency of the ownership required buffer (ORB), as we vary the number of processors           | 58 |

| 3.12 | Percentage of execution time wasted on failed speculation, and the breakdown of reasons for violations       |    |

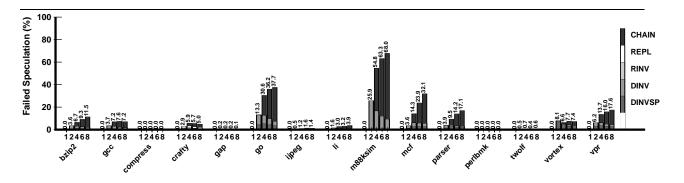

|      | as we vary the number of processors                                                                          | 60 |

| 3.13 | Percentage of misses where the cache line is resident in another first-level cache, which indicates the      |    |

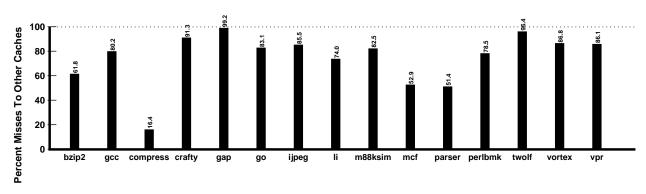

|      | impact of TLS execution on cache locality                                                                    | 61 |

| 3.14 | Impact of support for multiple writers. $W$ does not model support for multiple writers while $B$ (our       |    |

|      | baseline architecture) does                                                                                  | 62 |

| 3.15 | Impact of re-selecting unrollings when multiple-writers is not supported. <i>B</i> is our baseline (which does   |    |

|------|------------------------------------------------------------------------------------------------------------------|----|

|      | support multiple writers), $W$ and $U$ do not support multiple writers, and $U$ re-selects unrollings. Note      |    |

|      | that results may differ from Figure 3.14 since they are measured from benchmark versions where all               |    |

|      | loops and all unrollings have been speculatively parallelized                                                    | 63 |

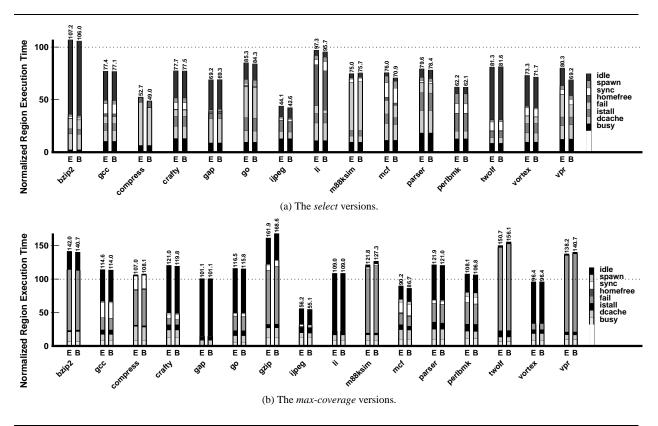

| 3.16 | Impact of support for speculative coherence messages. E has no speculative coherence messages while              |    |

|      | B (our baseline) does                                                                                            | 64 |

| 3.17 | Impact of speculative invalidation of non-speculative cache lines. $B$ (our baseline) models speculative         |    |

|      | invalidation of non-speculative cache lines while $D$ does not                                                   | 65 |

| 3.18 | Impact of various communication latencies on the <i>select</i> benchmarks. <i>B</i> is our baseline which models |    |

|      | 10 cycle interprocessor communication latency, $S$ modifies $B$ to have a zero-cycle spawn latency, $F$          |    |

|      | modifies $B$ to have a zero-cycle forwarding latency, $H$ modifies $B$ to pass the homefree token in zero        |    |

|      | cycles, and N has no interprocessor communication latency                                                        | 67 |

| 3.19 | Impact of varying communication latency (by tens of cycles)                                                      | 69 |

| 3.20 | Varying crossbar bandwidth from 8 to 32 bytes per cycle (for the <i>select</i> benchmarks). Note that our        |    |

|      | baseline architecture has a crossbar bandwidth of 8 bytes per cycle                                              | 70 |

| 3.21 | Varying the number of data reference handlers from 4 to 32 (for the <i>select</i> benchmarks). Note that our     |    |

|      | baseline architecture has 16 data reference handlers per processor.                                              | 72 |

| 3.22 | Varying data cache size from 8KB to 64KB (for the <i>select</i> benchmarks). Note that our baseline archi-       |    |

|      | tecture has a 32KB data cache per processor                                                                      | 73 |

| 3.23 | Varying data cache associativity from direct-mapped (1) to 2-way (for the <i>select</i> benchmarks). Note        |    |

|      | that our baseline architecture is 2-way set-associative                                                          | 74 |

| 3.24 | Impact of issuing memory references out-of-order. $I$ models an in-order-issue pipeline, and $B$ (our            |    |

|      | baseline) models an out-of-order-issue pipeline                                                                  | 75 |

| 3.25 | Impact of varying the reorder buffer size, from 64 to 256 entries. Note that our baseline architecture           |    |

|      | has a 128-entry reorder buffer                                                                                   | 77 |

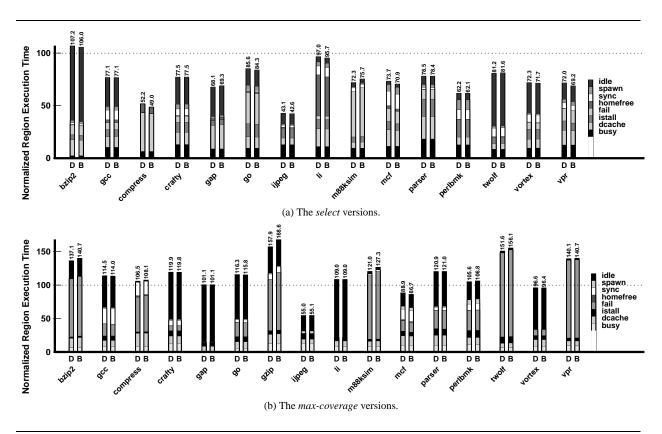

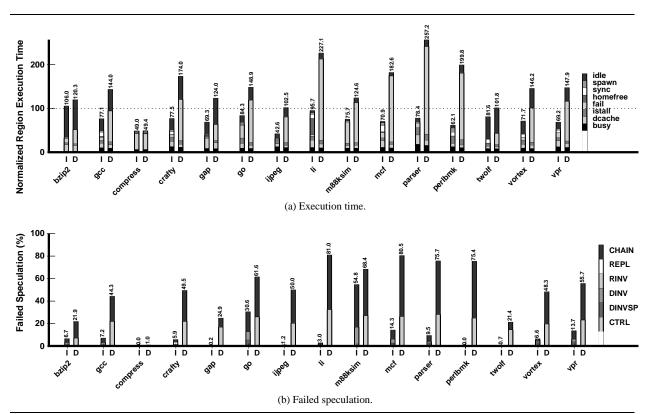

| 3.26 | Benefits of control independence. $I$ is control independent (our baseline) and $D$ is control dependent         | 79 |

| 3.27 | Comparison with hardware support that only uses the load/store queues as speculative buffers. 16                       |    |

|------|------------------------------------------------------------------------------------------------------------------------|----|

|      | models 16-entry load and store speculative buffers, 32 models 32-entry load and store speculative                      |    |

|      | buffers, and <i>B</i> is our baseline hardware support (using the first-level data caches as speculative buffers).     | 80 |

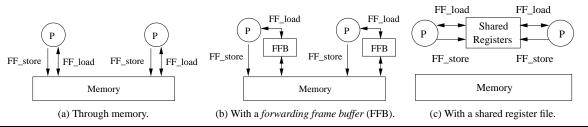

| 3.28 | Implementation alternatives for the forwarding frame, where forwarding frame loads (FF_load) and                       |    |

|      | stores (FF_store) are managed by different mechanisms                                                                  | 82 |

| 3.29 | Impact of special hardware support for the forwarding frame. For B, all forwarding frame references                    |    |

|      | are through regular memory (our baseline); for $F$ , forwarding frame references are first loaded from                 |    |

|      | regular memory but then saved in a <i>forwarding frame buffer</i> ; and for <i>R</i> , all forwarding frame references |    |

|      | are to a shared register file                                                                                          | 83 |

| 3.30 | Impact of support for avoiding any violation due to cache line replacement by immediately suspending                   |    |

|      | the offending epoch until it becomes homefree. $B$ is our baseline hardware support, and $S$ suspends                  |    |

|      | any epoch that attempts to replace a speculative cache line until it becomes homefree                                  | 84 |

| 3.31 | Impact of various violation notification and recovery strategies. <i>B</i> is our baseline strategy which polls        |    |

|      | for a violation at the end of an epoch, and squashed epochs re-spawn; <i>I</i> modifies <i>B</i> such that squashed    |    |

|      | epochs store their initial state and restart independently, without having to respawn; $F$ modifies $B$ such           |    |

|      | that violations are notified immediately by an interrupt; $G$ combines both $I$ and $F$ ; and $E$ modifies $G$         |    |

|      | by not having speculative coherence messages.                                                                          | 85 |

| 3.32 | Benefits of a hardware-visible homefree token. B (our baseline) models a software-only homefree                        |    |

|      | token, while $E$ models a hardware-visible homefree token                                                              | 87 |

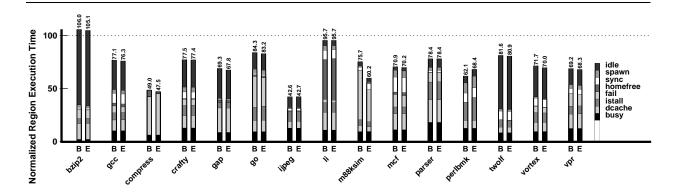

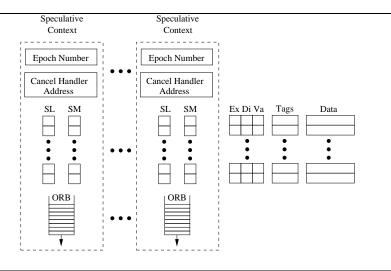

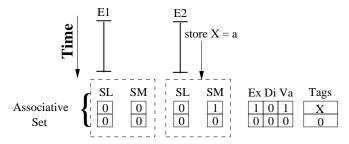

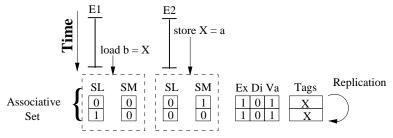

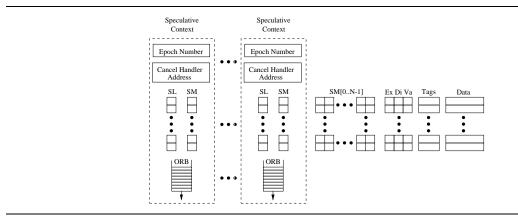

| 4.1  | Hardware support for multiple epoch contexts in a single cache                                                         | 90 |

| 4.2  | Support for efficient epoch number comparison                                                                          | 91 |

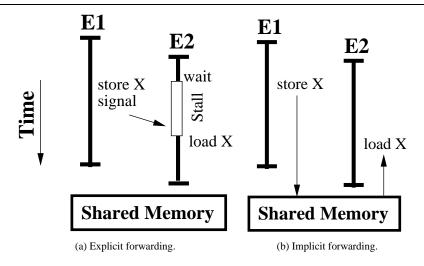

| 4.3  | Explicit vs implicit forwarding                                                                                        | 92 |

| 4.4  | Region performance of the <i>select</i> benchmarks on both private-cache and shared-cache architectures.               |    |

|      | P is speculatively executed on a 4-processor CMP with private caches, and S is speculatively executed                  |    |

|      | on a 4-processor CMP with a shared cache.                                                                              | 94 |

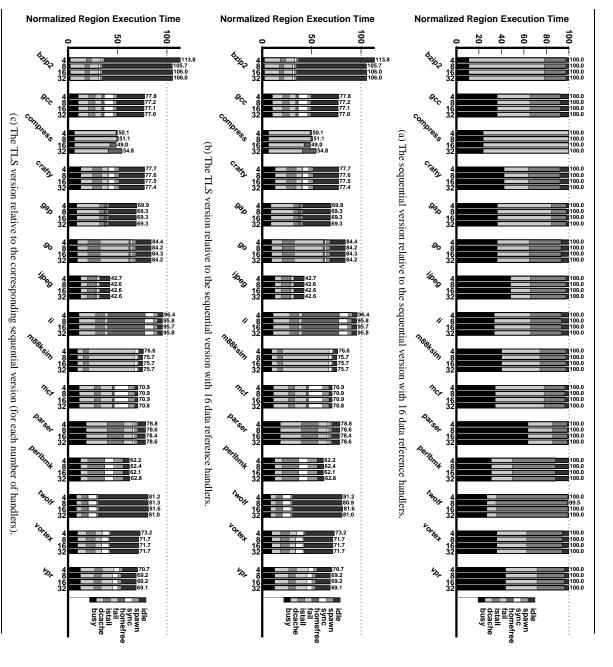

| 4.5  | Varying the number of processors for both private and shared-cache architectures. Note that the shared       |     |

|------|--------------------------------------------------------------------------------------------------------------|-----|

|      | cache is the same size as each of the private caches (32KB)                                                  | 95  |

| 4.6  | Benefits of implicit forwarding in a shared cache. $N$ does not support implicit forwarding, while $S$ (our  |     |

|      | shared-cache baseline) does                                                                                  | 96  |

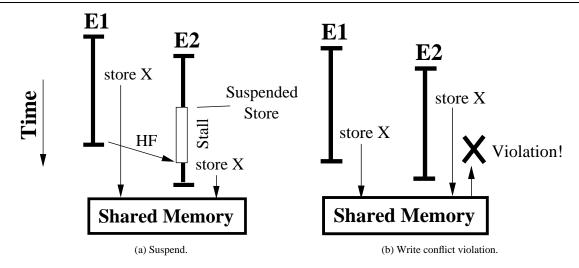

| 4.7  | Two epochs that store the same cache line. In (a), suspension of epoch 2 allows it to proceed later. In      |     |

|      | (b), suspension cannot help, and epoch 2 is violated due to the write conflict                               | 97  |

| 4.8  | Impact of suspending violations for replacement and conflicts. S is the baseline 4-processor shared-         |     |

|      | cache architecture, $U$ builds on $S$ by tolerating conflicts and replacement through suspension of the      |     |

|      | logically-later epoch, $R$ builds on $S$ by tolerating conflicts through replication, and $Q$ supports both  |     |

|      | suspension and replication                                                                                   | 98  |

| 4.9  | Example of cache line replication                                                                            | 99  |

| 4.10 | Hardware support for multiple writers in a shared cache that also supports replication                       | 99  |

| 4.11 | Impact of suspending violations for replacement and conflicts when the shared data cache is 4-way            |     |

|      | set-associativity (as opposed to 2-ways). $S$ is the baseline 4-processor shared-cache architecture, $U$     |     |

|      | builds on $S$ by tolerating conflicts and replacement through suspension of the logically-later epoch, $R$   |     |

|      | builds on $S$ by tolerating conflicts through replication, and $Q$ supports both suspension and replication. | 101 |

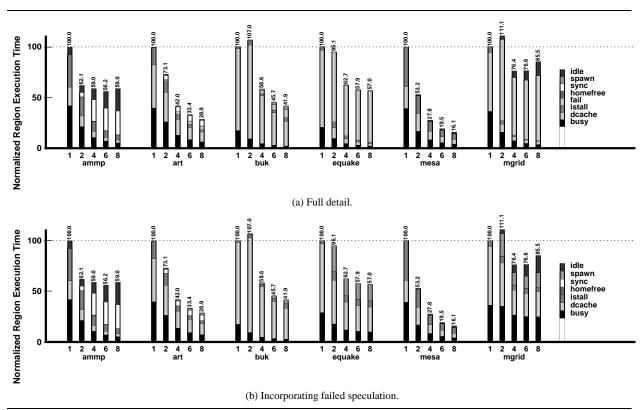

| 4.12 | Region performance of the <i>select</i> version of the floating point benchmarks when scaling (varying the   |     |

|      | number of processors) within a chip                                                                          | 102 |

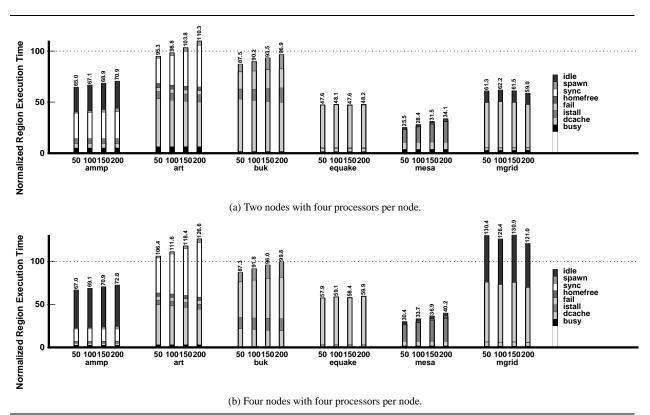

| 4.13 | Region performance of the select version of the floating point benchmarks on multiprocessor archi-           |     |

|      | tectures with varying numbers of processors and nodes. For each benchmark we simulate 1, 2, and 4            |     |

|      | nodes (N) of 1, 2, 4, and 8 processors per node                                                              | 104 |

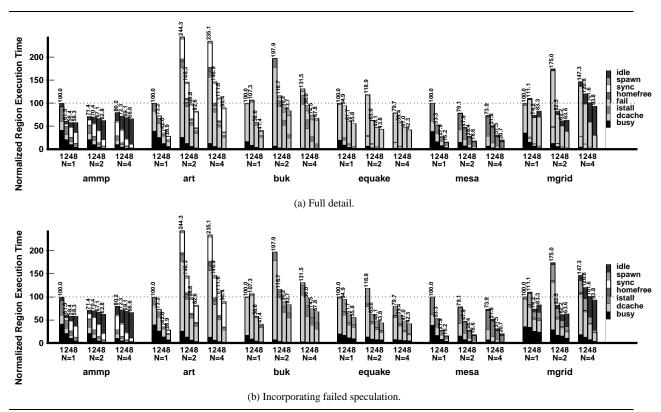

| 4.14 | Impact of varying the communication latency between nodes (chips) from 50 to 200 cycles; note that           |     |

|      | for our baseline architecture it is 100 cycles.                                                              | 106 |

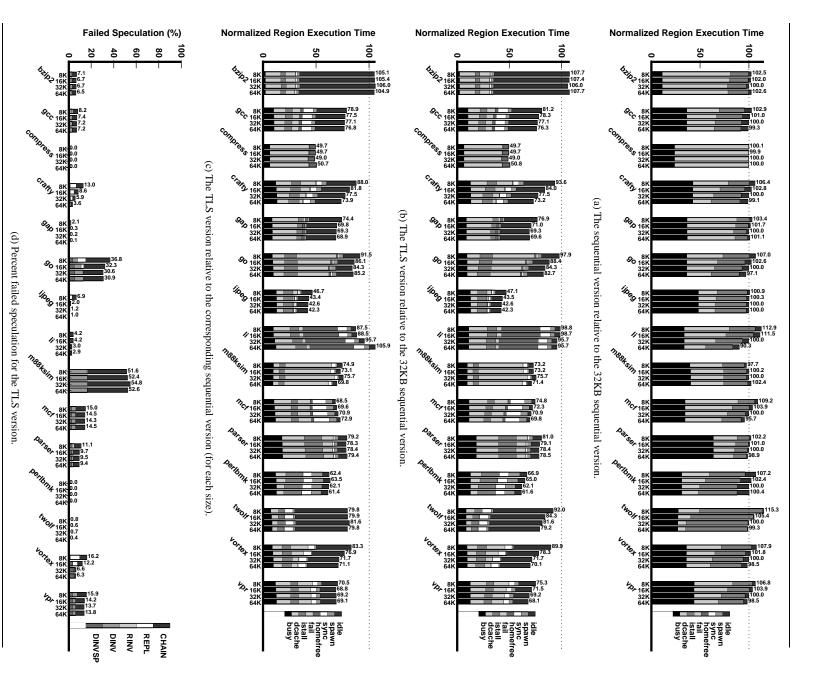

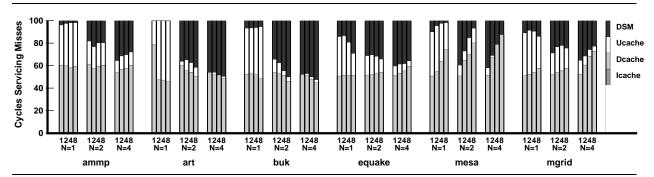

| 4.15 | Breakdown of cycles spent servicing misses (in the memory system) for varying numbers of nodes (N)             |     |

|------|----------------------------------------------------------------------------------------------------------------|-----|

|      | and processors per node. DSM represents cycles spent on accessing both local and remote memory                 |     |

|      | in the distributed shared memory system; Ucache represents cycles spent on contention and trans-               |     |

|      | mission in the inter-connection network (crossbar) between the data and instruction caches and the             |     |

|      | unified cache, as well as cycles spent on fill and contention in the unified cache itself; Dcache rep-         |     |

|      | resents cycles spent for fill and contention in the data cache while servicing data cache misses; and          |     |

|      | Icache represents cycles spent on both filling cache lines and contention in the instruction cache while       |     |

|      | servicing instruction cache misses.                                                                            | 107 |

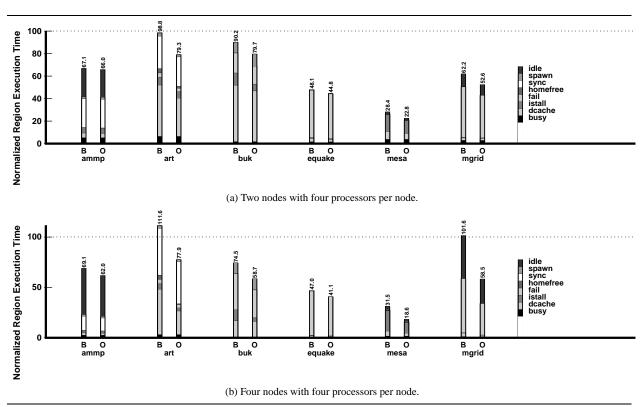

| 4.16 | Impact of the DSM page layout. B is the "baseline" data layout from Figure 4.13, and O models an               |     |

|      | oracle migration strategy to estimate the maximum potential benefit of improved page allocation                | 108 |

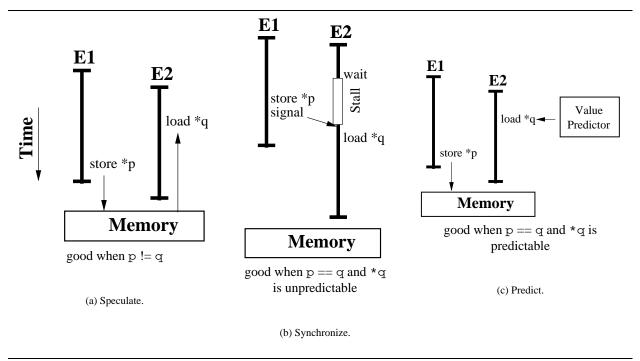

| 5.1  | A memory value may be communicated between two epochs (E1 and E2) through (a) speculation, (b)                 |     |

|      | synchronization, or (c) prediction.                                                                            | 111 |

| 5.2  | Potential impact of optimizing value communication. Relative to the normalized, original sequential            |     |

|      | version, $U$ shows the unoptized speculative version and $P$ shows perfect prediction of all inter-thread      |     |

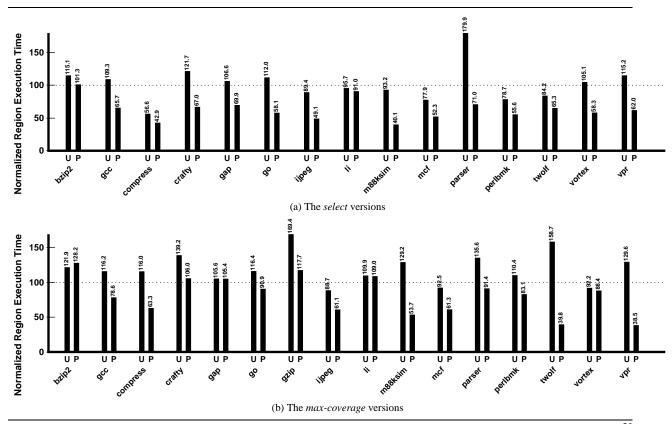

|      | data dependences                                                                                               | 112 |

| 5.3  | Reducing the critical forwarding path                                                                          | 113 |

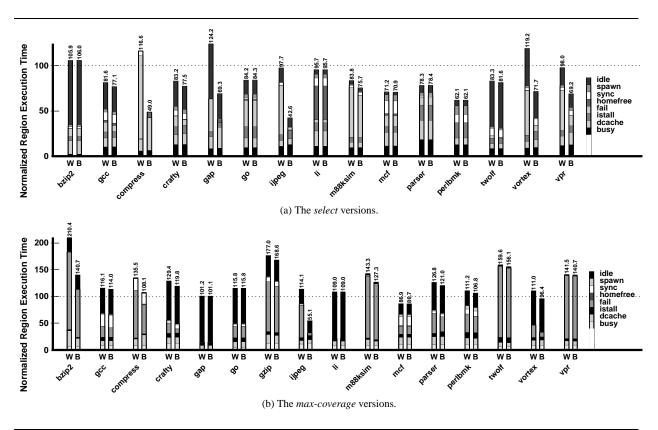

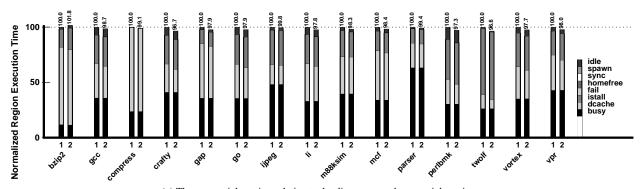

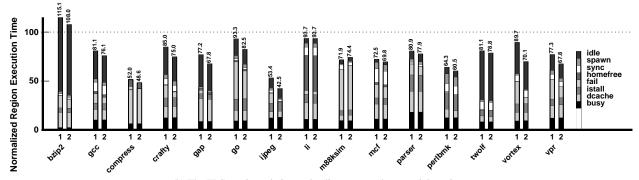

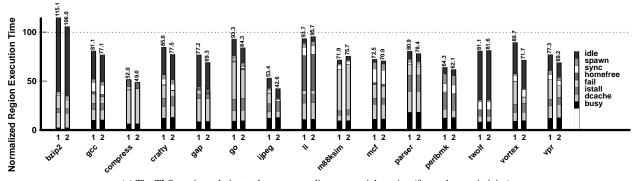

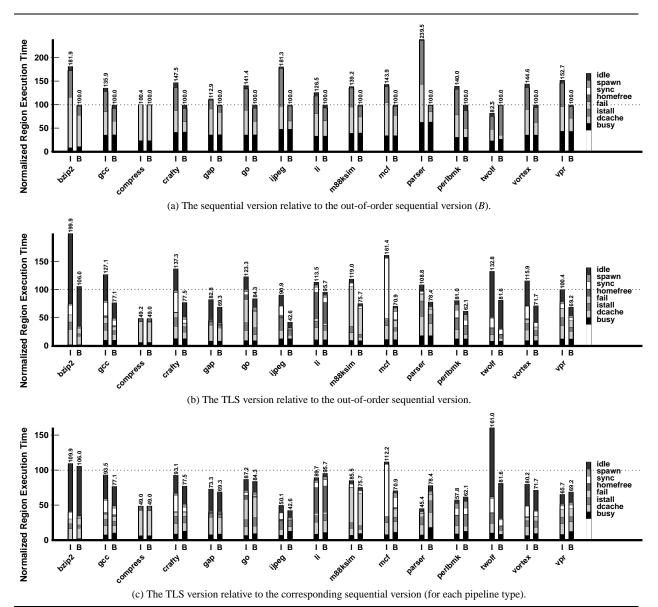

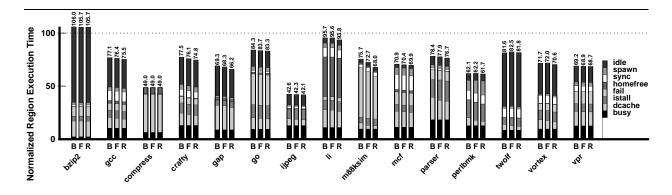

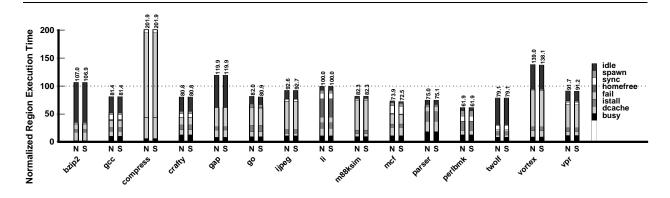

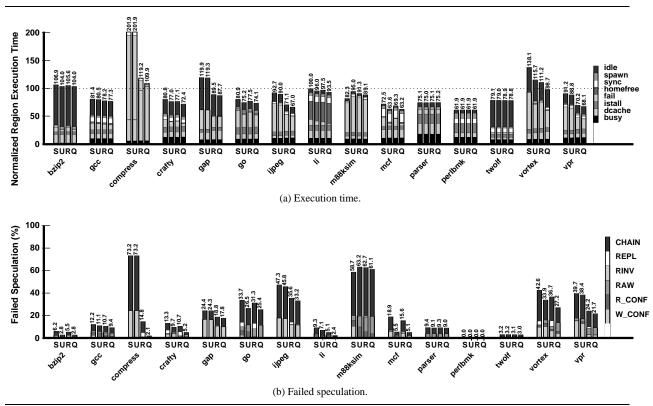

| 5.4  | Performance impact of our TLS compiler. For each experiment, we show normalized region execution               |     |

|      | time scaled to the number of processors multiplied by the number of cycles (smaller is better). S is           |     |

|      | the sequential version, $T$ is the TLS version run sequentially. There are two versions of TLS code            |     |

|      | run in parallel: $U$ and $B$ are without and with compiler scheduling of the critical forwarding path,         |     |

|      | respectively. Each bar shows a breakdown of how time is being spent.                                           | 114 |

| 5.5  | Impact of issuing around wait instructions. For <i>W</i> , instructions cannot issue out-of-order with respect |     |

|      | to a blocked wait instruction, while in $B$ (our baseline) they can                                            | 116 |

| 5.6  | Potential for improved value communication. B is our baseline, M shows perfect prediction of mem-              |     |

|      | ory values, F shows perfect prediction of forwarded values, and P shows perfect prediction of both             |     |

|      | forwarded and memory values                                                                                    | 117 |

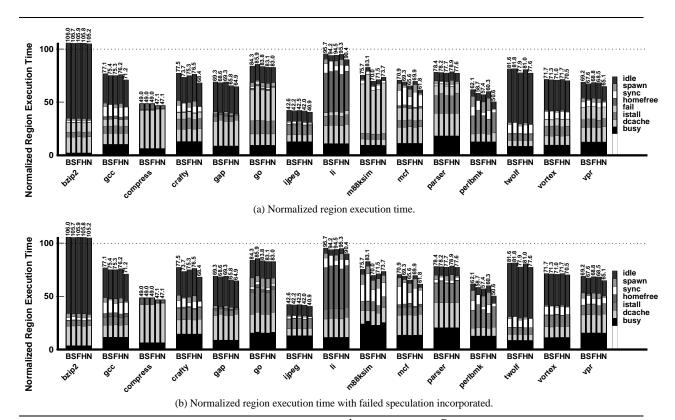

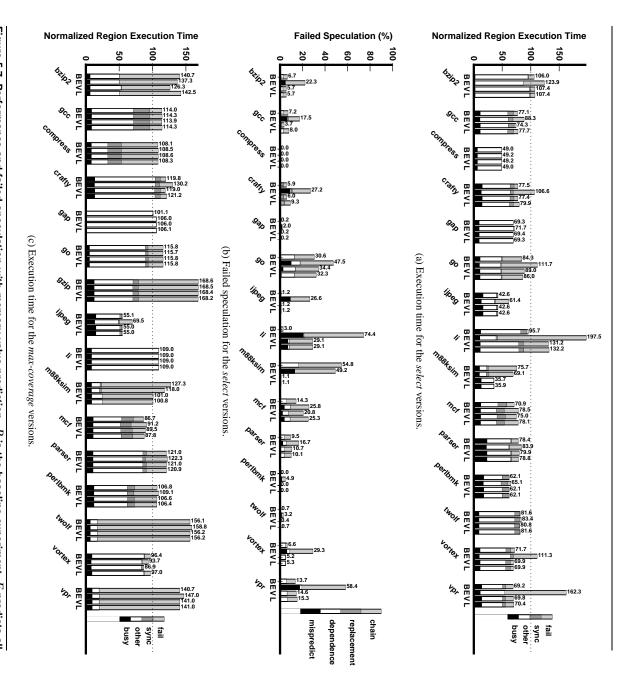

| 5.7  | Performance and failed speculation with memory value prediction. $B$ is the baseline experiment, $E$              |     |

|------|-------------------------------------------------------------------------------------------------------------------|-----|

|      | predicts all exposed loads, V only predicts loads that have caused violations using an exposed load               |     |

|      | table and a violating loads list that are both unlimited in size, and $L$ refines $V$ with tables/lists that are  |     |

|      | realistic in size                                                                                                 | 121 |

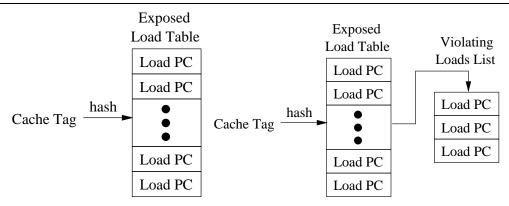

| 5.8  | Two mechanisms used to throttle memory value prediction: the exposed load table and violating loads               |     |

|      | list                                                                                                              | 122 |

| 5.9  | Performance of forwarded value prediction. $B$ is the baseline experiment, $F$ predicts all forwarded             |     |

|      | values S predicts forwarded values that have caused stalls                                                        | 124 |

| 5.10 | Performance of silent stores optimization. $B$ is the baseline experiment, and $S$ optimizes silent stores.       | 127 |

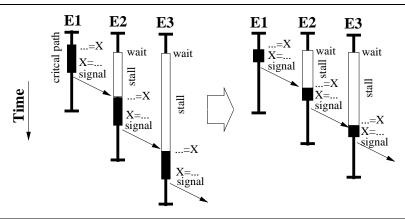

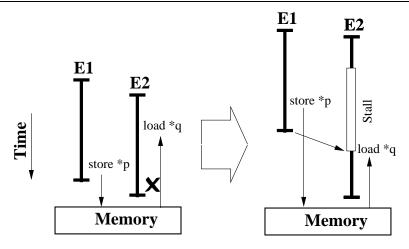

| 5.11 | Dynamic synchronization, which avoids failed speculation (left) by stalling the appropriate load until            |     |

|      | the previous epoch completes (right)                                                                              | 128 |

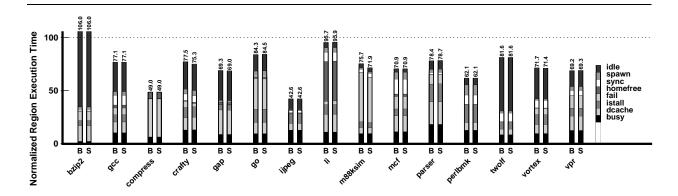

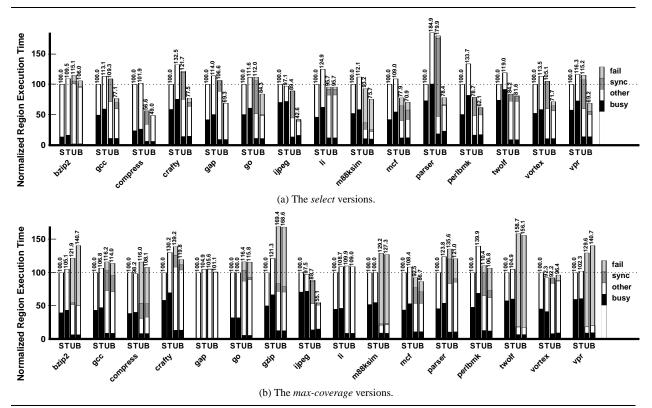

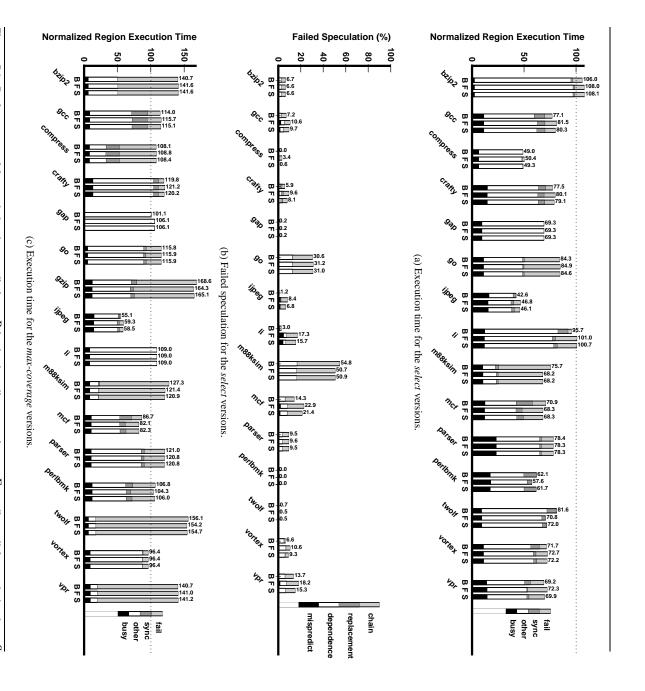

| 5.12 | Performance of dynamic synchronization. $B$ is the baseline experiment, $D$ automatically synchronizes            |     |

|      | all violating loads (using a exposed load tables and violating loads lists of unlimited size), R builds on        |     |

|      | D by periodically resetting the violating loads list, and $L$ refines $R$ with tables that are realistic in size. | 129 |

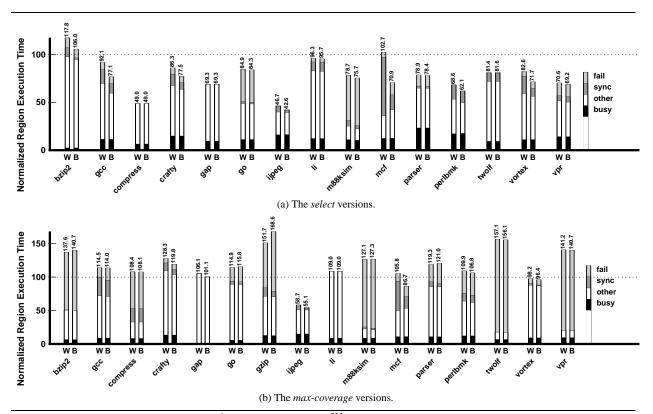

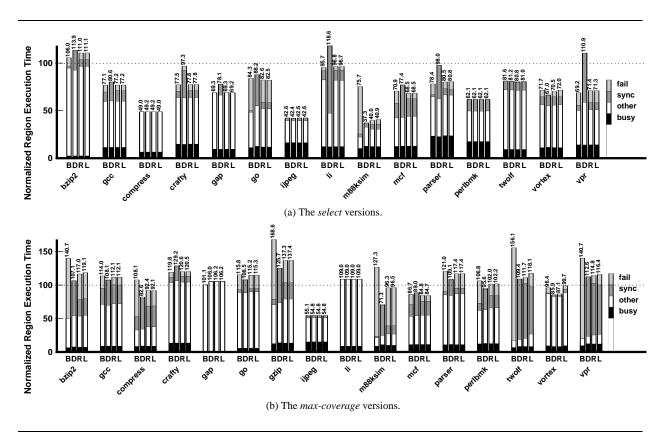

| 5.13 | Prioritization of the critical forwarding path. We show (a) our algorithm, where we mark the instruc-             |     |

|      | tions on the input chain of the critical store and the pipeline's issue logic gives them high priority; (b)       |     |

|      | some statistics, namely the fraction of issued instructions that are given high priority by our algorithm         |     |

|      | and issue early, and also the improvement in the average number of cycles from the start of the epoch             |     |

|      | until each signal                                                                                                 | 131 |

| 5.14 | Performance impact of prioritizing the critical forwarding path: $B$ is the baseline experiment, and $S$          |     |

|      | prioritizes the critical forwarding path.                                                                         | 132 |

| 5.15 | Performance impact of prioritizing the critical forwarding path when it has not been scheduled by                 |     |

|      | the compiler: $U$ has not been scheduled by the compiler, $S$ builds on $U$ by prioritizing the critical          |     |

|      | forwarding path, and $B$ is scheduled by the compiler                                                             | 133 |

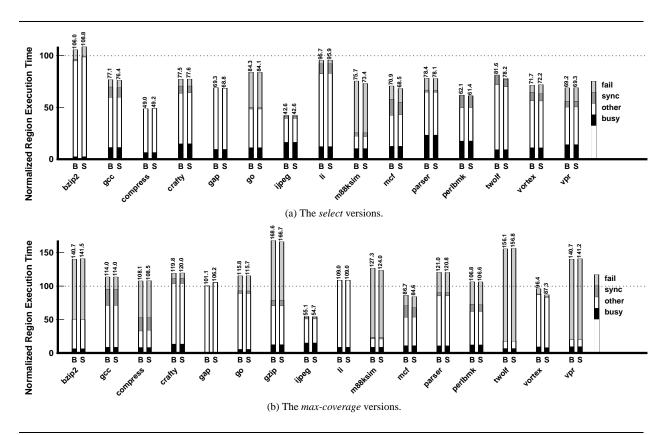

| 5.16 | Performance of all techniques combined. $B$ is the baseline experiment, $F$ models techniques for op-             |     |

|      | timizing forwarded values, $M$ models techniques for optimizing memory values, and $A$ models all                 |     |

|      | techniques                                                                                                        | 134 |

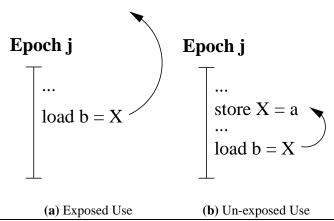

| A.1 | Exposed and un-exposed uses. |  |  |  |  |  |  |  |  |  |  |  |  |  | <br>147 |

|-----|------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|---------|

|     |                              |  |  |  |  |  |  |  |  |  |  |  |  |  |         |

## **List of Tables**

| 1.1 | Summary of related hardware schemes for TLS                                             | 6   |

|-----|-----------------------------------------------------------------------------------------|-----|

| 2.1 | Benchmark descriptions and inputs used                                                  | 24  |

| 2.2 | Truncation of benchmark execution                                                       | 25  |

| 2.3 | Statistics for the <i>select</i> benchmark versions                                     | 26  |

| 2.4 | Statistics for the <i>max-coverage</i> benchmark versions                               | 28  |

| 2.5 | Comparing TLS and sequential versions of the <i>select</i> benchmarks                   | 29  |

| 2.6 | Simulation parameters                                                                   | 33  |

| 3.1 | Memory Access Statistics                                                                | 39  |

| 3.2 | Region and Program Speedups and Coverage                                                | 54  |

| 3.3 | Forwarding Frame Sizes (in 8-byte words)                                                | 82  |

| 5.1 | Memory value prediction statistics for the <i>select</i> benchmarks                     | 120 |

| 5.2 | Forwarded value prediction statistics for the <i>select</i> benchmarks                  | 125 |

| 5.3 | Percent of dynamic, non-stack stores that are silent (for the <i>select</i> benchmarks) | 126 |

| 5.4 | Summary of techniques for improving value communication                                 | 135 |

| A.1 | Shared cache line states                                                                | 143 |

| A.2 | Processor-initiated actions                                                             | 144 |

| A.3 | Actions generated by the shared cache controller.                                       | 145 |

| A.4 | Other actions                                                                           | 148 |

| A.5 | Cache state transition diagram (Continued on next page). $\rightarrow$ X represents the transition to new state X, |     |

|-----|--------------------------------------------------------------------------------------------------------------------|-----|

|     | and (A)?(B):(C) denotes if A then B else C                                                                         | 150 |

| A.5 | Cache state transition diagram (Continued on next page)                                                            | 151 |

| A 5 | Cache state transition diagram (Continued from previous page)                                                      | 152 |

## Chapter 1

## Introduction

Due to rapidly increasing transistor budgets, today's microprocessor architect is faced with the pleasant challenge of deciding how to translate these extra resources into improved performance. In the last decade, microprocessor performance has improved steadily through the exploitation of *instruction-level parallelism* (ILP), resulting in superscalar processors that are increasingly wider-issue, out-of-order, and speculative. However, this highly-interconnected and complex approach to microarchitecture is running out of steam. Cross-chip wire latency (when measured in processor cycles) is increasing rapidly, making large and highly interconnected designs infeasible [1,58]. Both development costs and the size of design teams are growing quickly and reaching their limits. Increasing the amount of on-chip cache eventually shows diminishing returns [22]. Instead, an attractive option is to exploit *thread-level parallelism* (TLP).

The transition to new designs that support multithreading has already begun: the Sun MAJC [68], IBM Power4 [38], and the Sibyte SB-1250 [8] are all *chip-multiprocessors* (CMPs), in that they incorporate multiple processors on a single die. Alternatively, the Alpha 21464 [20] supports *simultaneous multithreading* (SMT) [19,70,71], where instructions from multiple independent threads are simultaneously issued to a single processor pipeline. These new architectures still benefit from ILP, since ILP and TLP are complementary.

While it is relatively well-understood how to design cost-effective CMP and SMT architectures, the real issue is how to use thread-level parallelism to improve the performance of the software that we care about. Multiprogramming workloads (running several independent programs at the same time) and multithreaded programs (using separate

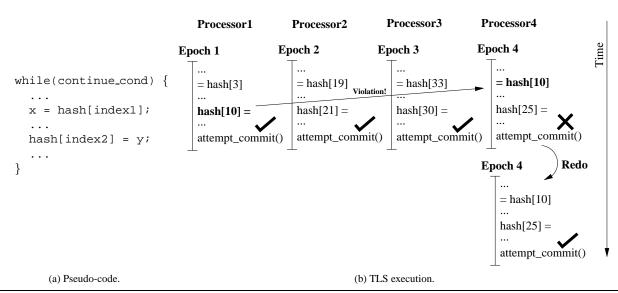

Figure 1.1. Example of thread-level speculation (TLS).

threads for programming convenience, such as in a web server) both naturally take advantage of the available concurrent threads. However, we often are concerned with the performance of a single application. To use a multithreaded processor to improve the performance of a single application we need that application to be *parallel*.

Writing a parallel program is not an easy task, requiring careful management of communication and synchronization, while at the same time avoiding load-imbalance. We would instead like the compiler to translate any program into a parallel program automatically. While there has been much research in this area of automatic parallelization for *numeric* programs (array-based codes with regular access patterns), compiler technology has made little progress towards the automatic parallelization of *non-numeric* applications: progress here is impeded by ambiguous memory references and pointers, as well as complex control and data structures—all of which force the compiler to be conservative. Rather than requiring the compiler to prove independence of potentially-parallel threads, we would like the compiler to be able to parallelize if it is *likely* that the potential threads are independent. This new form of parallel execution is called *thread-level speculation* (TLS).

#### 1.1 Example

TLS allows the compiler to automatically parallelize portions of code in the presence of statically ambiguous data and control dependences, thus extracting parallelism between whatever dynamic dependences actually exist at runtime. To illustrate how TLS works, consider the simple while loop in Figure 1.1(a) which accesses elements in

a hash table. This loop cannot be statically parallelized due to possible data dependences through the array hash. While it is possible that a given iteration will depend on data produced by an immediately preceding iteration, these dependences may in fact be infrequent if the hashing function is effective. Hence a mechanism that could speculatively execute the loop iterations in parallel—while squashing and re-executing any iterations which do suffer dependence violations—could potentially speed up this loop significantly, as illustrated in Figure 1.1(b). In this example, the program is running on a shared-memory multiprocessor, and some number of processors (four, in this case) have been allocated to the program by the operating system. Each of these processors is assigned a unit of work, or *epoch*, which in this case is a single loop iteration. When complete, each epoch attempts to commit its speculative work. In this case a *read-after-write* (RAW) data dependence violation is detected between *epoch 1* and *epoch 4*; hence *epoch 4* is squashed and restarted to produce the correct result, while *epochs* 1, 2, and 3 commit. This example demonstrates the basic principles of TLS.

#### 1.2 Related Work

This section provides an overview of the field of related work, which can be divided into three categories: loosely-related work, related work done prior to this dissertation, and related work done concurrently. An in-depth discussion of how this dissertation is differentiated from related work is given in each successive chapter.

#### 1.2.1 Loosely-Related Work

Concepts similar to thread-level speculation have been explored in concurrency for databases, aggressive simulation, and functional languages. For databases, the concept of speculative synchronization [43, 45, 46] as an alternative to mutual exclusion was a matter of great debate in the database community; the results of this debate are summarized by Agrawal *et al.* [2]. The time warp operating system [36] is an optimistically-parallel discrete event simulation engine, where a simulation is parallelized with optimistic synchronization. Events are simulated early—when the input parameters may possibly still change. In the case of misspeculation, the results of the simulated event are rolled back and the event is re-simulated to ensure correctness. Finally, Knight [39] and Halstead [61] each proposed forms of thread-level speculation within the context of functional languages.

#### 1.2.2 Prior Related Work

Herlihy et al. [35, 53] proposed using transactional memory to support TLS for numeric codes; however, this work was quite preliminary, and not explored in detail. The following two works are more relevant: the LRPD test [60] which is a software-only version of TLS that applies only to array-based codes, and the Multiscalar architecture [27, 65] which was the first complete evaluation of an architecture designed specifically for supporting TLS. More detail about each of these schemes follows.

#### The LRPD Test

Padua *et al.* [60] devised a method for parallelizing loops for numeric codes in the presence of ambiguous data dependences. Their entirely software-based approach, called the *LRPD* test, allows the compiler to parallelize loops without fully disambiguating all memory references. For a given loop, the LRPD test is performed on each shared variable with ambiguous references by creating corresponding *shadow arrays* to track read and write accesses. These shadow arrays are examined at the end of the parallel execution of the loop: if any cross-iteration data dependences were violated, the loop is re-executed sequentially; otherwise the parallel execution of the loop was correct.

Although a purely software-based approach is attractive, there are two shortcomings to the LRPD test. First, the LRPD test requires the creation of shadow storage for all shared data, and is therefore not applicable to most non-numeric codes due to their complex data structures and extensive use of heap-allocated objects. Second, the LRPD test does not extract any parallelism in the presence of a single cross-iteration *read-after-write* dependence: the loop is re-executed sequentially in such cases. In summary, only a narrow class of loops can be parallelized effectively using the LRPD test.

#### The Multiscalar Architecture

The most relevant prior work is the Wisconsin multiscalar architecture [26, 27, 65]. This architecture performs aggressive control and data speculation through the use of large hardware structures devoted to the task. The following describes the multiscalar system architecture, beginning with the compilation process.

During compilation for multiscalar execution, a program is broken up into small *tasks*. A task may consist of a only few instructions or perhaps several basic blocks. The compiler inserts a bit-vector called the *create mask* into every task denoting which registers are live at the end of the task. Hardware then uses this information to forward register

values between tasks.

The multiscalar architecture speculatively executes tasks in parallel by executing the tasks before the corresponding branches and memory dependences have been resolved. Processors in the multiscalar architecture are arranged in a ring, and each processor is tightly-coupled with its two neighboring processors. At any given time during execution, one of the processors is considered the *head* of the ring: this processor is executing the oldest task, and its work is not considered speculative since there are no longer any preceding tasks. There are two main benefits to the ring architecture. First, the ordering between tasks is implied by the order of the processors in the ring, thus making it trivial to terminate the appropriate tasks when a dependence is violated. Second, the tight-coupling of adjacent processors in the ring simplifies register forwarding, since register values are forwarded between consecutive tasks.

As described earlier, the create mask informs hardware which registers are live at the end of each task, and hardware automatically forwards these register values between tasks. Synchronization of register values that are communicated between tasks is provided by a *busy bit* that is associated with each register which is set when the register value arrives at the receiving processor.

To support data speculation, the multiscalar architecture includes the *address resolution buffer* (ARB) [27] which performs dynamic memory disambiguation. The ARB sits between the processors and the first-level cache, and all memory accesses are filtered through it. For each store to memory, the store address and the value are saved in one of the ARB's associative entries for the corresponding processor. On each memory access, the ARB is searched for previous accesses to the same address: if the ARB notices that a store and load to the same address have occurred out-of-order then all speculative tasks including and beyond the violating task are terminated.

Although the multiscalar architecture facilitates efficient control and data speculation, it does so at the cost of an architecture which is highly specialized to that mode of execution. The ring layout of processors is beneficial for forwarding data between consecutive tasks, but is not efficient when executing a conventional parallel program. The ARB is a large and complex structure; since an associative search is performed for most memory accesses, latency through the ARB is longer than that of an ordinary first-level cache. Therefore the multiscalar architecture will not be efficient at executing multiprogramming workloads or even conventional parallel programs. However, experimental results for the multiscalar architecture show that speculative execution is a promising way to improve the performance of non-numeric applications using multiple processors.

Table 1.1. Summary of related hardware schemes for TLS.

| Approach             | System<br>Composition | Underlying<br>Architecture | Applications<br>Supported | Speculative<br>Buffering          |

|----------------------|-----------------------|----------------------------|---------------------------|-----------------------------------|

| DMT [4]              | HW-only               | SMT                        | general-purpose           | buffer between processor and L1   |

| CSMP [50]            | HW-only               | SMT                        | general-purpose           | L1 cache                          |

| Trace Processor [62] | HW-only               | CMP                        | general-purpose           | (not specified)                   |

| Krishnan99 [42]      | SW/HW                 | CMP                        | general-purpose           | L1 caches                         |

| Hydra [34]           | SW/HW                 | CMP                        | general-purpose           | buffers between L1s and L2        |

| SVC [31]             | SW/HW                 | CMP                        | general-purpose           | L1 caches                         |

| SUDS [25]            | SW/HW                 | CMP (RAW)                  | general-purpose           | undo-log/buffer at each processor |

| Zhang99 [78]         | SW/HW                 | MP                         | numeric                   | undo-log/buffer at each node      |

| Cintra00 [12]        | SW/HW                 | MP/CMP                     | numeric                   | L1 and L2 caches                  |

| Our approach         | SW/HW                 | MP/CMP/SMT                 | general-purpose           | L1 caches                         |

#### 1.2.3 Concurrent Related Work

There are currently many approaches to support for TLS. Of these, one class of schemes are implemented entirely in software [32, 60, 63] but require explicit code and storage to track data dependences and buffer speculative modifications (or provide an undo-log); these schemes are thus only effective for array-based, numeric applications where the portions of memory for which cross-thread dependences need to be tracked are well defined. A software-only approach to TLS support for arbitrary memory accesses (pointers) is infeasible.

Approaches to TLS that involve hardware support may be divided into two classes: those that are implemented entirely in hardware [4, 50, 62], and those that use both hardware and software [12, 25, 31, 34, 41, 42, 59, 78], as summarized in Table 1.1. Hardware-only approaches have the advantage of operating on unmodified binaries, but are limited since hardware must decide how to break programs into speculative threads without knowledge of high-level program structure. Hardware-only approaches are generally more complex than those that take advantage of software support since any transformation and optimization of TLS execution must be implemented entirely in hardware, in addition to the mechanisms for selecting speculative threads.

These schemes may also be classified based on the underlying architecture: those that focus on chip-multiprocessor (CMP) architectures [25, 31, 34, 41, 56, 78]<sup>1</sup>, those that focus on simultaneously-multithreaded (SMT) or other shared-cache architectures [4, 50], and those that scale beyond a single chip to multiprocessor (MP) architectures [12, 32, 59, 60, 63, 77, 79]. With the exception of the scheme by Cintra *et al.* [12], no related approach is scalable both within a chip and also beyond a chip to multiprocessor systems; i.e., no related approach is applicable to multiprocessor

<sup>&</sup>lt;sup>1</sup>Note that the SUDS scheme [25] is implemented using the MIT RAW reconfigurable architecture, as opposed to extending a conventional CMP.

systems, chip-multiprocessors, and shared-cache architectures (such as SMT).

Related approaches can also be differentiated by the class of applications that are supported. Two approaches [12, 78] focus solely on numeric applications, while the rest focus on general-purpose applications. Any scheme which supports general-purpose applications will also function correctly for numeric applications. However, no related work contains a thorough evaluation of both general-purpose and numeric applications. It is also important to note that related schemes that do scale beyond a chip (MP) focus solely on numeric applications.

Finally, related approaches demonstrate a wide variety of hardware implementations, of which one of the most important features is the mechanism for buffering speculative state and tracking data dependences between speculative threads. For this purpose, dynamic multithreading (DMT) [4], SUDS [25], and Zhang *et al.* [78] introduce a new buffer near the processor; the latter two approaches speculatively modify memory and use the buffers to maintain an undo log, while the former uses its buffers to separate speculative modifications from memory. The Hydra [34] introduces speculative buffers between the write-through first-level caches and the unified second-level cache. These speculative buffers must be sufficiently large to be effective, but adding large amounts of speculation-specific buffering to the memory hierarchy is undesirable. The remaining approaches [12, 31, 42, 50]<sup>2</sup> use the existing caches as speculative buffers. A comprehensive summary and quantitative comparison of several schemes for TLS support is provided by Garazan *et al.* [29].

The next section describes the goals that differentiate this dissertation from related work.

#### 1.3 Research Goals

While there are many important issues regarding the role of the compiler in TLS, this thesis focuses on the design of the underlying hardware support. Thus, my thesis is that: hardware support for thread-level speculation that is simple and efficient, and that can scale to a wide range of multithreaded architectures can empower the compiler to improve the performance of sequential applications. Furthermore, a deep understanding of the key aspects of this novel hardware support—tracking data dependences and buffering speculative state, detecting and recovering from failed speculation, management of speculative threads, communication of data values between speculative threads, and the partitioning of these mechanisms between hardware and software—can be obtained.

<sup>&</sup>lt;sup>2</sup>The Trace Processor [62] approach does not specify means for buffering speculative modifications and tracking data dependences, deferring instead to related work.

The hardware support for TLS presented in this dissertation achieves the following four goals:

- 1. to handle arbitrary memory accesses—not just array references;

- 2. to preserve the performance of non-speculative workloads;

- 3. to provide a framework for scaling seamlessly both within and beyond chip boundaries;

- 4. to fully exploit the compiler and minimize the amount and complexity of the underlying hardware support.

While some previous efforts achieve a subset of the above goals, none achieves all four—hence these goals differentiate this work.

#### 1.4 Overview

The remainder of this dissertation is organized as follows. Chapter 2 provides the background necessary for the remainder of the dissertation. We define TLS terms and its execution model, and describe a cooperative approach to TLS hardware support—defining the roles of compiler and hardware and the interface between them. Also presented are the compiler infrastructure, benchmark applications, and simulation framework used in the evaluations in this dissertation. The chapter concludes with an estimate of the potential performance benefits of TLS for the benchmark applications.

In Chapter 3, we present the design for a unified mechanism for supporting thread-level speculation which can handle arbitrary memory access patterns and which is appropriate for any scale of architecture with parallel threads. The evaluation in this chapter focuses on support within a chip-multiprocessor, while in Chapter 4 we evaluate further support for speculation in a shared cache as well as the scalability of our approach beyond chip boundaries.

Chapter 5 provides a comprehensive evaluation of techniques for enhancing value communication between speculative threads, including several schemes for prediction and synchronization. The impact of compiler optimization on these techniques is also quantified.

Finally, we conclude in Chapter 6 by enumerating the contributions of this dissertation and discussing potential future directions. Note that the Appendix defines the speculative cache coherence scheme in full detail

## Chapter 2

## **Thread-Level Speculation**

#### 2.1 Introduction

This chapter provides the background necessary for the rest of the dissertation. We begin with a description of the high-level execution model for TLS targeted by software as well as the software interface to architected TLS support, including the definitions of new instructions. The compilation infrastructure including thread selection, code transformation, optimization, and code generation are all described, although an in-depth evaluation of compilation issues for TLS [76] is beyond the scope of this thesis<sup>1</sup>. This chapter also presents the experimental framework used in the evaluations throughout this dissertation including the benchmark applications and simulation infrastructure. Finally, through a preliminary simulation study we demonstrate the potential for TLS to improve performance.

#### 2.2 Execution Model

This section describes the execution model for TLS that is targeted by the compiler and implemented in hardware.

The following description also serves as a high-level overview of the tremainder of this section.

First, we divide a program into speculatively-parallel units of work called *epochs*. Each epoch is associated with its own underlying speculative thread, and creates the next epoch through a lightweight fork called a spawn, as shown in Figure 2.2(a). The spawn mechanism forwards initial parameters and a program counter (PC) to the appropriate processor. An alternative approach would be to have a fixed pool of speculative threads that grab epochs from a

<sup>&</sup>lt;sup>1</sup>See http://www.cs.cmu.edu/ stampede for an in-depth treatment of compilation issues for TLS

**Epoch:** The unit of execution within a program which is executed speculatively.

**Epoch Number:** A number which identifies the relative ordering of epochs within an OS-level thread. Epoch numbers also indicate that certain parallel threads are unordered.

**Homefree Token:** A token which indicates that all previous epochs have made their speculative modifications visible to memory and hence speculation for the current epoch is successful.

**Logically Earlier/Later:** With respect to epochs, *logically-earlier* refers to an epoch that preceded the current epoch in the original execution while *logically-later* refers to an epoch that followed the current epoch.

**OS-level Thread:** A thread of execution as viewed by the operating system—multiple speculative threads may exist within an OS-level thread.

**Speculative Context:** The state information associated with the execution of an epoch.

**Sequential Portion:** The portion of a program where TLS is not exploited.

Spawn: A light-weight fork operation that creates and initializes a new speculative thread.

Speculative Region: A single portion of a program where TLS (speculative parallelism) is exploited.

Speculative Thread: A light-weight thread that is used to exploit speculative parallelism within an OS-level thread.

**Violation:** A thread has suffered a true data dependence violation if it has read a memory location that was later modified by a logically-earlier epoch—other types of violations are described later.

Figure 2.1. Glossary of terms.

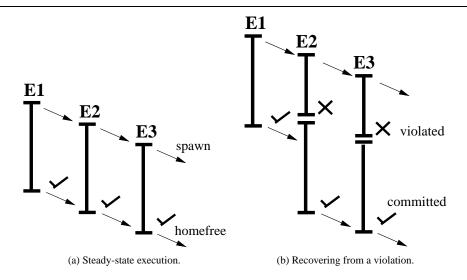

Figure 2.2. TLS execution model.

centralized work queue.

A key component of any architecture for TLS is a mechanism for tracking the relative ordering of the epochs. In our approach, we timestamp each epoch with an *epoch number* to indicate its ordering within the original sequential execution of the program. We say that *epoch X* is "*logically-earlier*" than *epoch Y* if their epoch numbers indicate that *epoch X* should have preceded *epoch Y* in the original sequential execution. Epochs commit speculative results in the original sequential order by passing a *homefree token* which indicates that all previous speculative threads have made all of their speculative modifications visible to the memory system and hence it is safe to commit. When an epoch is guaranteed not to have violated any data dependences with logically-earlier epochs and can therefore commit all of its speculative modifications, we say that the epoch is *homefree*.

In the case when speculation fails for a given epoch, all logically-later epochs that are currently running are also violated and squashed. In Figure 2.2(b), speculation fails for epoch 2 which in turn causes epoch 3 to be squashed. Although more aggressive strategies are possible, this conservative approach ensures that an epoch does not continue to execute when it may have received incorrect data.

#### 2.3 Software Interface

We have architected our TLS system to involve both the compiler and hardware, hence we require an interface between them. There are a number of issues to consider for such an interface: some issues are analogous to those for purely parallel applications, such as creating threads and managing the stacks; others are unique to TLS, such as passing the *homefree* token and recovering from failed speculation. In this section, we begin with a description of the important components of the software interface to TLS hardware, and then we present the new instructions that implement this interface.

#### 2.3.1 Required Interface Mechanisms

For thread-level speculation, there are many possible implementations for the interface between hardware and software. In this section we briefly explore the design space of interfaces and also present our approach.

```

single thread

/* Initialize v so that there is a RAW dependence

* in iteration 6 of the loop: */

y[] = \{20, 21, 22, 23, 24, 25, 5,

27, 28, 29, 30, ...};

i=0

i = 0;

while (++i < N) {

x[1]=x[21]

time

x[i] = x[y[i]];

x[2]=x[22]

x[N]=x[y[N]]

(a) The sequential version of a simple while loop.

my_i = 0;

start(my_i):

if(++my_i < N) {

i=0....

/* Pass value of my_i as a parameter to the

x[1]=x[21]

x[2]=x[22]

x[4]=x[24]

* next thread: */

x[3]=x[23]

td = lightweight_fork(&start, my_i);

|x[5]=x[25]|

x[6]=x[5]

x[my_i] = x[y[my_i]];

x[7]=x[27]

x[8]=x[28]

attempt_commit();

x[6]=x[5]

end_thread();

x[9]=x[29]

x[10]=x[30]

/* Falls through after last iteration: */

Violation.

i = my_i;

(b) The speculative version.

```

Figure 2.3. Speculative parallelization of a simple loop.

#### **Threads**

Before we discuss issues which are unique to speculation, we first consider one of the requirements for any kind of parallel execution: the creation of parallel threads. Figure 2.3(a) shows an example of a simple while loop where the elements of the array x are updated using array y as an index into x. The array y has been initialized such that the sixth iteration of the loop (i.e. when i = 6) will depend on the output of the preceding iteration (i.e. when i = 5); otherwise, the iterations are independent.

There are two methods for distributing work to threads: a static method, and a dynamic method. With static distribution, all threads are initialized prior to speculative execution—for example, by specifying a round-robin assignment of epochs for the next speculative region. With dynamic creation, each speculative thread initializes the next; this approach is more tolerant of load imbalance between epochs than the static approach. The dynamic approach is also advantageous when the number of available processors is constantly changing, (e.g. in a multiprogramming environment): the dynamic approach can more easily adapt to this situation by growing or shrinking the number of threads to match the available resources.

Figure 2.3(b) illustrates the dynamic model through a simple loop. Each epoch creates the next through a lightweight

```

my_i = 0;

start(my_i):

td = lightweight_fork(&start, my_i + 1);

x[my_i] = x[y[my_i]];

if(cancelled()) {

/* Cascade the cancel to subsequent threads: */

i = 0;

cancel_thread(td);

do {

end_thread();

x[i] = x[y[i]];

i++;

attempt_commit();

\} while (i < x[i]);

my_i++;

if(my_i < x[my_i]) {

end_thread();

(a) A simple do-while loop

with unknown bounds.

/* Cancel extra loop iterations and continue: */

cancel_thread(td);

i = my_i;

(b) Speculative version with cancelling.

```

Figure 2.4. Interface for cancelling superfluous epochs.

fork operation, performs its speculative work, and then attempts to commit its speculative modifications to memory.

The lightweight fork returns a thread descriptor (td) which serves as a handle on the next thread.

#### Stacks

A key design issue is the management of references to the stack. A naive implementation would maintain a single stack pointer (shared among all epochs) and a stack in memory that is kept consistent by the underlying data dependence tracking hardware. The problem with this approach is that speculation would fail frequently and unnecessarily: for example, whenever multiple epochs store values to the same location on the stack. These dependence violations would effectively serialize execution. In addition, whenever the stack pointer is modified, the new value must be forwarded to all successive epochs. An alternative approach is to create a separate *stacklet* [30] for each epoch to hold local variables, spilled register values, return addresses, and other procedure linkage information. These stacklets are created at the beginning of the program, assigned to each of the participating processors, and re-used by the dynamic threads. The stacklet approach allows each epoch to perform stack operations independently, allowing speculation to proceed unhindered.

#### **Epoch Cancellation**

To speculatively parallelize certain code structures we require support for *control speculation*. For example, a while loop with an unknown termination condition can be speculatively parallelized, but superfluous epochs beyond the correct termination of the loop may be created. For correct execution we require the ability to cancel any such

```

my_i = 0;

start(my_i):

if(++my_i < N) {

td = lightweight_fork(&start, my_i);

i = 0;

x[my_i] = x[y[my_i]];

while (++i < N) {

wait_for_homefree_token();

x[i] = x[y[i]];

commit_speculative_writes();

pass_homefree_token(td);

end_thread();

(a) Original code.

/* Falls through after last iteration: */

i = my_i;

(b) Threaded code.

```

Figure 2.5. Interface for passing the homefree token.

superfluous epochs. Figure 2.4(a) shows a while loop with an unknown ending condition, and Figure 2.4(b) shows the speculatively-parallelized version of the loop with support for cancelling superfluous epochs. Each speculative context provides a flag that indicates whether the current epoch has been cancelled. Any epoch that is cancelled also cancels its child epoch if one exists.<sup>2</sup> In contrast to an epoch that suffers a violation, a cancelled epoch is not re-executed by the run-time system.

#### Homefree Token

We cannot determine whether speculation has succeeded for the current epoch until all previous epochs have made their speculative modifications visible to memory—hence the act of committing speculative modifications to memory must be serialized. Two unattractive options would be 1) for a central entity to maintain the ordering of the active epochs, or 2) to broadcast to all processors any changes in the allocation of epoch numbers. A more efficient approach is to directly pass an explicit token—which we call the *homefree token*—from the logically-earliest epoch to its successor when it commits and makes all of its speculative modifications visible to memory. Receipt of the homefree token indicates that the current epoch has no predecessors, and hence is no longer speculative.

Figure 2.5 illustrates how the attempt\_commit operation can be implemented by waiting for the homefree token, committing speculative modifications to memory, and then passing the homefree token directly to the next epoch—thereby avoiding the need for central coordination. This homefree token mechanism is simply a form of producer/consumer synchronization and hence can be implemented using normal synchronization primitives. One option is to perform homefree synchronization at the user level through regular shared memory, without differentiating the homefree token from other synchronization objects. Another option is to make the homefree token visible to

<sup>&</sup>lt;sup>2</sup>Another option is to interrupt and terminate the epoch, rather than poll a flag.

- thread\_descriptor spawn(start\_address): Creates a new thread which begins execution at the start address given.

A thread descriptor is returned which can be used to refer to the thread in future calls—if no processor is able to enqueue this request for a new thread then a thread descriptor of zero is returned. A speculative context including a *stacklet* is also allocated for the new thread, and the contents of the forwarding frame are copied to the new thread's forwarding frame.

- void end\_thread(): Terminates execution of the current thread, frees its resources, frees its stack (unless it was saved), and invalidates any uncommitted speculative modifications.

- error\_code cancel\_thread(thread\_descriptor): Locates the specified thread and delivers a cancel signal to it. If the thread has registered a cancel handler, the thread asynchronously jumps to it. If not, then the thread is terminated. If the specified thread does not exist then this instruction is treated as a no-op.

- error\_code violate\_thread(thread\_descriptor): Notifies the specified thread of a violation—if the thread descriptor is null or invalid then this is a no-op.

sp save\_sp(): Returns the current stack pointer and marks it so that the stacklet is not freed when the thread ends.

void restore\_sp(sp): Frees the current stacklet and sets the stack pointer to the value provided.

#### Figure 2.6. TLS instructions for thread and stack management.

hardware so that hardware can react immediately to its arrival. For now, our software interface defers this decision and assumes that the underlying run-time system provides the necessary synchronized behavior. We will evaluate these alternatives later in Chapter 3.7.5.

#### **Value Forwarding**