# Using speculative execution to automatically hide I/O latency

Fay W. Chang December 7, 2001 CMU-CS-01-172

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

#### **Thesis Committee:**

Garth A. Gibson, Chair Gregory R. Ganger Todd C. Mowry James R. Larus, Microsoft Research

Copyright © 2001 Fay Chang

This research was sponsored by DARPA/ITO through DARPA Order D306, and issued by Indian Head Division, NSWC under contract N00174-96-0002. Additional support was provided by graduate fellowships from the Office of Naval Research and Intel, and by generous contributions from the member companies of the Parallel Data Consortium, including 3Com, Compaq, Data General, EMC, Hewlett-Packard, IBM, Intel, LSI Logic, Novell, Quantum, Seagate, StorageTek and Wind River Systems. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any of these entities or of the U.S. Government.

# **Abstract**

The gap between processing speeds and disk access times is widening. This trend is causing applications that must fetch data from disk to spend an increasing proportion of their execution times stalled on disk I/O. I/O prefetching, a well-known technique for hiding disk latency, has the potential to alleviate this problem, particularly when the data that needs to be fetched is distributed across multiple disks. A major hurdle to benefiting from this technique in practice is the difficulty of generating accurate and timely prefetches. In this dissertation, I put forth a new approach to generating accurate and timely prefetches without programmer involvement.

The key to the proposed approach is its unique method for predicting what data an executing process will access in the future. The approach involves adding an execution of each target process's code that exploits spare processing cycles. These added executions skip some operations, like accesses to uncached data, so that they can run ahead of their target normal executions. This permits differences between the data values used during the added speculative executions and their target normal executions. Despite any such differences, the approach predicts that the data accesses encountered during speculative executions will often be the same as the data accesses that will be encountered during their target normal executions such that, by initiating prefetching of that data, speculative executions could reduce the I/O stall time of their target normal executions.

To investigate the viability of this approach, I developed and evaluated SpecHint, a design and implementation for applying the approach automatically. SpecHint is based on binary modification and requires no operating system support specific to this approach. I evaluated SpecHint using six benchmarks from the TIP benchmark suite. Experiments demonstrate that, with the file system striped across four disks, SpecHint reduces the elapsed times of five of the benchmarks (text search, scientific visualization, object linking, and two database queries) by 24% to 71%, with an average of 53%. Moreover, simulation experiments suggest that, on future systems, the benefit of SpecHint would not decrease, and may even increase for some applications.

# Acknowledgements

I would like to thank my advisor, Garth Gibson, for many years of excellent advice, timely encouragement, and the many experiences that he helped make possible. I would also like to thank the other members of my committee, Greg Ganger, Jim Larus and Todd Mowry, for their helpful comments and questions. Thanks also to Steve Lucco, David Nagle, and Thomas Gross for their advice in earlier years.

I am grateful to the School of Computer Science community at CMU for providing a friendly and inspiring environment unlike any other I have known. I was also fortunate to have been a member of a wonderful lab group, the Parallel Data Lab. Thanks to all the members of the PDL for their camaraderie over the years. Special thanks to Paul Mazaitis for keeping my testbed up and running, Jim Zelenka for help with Digital Unix, and Hugo Patterson and David Rochberg for help with TIP.

Thanks to my friends for laughter, companionship, encouragement, and perspective, which have helped sustain me throughout this endeavor. And, last but not least, thanks to my parents and siblings, who have been a bedrock of support throughout my life.

# **Contents**

| 1 | Intr | oduction                                               | 1  |

|---|------|--------------------------------------------------------|----|

|   | 1.1  | The speculative execution approach                     | 2  |

|   | 1.2  | Thesis statement                                       | 3  |

|   | 1.3  | Dissertation roadmap                                   | 3  |

| 2 | Bac  | kground                                                | 7  |

|   | 2.1  | The I/O gap problem                                    | 7  |

|   | 2.2  | I/O prefetching                                        | 9  |

|   |      | 2.2.1 Potential benefits of prefetching                | 10 |

|   |      | 2.2.2 Potential risks of prefetching                   | 13 |

|   |      | 2.2.3 Prefetch scheduling and cache management         | 14 |

|   |      | 2.2.4 Predicting future data needs                     | 17 |

|   | 2.3  | Speculative execution                                  | 22 |

|   | 2.4  | Other techniques for reducing I/O stall time           | 24 |

|   | 2.5  | Summary                                                | 25 |

| 3 | The  | speculative execution approach                         | 27 |

| J | 3.1  | The speculative execution approach                     | 27 |

|   | 3.1  | 3.1.1 Potential advantages                             | 31 |

|   |      | 3.1.2 Limitations and disadvantages                    | 32 |

|   |      | 3.1.3 Discussion                                       | 35 |

|   | 3.2  | Developing a design                                    | 37 |

|   | 3.2  | 3.2.1 Design goals                                     | 38 |

|   |      | 3.2.2 Design alternatives                              | 38 |

|   |      | 3.2.3 The SpecHint design and implementation           | 39 |

|   | 3.3  | Summary                                                | 40 |

|   | ъ.   | 1 1160 /                                               | 42 |

| 4 |      | gn goal: Effectiveness                                 | 43 |

|   | 4.1  |                                                        | 43 |

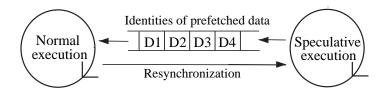

|   |      | 4.1.1 Resynchronizing speculative and normal execution | 44 |

|   |      | 4.1.2 Skipping unnecessary work                        | 46 |

|   |      | 4.1.3 Increasing the effectiveness of stale values     | 49 |

|   |      |                                                        | 51 |

|   | 4.2  | Effectiveness in SpecHint                              | 52 |

vi *CONTENTS*

|   |      | 4.2.1 Prefetch generation                  |

|---|------|--------------------------------------------|

|   |      | 4.2.2 Resynchronization policy             |

|   |      | 4.2.3 Resynchronization method             |

|   |      | 4.2.4 Experimental slicing                 |

|   |      | 4.2.5 Stale value selection                |

|   | 4.3  | Summary                                    |

| 5 | Desi | gn goal: Low overhead 59                   |

|   | 5.1  | Designing for low overhead                 |

|   |      | 5.1.1 Processing cycles                    |

|   |      | 5.1.2 Memory                               |

|   |      | 5.1.3 I/O bandwidth                        |

|   |      | 5.1.4 Useless I/O                          |

|   |      | 5.1.5 Discussion                           |

|   | 5.2  | Limiting overhead in SpecHint              |

|   |      | 5.2.1 The speculating thread               |

|   |      | 5.2.2 Memory and I/O bandwidth consumption |

|   |      | 5.2.3 Filtering                            |

|   | 5.3  | Summary                                    |

| 6 | Desi | gn goal: Safety 77                         |

|   | 6.1  | Base safety assumption                     |

|   | 6.2  | Designing for safety                       |

|   |      | 6.2.1 Separate process                     |

|   |      | 6.2.2 Shared process, separate thread      |

|   |      | 6.2.3 Shared thread                        |

|   | 6.3  | Safety of SpecHint                         |

|   |      | 6.3.1 Shadow code                          |

|   |      | 6.3.2 Support routines                     |

|   | 6.4  | Summary                                    |

| 7 | Exp  | erimental setup 113                        |

|   | 7.1  | Evaluation environment                     |

|   |      | 7.1.1 Prefetch-aware software striper      |

|   | 7.2  | SpecHint tool and object files             |

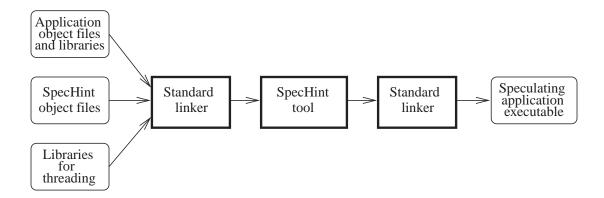

|   |      | 7.2.1 Producing executables                |

|   | 7.3  | Benchmark applications                     |

|   |      | 7.3.1 Agrep                                |

|   |      | 7.3.2 XDataSlice                           |

|   |      | 7.3.3 Gnuld                                |

|   |      | 7.3.4 Postgres                             |

|   |      | 7.3.5 Sphinx                               |

|   | 7.4  | Summary                                    |

|   |      |                                            |

| CONTENTS | vii |

|----------|-----|

|----------|-----|

| 8 | Eva | luation  |                                                 | 125   |

|---|-----|----------|-------------------------------------------------|-------|

|   | 8.1 | Single a | application, naive SpecHint                     | . 125 |

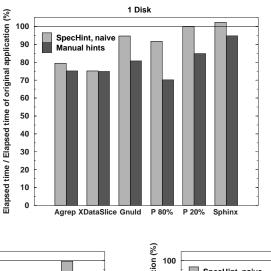

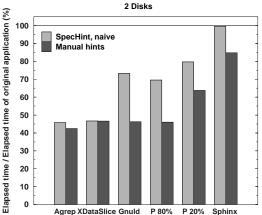

|   |     | 8.1.1    | Overall performance                             | . 126 |

|   |     |          | Hinting performance                             |       |

|   |     |          | Prefetching performance                         |       |

|   |     |          | Caching performance                             |       |

|   |     | 8.1.5    | Overhead to normal execution                    | . 137 |

|   |     | 8.1.6    | Performance of speculative execution            | . 139 |

|   | 8.2 | Single a | application, improving SpecHint effectiveness   | . 141 |

|   |     | 8.2.1    | Minimal updates to execution state              | . 142 |

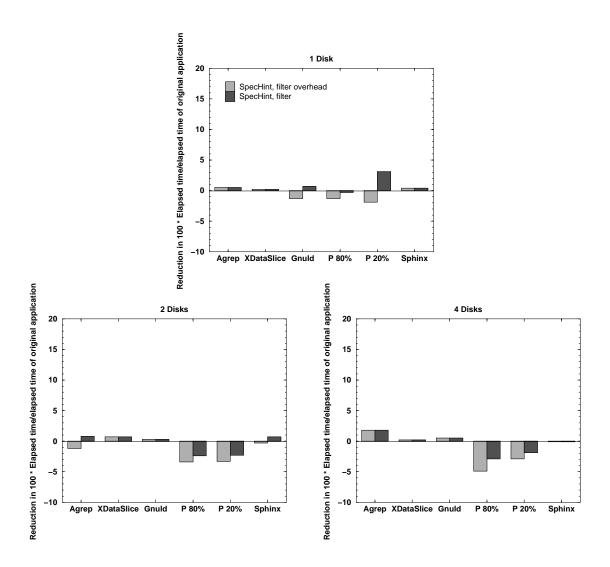

|   |     |          | Prefetch correctness prediction and filtering   |       |

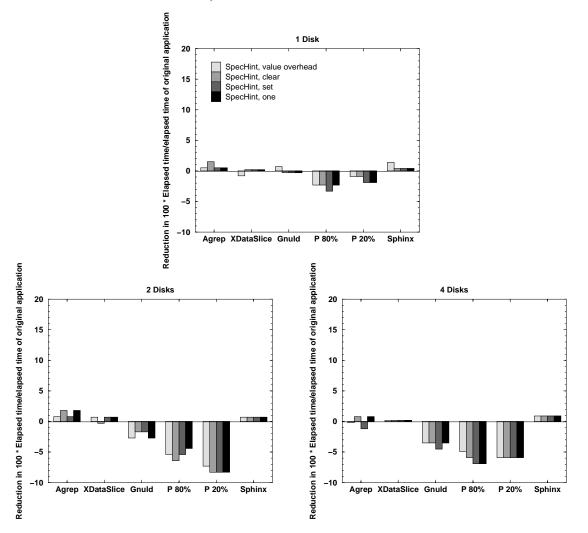

|   |     | 8.2.3    | Simple value prediction                         | . 146 |

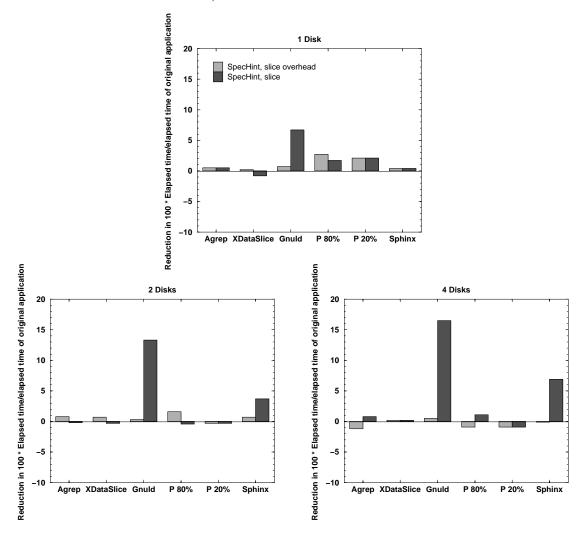

|   |     | 8.2.4    | Experimental slicing                            | . 148 |

|   |     |          | Combining techniques                            |       |

|   | 8.3 | Projecti | ng future performance                           | . 151 |

|   | 8.4 |          | rent applications                               |       |

|   |     |          | Impact of decreasing spare processing resources |       |

|   |     | 8.4.2    | Impact of increasing resource contention        | . 157 |

|   | 8.5 |          | rmation overhead                                |       |

|   | 8.6 | Summa    | ry                                              | . 161 |

| 9 | Con | clusions |                                                 | 163   |

|   | 9.1 | Disserta | ation summary                                   | . 163 |

|   | 9.2 | Contrib  | utions                                          | . 165 |

|   | 9.3 | Future v | work                                            | . 165 |

viii CONTENTS

# **List of Figures**

| 2.1 | Potential benefit of I/O gap on application performance    |

|-----|------------------------------------------------------------|

| 3.1 | A simple program                                           |

| 3.2 | Potential to improve performance                           |

| 3.3 | A simple data-dependent program                            |

| 3.4 | Another data-dependent program                             |

| 3.5 | A program that defies prefetching                          |

| 4.1 | Lazy resynchronization policies                            |

| 4.2 | Selecting more effective values                            |

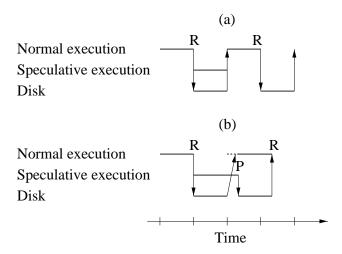

| 5.1 | Scheduling speculative execution 61                        |

| 5.2 | Execution path and correctness probability                 |

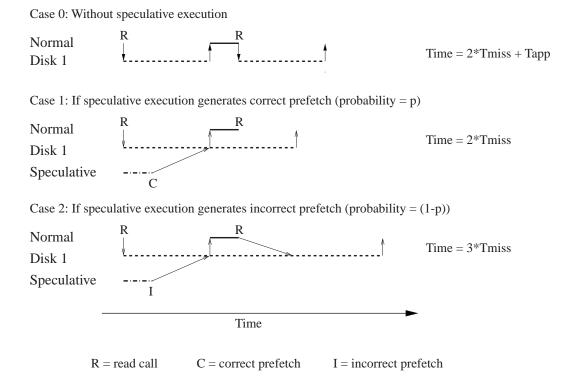

| 5.3 | Incorrect prefetches with a single disk                    |

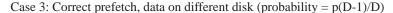

| 5.4 | Incorrect prefetches with multiple disks                   |

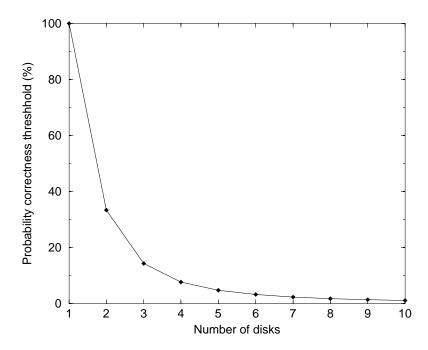

| 5.5 | Correctness probability threshold                          |

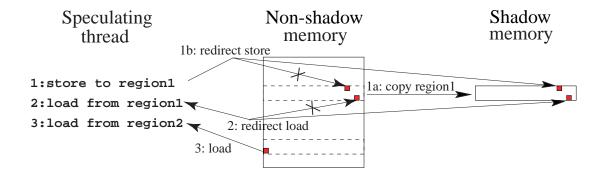

| 6.1 | Software copy-on-write                                     |

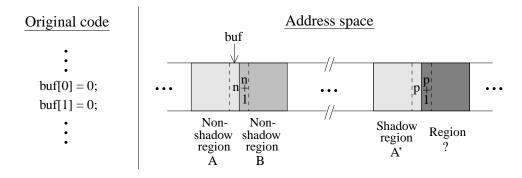

| 6.2 | An addressing issue                                        |

| 6.3 | Modifying a system call in shadow code                     |

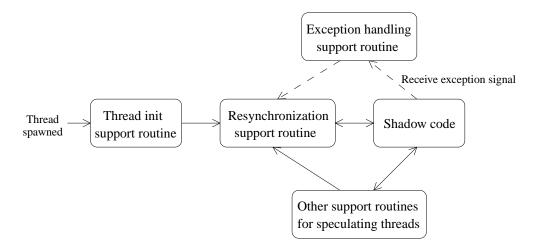

| 6.4 | Control flow of speculating thread                         |

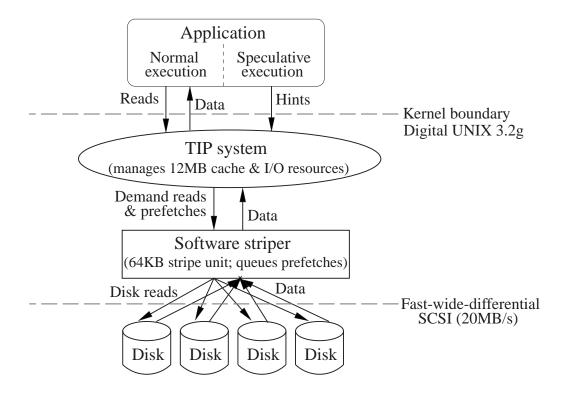

| 7.1 | Evaluation environment                                     |

| 7.2 | Using the SpecHint tool to produce speculating executables |

| 7.3 | Inlining TIP hint call to manually modify Agrep            |

| 7.4 | Loop distribution to manually modify XDataSlice            |

| 7.5 | Loop inlining and splitting to manually modify Gnuld       |

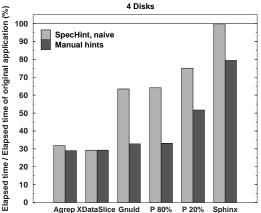

| 8.1 | Single application performance of the SpecHint design      |

| 8.2 | Hint correctness prediction and filtering                  |

| 8.3 | Simple value prediction                                    |

| 8.4 | Experimental slicing                                       |

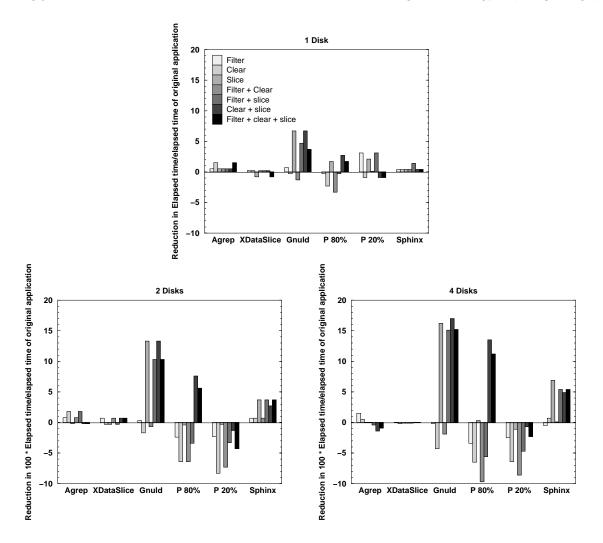

| 8.5 | Combined techniques                                        |

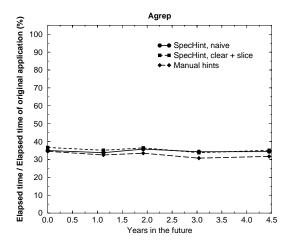

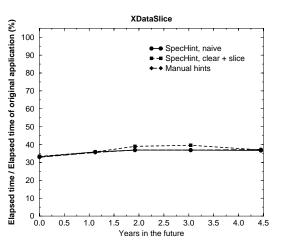

| 8.6 | Projected performance of speculative execution             |

x LIST OF FIGURES

| 8.7 | Projected performance of speculative execution (cont.) |

|-----|--------------------------------------------------------|

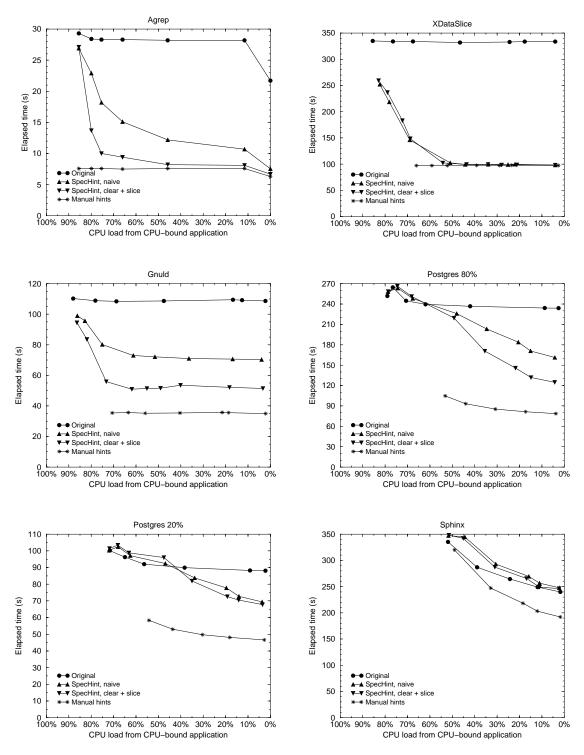

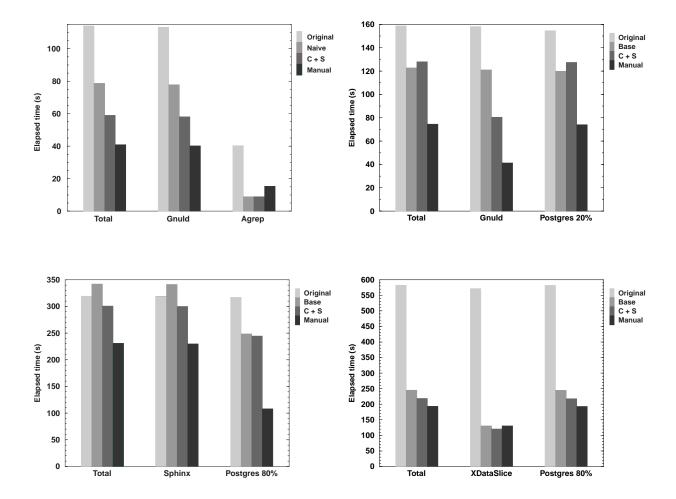

| 8.8 | Concurrent CPU-bound application                       |

| 8.9 | Multiple disk-bound applications                       |

# **List of Tables**

| 2.1        | TIP interface                                                |

|------------|--------------------------------------------------------------|

| 3.1        | Time between read calls                                      |

| 6.1        | Copy-on-write and stack pointer checks                       |

| 7.1<br>7.2 | Summary of benchmarks                                        |

| 8.1        | Single application performance of the SpecHint design        |

| 8.2        | Hinting performance of the SpecHint design                   |

| 8.3        | Prefetching performance of the SpecHint design on one disk   |

| 8.4        | Prefetching performance of the SpecHint design on four disks |

| 8.5        | Cache performance of the SpecHint design on one disk         |

| 8.6        | Cache performance of the SpecHint design on four disks       |

| 8.7        | CPU and memory performance of normal execution               |

| 8.8        | Performance characteristics of speculative execution         |

| 8.9        | Performance with minimal execution state updates             |

| 8.10       | Hinting performance with filtering                           |

|            | Combined techniques                                          |

|            | CPU load of benchmarks                                       |

|            | Transformation overhead                                      |

# Chapter 1

# Introduction

Many applications often require data that is too large or too infrequently used to be found in memory. Examples of such applications range from common utility programs (like text search or file archiving tools), to database and data mining applications, to a wide variety of scientific and engineering applications. In order to access their data, these applications often issue large numbers of disk requests. Unfortunately, because disks are much slower than processors, these applications often end up wasting a substantial fraction of their execution times waiting for disk requests to complete. Moreover, since the rate at which disks can satisfy requests is increasing slowly relative to increases in processing speeds, this performance problem is expected to worsen.

One way to address this *I/O gap problem* is *I/O prefetching*. Rather than fetching data from disk on demand (i.e. only after an application has attempted to access the data), I/O prefetching involves fetching data from disk in anticipation of an upcoming attempt to access the data. The potential benefit of an I/O prefetch is that, if the anticipated attempt occurs, then the prefetch will have hidden some or all of the time it takes to fetch that data from disk, so the accessing application will waste less time stalled on I/O.

Prior research has demonstrated that, by reducing I/O stall time, I/O prefetching can dramatically improve the performance of a wide range of I/O-intensive applications. In practice, however, it can be difficult to extract such improvements. On one hand, I/O prefetching will yield little or no benefit if too little data is prefetched, or data is prefetched too late, to hide much disk fetch time. On the other hand, if the wrong data is prefetched, or data is prefetched prematurely, then I/O prefetching can degrade rather than improve performance. In particular, since I/O prefetching consumes disk bandwidth, a prefetch could delay other disk requests. Also, since I/O prefetching consumes memory to buffer the prefetched data, a prefetch could cause useful data to be evicted from memory prematurely, so that additional I/O requests are required to fetch that data back into memory. Therefore, prefetching effectively requires both accurate and timely identification of what data will be accessed when.

One approach to obtaining accurate and timely prefetching information is for programmers to implement or modify applications such that, when executed, the applications will issue prefetching calls specifying this information. However, this manual approach can require a substantial amount of programming and debugging effort. Furthermore, a programmer could modify an existing application only if the application's source code is available. Consequently, in practice, very few applications are implemented or subsequently modified to provide such information.

Therefore, a more realistic approach would be to somehow extract prefetching information automatically. Unfortunately, while a variety of automatic approaches have been proposed, there are many applications that cannot be handled by any of the existing approaches. Existing approaches fall in one of three categories: pattern-based approaches, history-based approaches, and static analysis approaches. Common access pattern approaches generate prefetches according to some fixed set of pre-identified access patterns. These approaches can be very effective for applications whose data accesses conform to one of their pre-identified patterns, but cannot improve the performance of other applications. History-based approaches generate prefetches based on observing the sequence of prior data accesses. These approaches may be effective for prefetching a previously observed sequence of data accesses, but will not, for example, be able to generate accurate prefetches for an access sequence that differs greatly from any which have previously been observed. For this and other reasons, history-based approaches tend to be ineffective for applications whose data accesses depend on inputs that usually vary from run to run. Finally, in static analysis approaches, a compiler (or other tool) adds prefetching calls to an application based on pre-runtime analysis of the application's source code. These approaches are limited by the compiler's ability to transform an application such that data will be prefetched substantially in advance of when the application will attempt to access it, an ability which is hampered by the dependence of applications on data values that are determined only during their execution. The difficulty of accomplishing this has thus far constrained static analysis approaches to looping array codes.

This dissertation puts forth a new approach to automating the extraction of I/O prefetching information called the *speculative execution approach*. This approach exploits technology trends, which are providing an increasing abundance of processing and memory resources, to avoid many of the disadvantages of previously existing approaches. In particular, unlike common access pattern approaches, it is capable of prefetching arbitrary access sequences. Unlike history-based approaches, it is capable of prefetching access sequences that have never previously been observed. And, unlike static analysis approaches, it does not require any sophisticated pre-runtime analyses.

## 1.1 The speculative execution approach

An execution is *speculative* if it depends on one or more possibly incorrect data values, and may therefore be inaccurate. Most processors perform speculative execution to more efficiently handle conditional branch instructions and other sources of pipeline stall. This dissertation advocates performing software-level speculative execution to reduce I/O stall time.

Specifically, this dissertation proposes that, to generate I/O prefetches for an executing

application, we should add a new execution of that application's code. This added execution should run ahead of the application's *normal* (i.e. non-speculative) execution by skipping some operations, like attempts to access data that is not in memory. Skipping these operations will probably cause the added execution to use some data values that differ from the data values that will be used during the normal execution. The fundamental hypothesis behind the speculative execution approach is that, despite these incorrect data values, the data accesses encountered during the added speculative execution will often be the same as the data accesses that will occur during subsequent normal execution. Thus, whenever the speculative execution encounters an access to data that is not in memory, it may be able to reduce the normal execution's I/O stall time by issuing a prefetch for that data.

For the speculative execution approach to be successful, it is not sufficient for speculative execution to be capable of generating accurate prefetches for the data that will be accessed during subsequent normal execution. It is also necessary that speculative execution generate these prefetches early enough to hide a substantial amount of disk fetch time. In order to accomplish this, speculative executions must be provided with an adequate and timely amount of processing, memory and I/O resources. Therefore, the approach is also based on a second hypothesis that there are/will be sufficient resources on current/future systems for this purpose.

Finally, a number of factors will affect the practicality of the approach. For example, since programmer time is an expensive commodity, there needs to be a way to add speculative executions automatically. As another example, since people are unlikely to use an approach that causes their applications to produce erroneous results or otherwise malfunction, there should be a way to add speculative executions that will not cause such malfunctions.

### 1.2 Thesis statement

My thesis is that:

- For a wide range of applications, speculative execution of the application's code could be leveraged to accurately predict what data the application will access in the future early enough for I/O prefetching to provide substantial performance benefits.

- For a wide range of applications, such speculative execution could be added automatically in a manner that will not cause the application to malfunction.

## 1.3 Dissertation roadmap

This dissertation raises and answers several basic questions. Can speculative execution of an application's code generate accurate predictions of what data will be accessed by the application? What limits the ability of speculative execution to generate accurate predictions? What resources are needed by speculative execution to generate these predictions early enough for effective prefetching? Are these resource needs reasonable on current and

future systems? How can adding speculating executions change the behavior of a system? Can we automate the addition of speculative executions in a manner that will not cause applications to malfunction? Can such a design for adding speculative executions deliver substantial performance benefits for real-world applications? To what degree can this approach automatically deliver the potential performance benefits of I/O prefetching? And, relative to prior approaches to automating I/O prefetching, what are the advantages and disadvantages of the speculative execution approach?

To answer these questions, the dissertation discusses the advantages and limitations of this approach to automatically generating I/O prefetches. It also discusses the major issues and tradeoffs in developing a design for automatically adding speculative executions. Interlinked with this discussion, the dissertation provides an in-depth investigation of *SpecHint*, a particular design and implementation. Finally, the dissertation describes an evaluation of SpecHint using five, real-world data-intensive applications. This evaluation demonstrates the strengths and weaknesses of the speculative execution approach and the SpecHint design and implementation.

This dissertation demonstrates that we can automate the speculative execution approach in a manner that is guaranteed to cause no malfunctions for a wide range of applications. The discussions argue and the evaluation affirms that speculative execution is capable of extracting accurate I/O prefetching information, and that the resources needed to perform speculative execution should be reasonable on both current and future systems. The dissertation also argues and affirms that the degree to which the speculative execution approach will be successful is highly application-dependent. In particular, it can be limited by application-specific dependencies of normal execution on data that is not available during speculative execution and/or by application-specific resource requirements for effective speculative execution. The evaluation demonstrates that the speculative execution approach, and the SpecHint design and implementation in particular, can produce impressive performance benefits on a variety of real-world applications. In addition, a simulation experiment indicates that, if current technology trends continue, then these benefits should not decrease, and may even increase for some applications, on future systems. The evaluation also demonstrates that the approach can sometimes deliver benefits comparable to those that could be obtained by manually modifying applications to issue prefetch calls.

The rest of this dissertation is organized as follows. In Chapter 2, I describe the trends which motivate this work and provide background material on I/O prefetching. I then describe and contrast my approach to prior approaches to automating I/O prefetching, and prior uses of speculative execution.

In Chapter 3, I describe the speculative execution approach in greater detail, discussing its potential advantages and disadvantages relative to prior approaches. I also describe the factors which can limit the success of this approach and reason that these factors will not prevent the approach from providing substantial benefits in many interesting situations. I then set the framework for the design discussion in the next three chapters. In particular, I discuss the three basic goals that should be shared by any design for adding speculative execution, sketch out a few possible designs, argue that no single design will be ideal in

5

all situations, and introduce the SpecHint design (the design I developed and implemented in the course of this dissertation work in order to investigate the speculative execution approach).

In Chapters 4, 5 and 6, I describe the major design issues related to each of the three basic design goals. Chapter 4 focuses on effectiveness, the ability of a design to extract timely and accurate prefetching information. Chapter 5 focuses on low overhead, where overhead is defined to be an increase in the elapsed time of a normal execution. Chapter 6 focuses on safety, the degree to which a design ensures that it will not cause applications to malfunction. Each chapter is split into two sections. The first section describes the issues that should be considered in developing a design for adding speculative execution. The second section describes how these issues are addressed in the context of the SpecHint design and implementation.

In Chapter 7, I describe my experimental testbed and the benchmarks I use to evaluate the SpecHint design and implementation. This includes a discussion of how much effort was needed to manually modify the benchmark applications to perform explicit prefetching. In Chapter 8, I describe my evaluation of the SpecHint design and implementation.

Chapter 9 concludes the dissertation with a summary of its key contributions. The chapter also includes some possible avenues for further research stemming from this work.

# **Chapter 2**

# **Background**

In this chapter, I describe the problem that motivates this dissertation work, prior attempts to address this problem, and the reasons why further work is required. Section 2.1 begins by quantifying the huge and growing gap between processing speeds and disk access times. It provides background material to explain why the gap is expected to continue growing, and presents a simple example to illustrate how this growing gap creates a serious performance problem. One way to address this *I/O gap problem* is to apply a well-known technique for hiding disk access times called I/O prefetching. Section 2.2 begins by describing how I/O prefetching can improve performance dramatically. It then explains why I/O prefetching is a difficult technique to apply successfully. Next, it describes previous work on I/O prefetching and why that work is not always sufficient. This dissertation explores a new approach to I/O prefetching based on a technique called speculative execution. Section 2.3 describes the ways speculative execution has been used in the past and how they differ fundamentally from the approach explored in this dissertation. Finally, Section 2.4 briefly discusses other ways of addressing the I/O gap problem.

### 2.1 The I/O gap problem

Purchase a new desktop computer today, and its processor speed will probably range from 1 to 2 GHz.<sup>1</sup>. In contrast, the average time it takes to retrieve a modest amount of data from disk ranges from 5.6 to 12.6 ms.<sup>2</sup> In other words, the average disk access time on a new system will probably be equivalent to more than 6 million processing cycles. Therefore, an application that needs to wait for data to be retrieved from disk will progress much slower than it otherwise could. Even worse, this gap between processing speeds and disk access times is widening. While processor speeds are increasing at an impressive rate of 58% a year [20], disk access rates are only increasing at about 8% a year [18].

<sup>&</sup>lt;sup>1</sup>This range comes from the offerings at www.dell.com and www.compaq.com as of December 1, 2001

<sup>&</sup>lt;sup>2</sup>This range comes from the offerings at www.seagate.com and www.quantum.com as of December 1, 2001.

To understand why such a huge gap exists, and why it is expected to continue growing, it is helpful to have a basic understanding of how disks work. A disk drive contains a controller, some buffer memory, a stack of disk platters mounted on a central spindle that rotates at some rate (the *spindle speed*), and a set of disk heads (one for each side of each platter) mounted on an actuator assembly. Data is stored on both sides of each platter in concentric tracks, and the actuator assembly can pivot to position a head over any track. When the controller receives a request for some data, it first checks to see whether that data is in the disk's buffer memory. If so, the controller can begin transferring the data to main memory immediately. Otherwise, the time it takes to service the request (disk access time) is the sum of a relatively negligible amount of controller overhead time plus the time to pivot the actuator assembly such that a head is positioned over the track where the data resides (seek time), the delay before the data begins rotating beneath that head (rotational latency), and the time it takes for all of the requested data to pass beneath the head so that it can be read (transfer time). Disk transfer rates have been improving at a respectable 40% a year, largely due to 30% per year improvements in linear density (the density of bits on a track) [18]. However, most disk requests are small enough that disk access times are dominated by *positioning times* (the combination of seek times and rotational latency) rather than transfer time. Unfortunately, as just described, positioning times depend on mechanical technology, which is slower and improves much less rapidly than the solid-state technology that makes up processors, memory and most other components of computer systems.

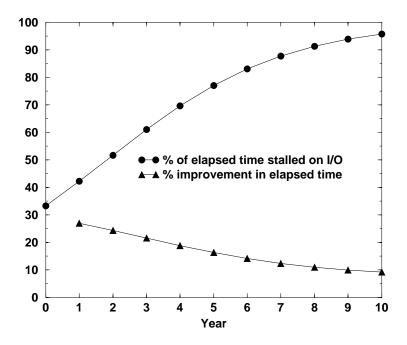

To illustrate how the widening gap between processing speeds and disk access times can affect application performance, consider a hypothetical single-threaded application that, on a current system, spends twice as much time processing as waiting for data to be retrieved from disk. Assume that (in accordance with current trends) the processor speed increases by 58% per year, and the disk access rate increases by 8% per year. Each year, in accordance with Amdahl's Law<sup>3</sup>, the application's elapsed time will decrease by smaller amounts as it spends an increasing proportion of its time stalled on I/O. Figure 2.1 shows both the decrease in elapsed time and the fraction of the new elapsed time that will be spent stalled on I/O, for ten years of annual upgrades. Notice that, after only the second yearly upgrade, the application will be spending more than half of its time stalled on I/O and, after only the eighth yearly upgrade, the application will be spending more than 90% of its time stalled on I/O. Moreover, with the eighth yearly upgrade, the application's elapsed time will decrease by only 11%. In contrast, the elapsed time of an application which performs no I/O would decrease by 58% with each year's upgrade. This example highlights how the widening gap between processor and disk access speeds will hamper the performance of applications that need to access data on disk, causing them to be increasingly disk-bound and increasingly incapable of deriving benefit from advances in processor technology.

The simplified example in the last paragraph ignores possible effects of other trends in computing systems. For example, it has been predicted that increasing memory sizes

<sup>&</sup>lt;sup>3</sup>A generalized restatement of Amdahl's Law is that the performance improvement which can be obtained from some faster mode of execution is limited by the fraction of time that the faster mode is used.

Figure 2.1: Effect of the growing gap between processor speeds and disk access times on the performance of a hypothetical single-threaded application that currently spends twice as much time processing as waiting for disk reads to complete. This graph assumes that, each year, the processor speed increases by 58%, and the disk access rate increases by 8%.

would obviate concern about disk access times by greatly decreasing the percentage of data requests that would require disk access (i.e. the *miss rate*). Several file trace studies have not upheld this predictions, however. In particular, file trace studies from 1985 [39], 1991 [2] and 1999 [65] reported very similar miss rates (approximately 40%), despite the passage of 14 years and the corresponding increase in memory sizes on the traced machines. Although these particular studies were conducted in different computing environments (the BSD, Sprite [38] and NT file systems, respectively), and are not representative of all user communities, they indicate that increasing memory sizes will not automatically hide the performance impact of disk access times. This argues that there will be a growing need for techniques that will explicitly address the I/O gap problem.

### 2.2 I/O prefetching

Prefetching is a well-known technique for hiding data access latency. Prefetching involves fetching some data from a higher-latency locale to a lower-latency locale (from main memory to processor caches, for example) before the data is accessed. Prefetching can improve

performance if prefetched data is subsequently accessed by allowing these accesses to experience only the lower latency. A conceptually simple idea, prefetching is complicated by resource constraints. For example, prefetching consumes bandwidth to transfer the data between the higher and lower latency locales, and buffer space in the lower latency locale to hold the data in anticipation of a subsequent access. Since there are typically competing ways to use these limited resources, prefetching can inadvertently harm rather than help performance.

In this dissertation, I/O prefetching refers to prefetching data from magnetic disks to main memory. Section 2.2.1 shows why I/O prefetching is an appealing technique by describing its potential to produce dramatic performance improvements. Section 2.2.2 shows why I/O prefetching should only be used carefully by describing how I/O prefetching can hurt performance. The challenge with leveraging I/O prefetching is how to extract some of the potential performance improvements described in Section 2.2.1 rather than inadvertently hurting performance as described in Section 2.2.2. Previous research [42, 3] has demonstrated that this problem can be subdivided into two parts: 1) figuring out what data will be accessed when, and 2) assuming the former, figuring out when to prefetch what, and what to eject from memory whenever space is needed (e.g. to hold newly fetched data). This dissertation focuses on the first part of the problem, leveraging prior work that addresses the second part of the problem. Section 2.2.3 summarizes the issues and prior work on addressing the second part of the problem. Section 2.2.4 discusses prior work on the first part of the problem, and why it is not sufficient.

### 2.2.1 Potential benefits of prefetching

I/O prefetching improves performance by hiding disk access times from applications. In particular, if an application attempts to access some data while it is being prefetched, then the application will experience only the remaining disk access time. Even better, if an application attempts to access some data after it has been prefetched, while the data is still in memory (i.e. still *cached*), then all of the disk access time will be hidden from the application.

To illustrate the extent to which I/O prefetching can improve application performance, consider a hypothetical application that processes for P time units between each of N calls to read data that is not cached when the application begins executing. For simplicity, assume that there are no other executing applications, and that the time it takes for a disk to service an I/O request is fixed at  $T_{disk}$  time units.

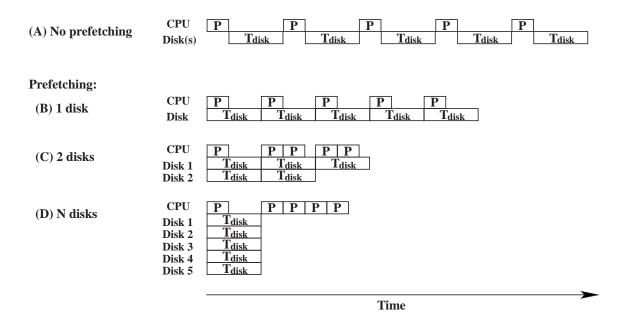

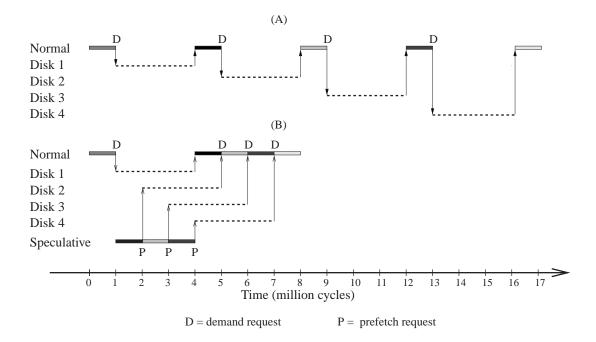

First, consider the case in which all the application's data resides on a single disk. Each of the application's read calls will trigger an I/O request. Therefore, the application will alternate between processing and stalling on the disk, as shown in Figure 2.2A, and the application's total execution time will be  $N(P+T_{disk})$  time units. To determine the potential benefit of prefetching, assume that, as soon as the application begins executing, a prefetch is issued for the data specified by each of the application's N read calls.<sup>4</sup> In this sce-

<sup>&</sup>lt;sup>4</sup>If an application's data can be prefetched before the application begins executing, then the potential

Figure 2.2: This figure illustrates the potential benefit of I/O prefetching. The hypothetical application issues N read calls for uncached data, processing for P cycles between read calls. (A) With no prefetching, the application will take  $N(P+T_{disk})$  time units to execute, regardless of the number of disks. To show the potential benefit of prefetching, assume that prefetches are issued for all the data specified in the application's read calls as soon as the application begins executing. (B) With a single disk, the prefetches can be overlapped with computation. (C) With multiple disks, the potential performance improvement is much larger because, in addition to overlapping prefetching with computation, it may be possible to concurrently service multiple prefetches.

nario, when the application begins executing, the disk will begin servicing the first prefetch immediately and will then proceed to service the remaining prefetches one after another. Therefore, as shown in Figure 2.2B, the performance of the application will be improved because the I/O system will fetch the application's data in parallel with the application's processing. Specifically, prefetching will be able to decrease the application's execution time to the greater of NP and  $NT_{disk}$ , i.e. by as much as a half.

Even greater performance improvements are possible if an application's data is spread across multiple disks. To illustrate this, reconsider the same application but assume that the application's data is spread across D ( $\leq$ N) disks such that each call in a sequence of D read calls specifies data on a different disk. If no prefetches are issued, each of the application's read calls will trigger an I/O request. Therefore, the application's execution time will be exactly as it was with a single disk (i.e. Figure 2.2A still applies). If, instead, we assume that prefetches are issued as described in the last paragraph then, when the application begins executing, each of the D disks will begin servicing prefetches. Therefore, as shown

benefit of prefetching may be even greater. This is one advantage of dynamic history-based prefetching approaches, which are discussed in Section 2.2.4.2.

in Figure 2.2C, the I/O system will service D prefetches in parallel with one another, as well as with the application's processing. This will allow the application's execution time to be decreased to:

$$\begin{cases} N*P & \text{for } P \geq T_{disk} \\ T_{disk} + (N-1)*P & \text{for } T_{disk} \geq P \geq T_{disk}/D \\ \lceil N/D \rceil * T_{disk} + ((D-1)modN)*P & \text{for } P < T_{disk}/D \end{cases}$$

Therefore, for example, for an application whose data is spread over many disks (i.e.  $D \ge 10$ ) and which performs little processing between read requests (i.e.  $P << T_{disk}$ ), reductions in execution time of 90% or more are plausible.

In addition to showing that the potential benefits of prefetching can be dramatic, the preceding example highlights both how prefetches can allow applications to exploit multidisk I/O systems more fully and, conversely, how multi-disk I/O systems enable prefetching to be more effective. In particular, since read requests are blocking, a single-threaded application can only have one I/O request outstanding at any time. Moreover, the vast majority of read requests are of a modest size such that the data specified by a single request does not span multiple disks. Therefore, as illustrated in Figure 2.2A, a single-threaded application executing by itself is unlikely to derive substantial performance benefit from having its data distributed across multiple disks because it will never exercise more than one disk at a time. In contrast, prefetching on behalf of an application will increase the frequency with which there are multiple I/O requests outstanding at the same time. If data is well-distributed across multiple disks (where striping [47] generally suffices to produce such a distribution), it is likely that different requests can often be serviced in parallel by multiple disks. Therefore, prefetching increases the degree to which applications can exploit multiple disks.

Conversely, as described above, if an application's processing time between disk requests is less than the disk access time – which, even if not true today, will be increasingly likely given the widening gap between processing speeds and disk access times – then the benefit of prefetching will be limited by the number of disks. For example, from the discussion above, for an application in which P is only 10% of  $T_{disk}$ , the maximum potential decrease in the application's execution time is only about 9% if the data resides on a single disk. However, assuming that the application issues 20 read requests, the maximum potential decrease in the application's execution time is 54% if the data resides on two disks, 76% if the data resides on four disks, and 87% if the data resides on ten disks. Notice that prefetching cannot decrease the total amount of data that must be fetched from disk. It can improve performance only by fetching that data earlier than it would otherwise be fetched. Therefore, prefetching may not be able to improve the performance of a multi-threaded application or a multi-tasking system that already fully utilizes the I/O system (i.e. keeps all disks busy at all times) because causing some data to be fetched earlier would simply result in other data being fetched later.

The benefit of prefetching can actually be somewhat greater than described in the preceding discussion. In focusing on how prefetching can hide disk access times from applications, the preceding discussion ignored two ways that prefetching can improve perfor-

13

mance by reducing the aggregate time to fetch the necessary data from disk. The first of these leverages the fact that disks can reorder queued requests to decrease their positioning times using any of a variety of disk scheduling algorithms [14]. As discussed above, a typical single-threaded application executing by itself will not benefit from disk scheduling because there will never be more than one request queued at any time. By increasing the depth of disk queues, prefetching increases the potential for a reordering of those requests that will reduce their positioning times. The second of these targets the fact that there is a cost to issuing a request to the I/O system. Since prefetches, unlike demand fetches, are not blocking, it is reasonable to accumulate multiple prefetches, batching them into a single request to the driver in order to reduce driver overhead [43]. Finally, although not considered in this dissertation, I/O prefetching can also improve performance in terms of energy consumption. In particular, by batching I/O requests more closely in time, prefetching can reduce the number of disk spin ups and/or how long disks are powered.

### 2.2.2 Potential risks of prefetching

While the potential benefits of I/O prefetching are large, prefetching can also hurt application performance as a side effect of increasing contention for a limited resource. This is particularly likely when a prefetch consumes resources without any possible benefit because the prefetched data is not subsequently accessed. There are two primary ways in which a prefetch can hurt application performance.

First, a prefetch can occupy an actuator assembly, delaying demand requests. Current disks are not preemptive; if a demand request is issued to a disk while a prefetch is being serviced, the demand request will not be serviced until the prefetch has completed. Furthermore, current disks cannot differentiate between prefetch requests and demand requests; once a prefetch is issued to a disk, the disk will schedule it no differently than a demand request. If a disk reorders queued requests to reduce aggregate positioning time, it may even reorder a demand request behind a subsequently issued prefetch request. Notice that these hardware limitations make it impossible for any software prefetching scheme to guarantee that it will never hurt performance (unless it can determine when demand fetches will occur, so that it can appropriately limit its activity). One heuristic for bounding the consequences of these hardware limitations is to modify operating systems and device drivers such that they allow a prefetch request to be issued to a disk only when there is at most one request (demand or prefetch) already queued at the disk [43].

Second, since prefetched data competes for space in main memory, applications may end up issuing more I/O requests, and experiencing more I/O latency, to access their data than if no prefetching had occurred. Before a prefetch is issued to disk, space must be reserved in memory to hold the data that will be read from disk. Unless there is sufficient unused memory, reserving this space will require ejecting some data from memory. In addition, until the prefetched data is accessed or ejected from memory, it will occupy space that would otherwise have been available to hold some other data. By shrinking the pool of memory from which space is reserved for subsequently fetched data, prefetched data will

indirectly cause the ejection of data that would have otherwise remained in memory. In either case, if the data that is ejected from memory due to a prefetch have been accessed before it was ejected had the prefetch not taken place, then the prefetch will cause that subsequent access to require an I/O that would have been unnecessary had the prefetch not occurred.

### 2.2.3 Prefetch scheduling and cache management

If an application writer wishes to improve the performance of an application by modifying the application such that it issues I/O prefetches for the data it will subsequently access, the mechanisms offered by current operating systems are poorly suited to the task [42]. In particular, the most suitable mechanism offered by most current operating systems is an asynchronous read call. Asynchronous read calls are a poor prefetching mechanism because issuing such a call causes the operating system to immediately allocate space in memory, and issue a disk request, for any uncached data specified by the call. This presents the application writer with a difficult optimization problem because a particular placement of asynchronous calls in the application which substantially improves performance in one execution environment may be harmful in another. For example, a placement that improves the application's performance when the application is executed on a machine with a certain amount of memory may hurt performance on a machine with less memory because (as described in the previous section) contending for a smaller pool of memory could result in the prefetches causing useful data to be ejected from memory such that the application ends up spending more time stalled on I/O. The same effect could appear even when re-executing the application on the original machine if, during the re-execution, there are concurrently executing applications competing for space in memory. To address this problem, researchers [42, 5] have argued for a separation between exposing what data will be accessed in the future, and allocating shared machine resources in an attempt to derive benefit from that information. Exposing future data accesses will be discussed further in the next section. This section focuses on how a system might manage its I/O and memory resources, given at least partial information about what data will be accessed in the future.

Given some such information, the two main policies that the system can control in striving to extract the greatest benefit from this information are: 1) the prefetch scheduling policy, i.e. when to initiate a prefetch for some data (which typically requires pre-allocating sufficient memory to hold that data before issuing a disk read request), and 2) the cache ejection policy, i.e. what to eject from memory whenever more space needs to be allocated (to satisfy a demand or prefetch request). The challenge in developing a prefetch scheduling policy is how to schedule prefetches such that they are early enough to hide I/O latency entirely, while recognizing when prefetches should be issued later in order to avoid causing ejections from memory that would end up hurting performance. The challenge in developing a cache ejection policy is how to identify what data in memory can be ejected with the least performance penalty.

As discussed above, current operating systems schedule prefetches as if they were de-

15

mand fetches, i.e. without considering what data they cause to be ejected from memory. The cache ejection policy used by most operating systems approximates the least recently used (LRU) policy. With LRU, when the system needs another cache block, it will eject the data which has not been accessed for the longest time. This policy exploits temporal locality in data accesses (the observation that, in general, data that has been accessed recently is likely to be accessed in the near future) and, while a mismatch for some access patterns, is known to be fairly effective in general. Prior work [43, 3, 4, 24, 62] has proposed a variety of algorithms for leveraging more explicit information about what data will be accessed in the future. Because the system implemented and evaluated in this dissertation takes advantage of TIP2 [43], the rest of this section focuses on TIP2, hereafter referred to simply as "TIP". In particular, Section 2.2.3.1 briefly describes TIP, and then discusses its weaknesses, and how these affect the work described in this dissertation.

#### 2.2.3.1 TIP

The TIP informed prefetching and caching system [43, 41] is an operating system extension that enables processes to indicate what data they will access in the future and, based on this information, attempts to optimize usage of the buffers allotted to the file cache. Specifically, TIP allows each process to generate (by issuing system calls) a single stream of disclosure hints, where each disclosure hint specifies some file data. TIP incorporates a system performance model that allows it to estimate, for each hint, the benefit of prefetching the data specified by that hint at any given time. TIP also uses the model to estimate the cost of ejecting data from the hinted cache, which consists of the buffers in the cache which contain data that is specified by a hint, and the cost of shrinking the LRU cache, which consists of all other buffers in the cache. The latter estimate also depends on a dynamic prediction, derived by observing the stream of file accesses on the system, of how the hit rate of the LRU cache would change if the size of the LRU cache were changed. TIP keeps track of the hint for uncached, unprefetched data that has the largest estimated benefit, and issues the corresponding prefetch once that estimated benefit is larger than the estimated cost of taking the appropriate number of buffers from the hinted cached and/or the LRU cache.

Prior work [41] has demonstrated that TIP can dramatically reduce the execution times of I/O-intensive applications that issue appropriate disclosure hints. For example, it was demonstrated that TIP can reduce the elapsed times of six real-world, I/O-intensive benchmarks executed on a four-disk system by 12% to 72%. However, to obtain these results, it was necessary to manually modify the source code of the benchmark applications so that they would issue appropriate disclosure hints.

Assuming that processes somehow issue disclosure hints, the performance of TIP hinges on the assumptions which underly its system performance model. The most questionable of these assumptions are that: 1) the system supports an infinite amount of I/O parallelism, and 2) a process's hint stream exactly specifies the data that the process will access in the future, in the order that the process will access that data. Two other assumptions in TIP are also questionable. First, TIP assumes that, once prefetched data is no longer specified by

any hints, it should simply be added to the tail of the LRU cache's LRU queue. Second, TIP enables processes to cancel hints, but assumes that the underlying system does not allow TIP to cancel prefetches.

TIP's assumption that the system supports an infinite amount of I/O parallelism has several consequences. One is that TIP issues prefetches assuming that prefetch requests will never delay demand requests (which is not the case on current systems for the reasons discussed in Sections 2.2.2 and 2.2.3). In evaluations of the TIP system, this behavior was approximated by a prefetch-aware software striper (described in Section 7.1.1). The assumption of infinite amounts of I/O parallelism also has two consequences that cannot be addressed simply by modifying the systems underneath TIP. First, TIP may not issue prefetches early enough to hide I/O latency completely when there is contention for I/O resources (i.e. if disks have demand requests or other prefetch requests queued). Second, TIP is not capable of exploiting variations in fetch time to hide more I/O latency. For example, assume that data block A is on a lightly loaded disk while data block B is on a heavily loaded disk, so that it would take a much longer time to fetch B from disk than to fetch A from disk. Assume there is a single hint stream, in which A is before B. In this situation, the optimum performance may be achieved by ejecting A to initiate a prefetch for B (possibly initiating a prefetch for A at a later time) because, due to the variation in fetch times, the amount of I/O latency that will be hidden by initiating the prefetch for B earlier is greater than the amount of I/O latency that will be added by re-fetching A at a later time. Since TIP's system performance model does not consider variations in fetch time, it will miss this opportunity.<sup>5</sup>

Unsurprisingly, TIP may make suboptimal prefetching and caching decisions if the hint stream contains incorrect or mis-ordered hints, or is missing hints. In addition, the implementation of TIP makes it possible for incorrect or mis-ordered hints to prevent the process from benefiting from subsequent hints. In particular, there are only two ways to remove a hint from a hint queue; a hint will be removed from its hint queue if the corresponding process issues a matching read request when the hint is at the head of its queue, or if the hint is explicitly cancelled. The estimated benefit of prefetching the data specified by a hint, however, is dependent on the hint's position in its hint queue. Therefore, incorrect or mis-ordered hints need to be explicitly cancelled for the benefit of subsequent hints in the same hint stream to be correctly estimated. If incorrect or mis-ordered hints are not cancelled, TIP will eventually stop prefetching on behalf of the corresponding process.

Adding prefetched data that is no longer hinted to the tail of the LRU queue may not be optimal because the lack of a hint may be an implicit hint that the data will not be reaccessed. For example, consider a fully hinted process that rapidly streams through a large amount of data (i.e. it never re-accesses data). TIP will add this prefetched data to the LRU queue right after the process accesses it. If no other process accesses this data, then the data will consume space in the cache while it moves through the LRU queue, without providing any value.<sup>6</sup>

<sup>&</sup>lt;sup>5</sup>Subsequent research [24, 62] has proposed solutions to this problem.

<sup>&</sup>lt;sup>6</sup>Subsequent research [62, 8] has proposed solutions to this problem.

Finally, never revoking prefetches is suboptimal because the estimated benefits and costs of prefetching and ejecting different data from the cache changes dynamically. As a simple example, if a hint is cancelled after a prefetch has been issued for the hinted data, then (as far as the system can determine) there is no benefit to prefetching that data. It may be possible to improve performance by choosing a different use for the cache space pre-allocated for that data, or simply by not wasting I/O bandwidth.

As mentioned earlier, the system that I implemented and evaluated in this dissertation work uses TIP. Notice that these shortcomings of TIP can only cause the benefit of my system to be under-estimated relative to an application that does not provide any information about what data will be accessed in the future. Chapter 5 includes a proposal for how to alleviate the effect of sometimes providing imperfect information (which is evaluated in Chapter 8). TIP's need for explicit cancellation of incorrect and misordered hints is handled by my design and implementation, as described in Chapter 4.

Table 2.1 shows the calls in the TIP interface that were used by my system. In particular, there are two ways to provide a disclosure hint, and a single call which explicitly cancels all hints in the calling process's hint queue. These calls do not produce any application-level side-effects – they do not, for example, update file pointers – so inserting them into an application can affect only the performance of the application (not its output). This increases the usability of the interface because it guarantees that (assuming the implementation of TIP is bug-free) no regression testing (or correctness debugging) will be necessary whenever these calls are added to/moved in/removed from an application. (Of course, after any such change, the programmer may wish to do some performance debugging.)

| Ioctl            | Arguments                       | Description                              |

|------------------|---------------------------------|------------------------------------------|

| TIPIO_FD_SEG     | file descriptor, offset, length | disclosure hint                          |

| TIPIO_SEG        | file name, offset, length       | disclosure hint                          |

| TIPIO_CANCEL_ALL | (none)                          | cancel all hints queued for this process |

Table 2.1: Calls in the TIP interface used by my implementation. These calls do not produce any side-effects (like updating file pointers) that restrict how they should be called in an application. I added TIPIO\_CANCEL\_ALL to the original TIP interface to increase the efficiency of hint cancellation. (The original interface only allowed the cancellation of a single hint at a time.)

### 2.2.4 Predicting future data needs

In order to take advantage of any of the algorithms described in the last section, it is necessary to provide information about what data will be accessed in the future. This section discusses prior approaches to extracting such information, and the shortcomings of those approaches.

Perhaps the most obvious approach to exposing this information is to have programmers modify application source code such that it explicitly provides this information, e.g. by issuing the hint calls shown in Table 2.1. To accomplish this, the programmer needs

to understand how an application determines what data it will access. The programmer also needs to identify how to modify the application such that it will provide information about what data it will subsequently access early enough for prefetching to hide a substantial amount of I/O latency. For some applications, both of these steps may be easy. Such a case is described in Section 7.3.1. For other applications, however, one or both steps may be difficult. For example, the code which determines what data the application will access may be spread across many modules, and the code may be ordered in a way that requires substantial reorganization before the appropriate information can be provided early enough to derive substantial benefits from prefetching. Such a case is described in Section 7.3.4. Moreover, while the interface through which the programmer exposes this information may not produce any side-effects that could introduce new bugs into the application, reorganizing code may introduce introduce bugs, so such an effort may also require additional regression testing and correctness debugging. Therefore, manual modification has two major drawbacks. First, it can require a formidable amount of programming and debugging effort. Second, it requires that application source code be available. Given that application source code is often not available, and programmer time is an expensive commodity, it is not realistic to expect that all, or even most, applications that could benefit from I/O prefetching will be manually modified to provide timely and accurate information about what data they will access in the future.

The alternative is for this information to be extracted automatically. Prior work on automating the extraction of information about future data accesses can be divided into three categories: common access pattern approaches, dynamic history-based approaches, and approaches based on static analysis. The rest of this section discusses the approaches in each category. The existing approaches in the first two categories were proposed with simple prefetch scheduling policies and no modification of the system's cache ejection policy. One could imagine, however, changing the prefetches to disclosure hint calls, or some other mechanism, to leverage the existing work (described in the previous section) on prefetch scheduling and cache ejection policies. Therefore, the following discussions focus on the strengths and weaknesses of how the different approaches extract information about future data accesses.

#### 2.2.4.1 Common access pattern

A common access pattern approach relies on having previously identified some small set of access patterns that occurs frequently. The basic approach is for the system to observe the last few accesses, check whether these accesses fits one of the previously identified access patterns and, if there is a fit, begin issuing prefetches for the data that will soon be accessed if future accesses continue to fit that pattern.

For example, one of the most widespread forms of automatic I/O prefetching is the sequential file readahead [10, 35] performed by most file systems. Whenever the file system detects that the last n reads to a particular file requested data sequentially (where n varies by file system, but is generally one or two) it begins prefetching whatever data is next, sequentially, in the file (where the amount of data prefetched also varies by file system).

Readahead exploits the preponderance of sequential reads that have been documented in many file trace studies over the years [39, 2, 65]; for example, a recent study [65] found that almost 86% of read and read/write accesses were within a series of sequential accesses. However, readahead is less effective than one might expect from these figures because it can only help performance when the series of sequential accesses spans multiple blocks in the file cache; otherwise, only the first access could suffer any I/O latency. Therefore, it is ineffective when accessing small files. Largely due to accesses to small files, for example, that same recent study included a graph showing that over 90% of sequential read runs were less than 8 KB in size, which is the cache block size in many systems (including Digital Unix 3.2, my evaluation system).

The other widespread form of automatic I/O prefetching is the page clustering [31] performed by most operating systems. Page clustering differs widely from system to system. As an example, consider a virtual memory system that groups pages in an address space into sets of pages called "clusters". When a page fault occurs, the virtual memory manager generates an demand I/O to fetch the page that was faulted on. With page clustering, it also identifies a cluster to which that page belonged, and generates I/Os to prefetch the other pages in that cluster. One way that page clustering approaches can differ is in how pages are grouped into clusters. If the groups are determined statically, i.e. depending on spatial locality, then the page clustering approach is an example of a common access pattern approach to automating I/O prefetching where the set of pre-identified patterns is spatial locality in memory accesses. If the groups are determined dynamically, i.e. by observing memory accesses, then the page clustering approach is an example of a dynamic history-based approach. Dynamic history-based approaches are discussed in the next section.

Common access pattern approaches have also been proposed for prefetching on behalf of parallel applications. Previous work [26, 34] has identified access patterns that match the accesses performed by many these applications, including complicated patterns like strided accesses.

In general, common access pattern approaches have two major strengths. They can be very effective when the stream of accesses fits one of the pre-identified patterns and, assuming the set of pre-identified patterns is fairly small, they incur little overhead (checking whether the last few accesses fit one of the patterns). However, these approaches have two major weaknesses. First, they cannot help whenever the stream of accesses do not fit any of the pre-identified patterns. Second, they can result in useless prefetching, which can harm system performance as a side effect of increasing resource contention (as discussed in Section 2.2.2), whenever the last few accesses fits a pattern, triggering prefetching, but subsequent accesses do not fit the pattern.

#### 2.2.4.2 Dynamic history

In a dynamic history-based approach to generating I/O prefetches, the system observes the stream of accesses, and possibly some other information. It uses these to form and update a set of prefetching rules, and to determine what data to prefetches (based on those prefetching rules).

One very simple approach [53, 32, 28], sometimes called the "last-successor" approach, is to have the file (virtual memory or database) system track, for each file (page or object), the next file (page or object) accessed the last time that file was accessed. Previous work has shown that this simple approach can correctly predict the next file (page or object) accessed the majority of the time; for example, using traces of file accesses, Kroeger and Long [28] found that this simple approach correctly predicted the next file accessed 72% of the time.

Many more sophisticated approaches have been proposed [60, 40, 6, 16, 32, 28]. Curewitz, Krishnan and Vitter [6] were the first to adapt context modelling techniques generally used for data compression to perform probabilistic prediction of an application's next page fault (or, in an object-oriented database, the next object accessed) based on the sequence of past page faults (or objects accessed). In particular, they used a character-based version of the Lempel-Ziv algorithm and the Finite multi-order context models (FMOC) that originated from prediction-by-partial-match data compressors. Kroeger and Long [27, 28] proposed approaches based on FMOC for predicting the next file that will be accessed. As another example, Griffioen and Appleton [16, 17] proposed an approach in which accesses to files are predicted based on an accumulated graph that tracks, for each file, which files have most often been amongst the next n files accessed, where n is some small number. This approach differs from the two just described in two related ways: 1) it will implicitly predict more than just the next file that will be accessed, and 2) it will capture the fact that an access to file A is often followed by an access to file B even if there is always an access to some other random file between the accesses to A and B so, for example, it may not be as sensitive to the interleaving of processes on a multi-tasking machine. However, Kroeger and Long [28] found that, while conceptually appealing, such an approach may actually perform worse than the last-successor approach.

Dynamic history-based approaches can be very successful when access streams are repetitive. Approaches that predict file accesses are also capable of discovering and exploiting access patterns that span multiple applications. An example drawn from Griffioen and Appleton's paper [16] is that such an approach could implicitly recognize an edit-compile-run cycle for some source tree and prefetch the appropriate compiler, object files, and/or libraries when it notices that a user is editing a source file in that tree.

On the other hand, dynamic history-based approaches have two critical weaknesses. First, they cannot help when the sequence of accesses is non-repetitive. For example, it is unlikely that a dynamic history-based approach could help an application whose accesses depend on its arguments and inputs if those tend to change each time the application is executed. Second, they are limited by the amount of processing cycles and memory resources they can consume before they incur an overhead that outweighs their benefit. To limit the amount of processing cycles and memory they consume, such approaches must limit the types of events they track, the ways in which they analyze these events, and/or the amount of information they retain about these events. There are many examples of how existing approaches constrain their effectiveness as a by-product of how they limit their overhead. For example, the existing approaches for predicting file accesses track open calls rather than (more numerous) read calls. As a result, they cannot help applications which access

21

large files nonsequentially. A similar example regarding existing approaches for predicting accesses to pages is that, rather than tracking memory accesses, such approaches track only page faults. As a result, the information they gather may become useless if the amount of memory available to an application changes (as would probably occur, for example, if there is a change in what other applications are executing).

#### 2.2.4.3 Static analysis

In a static analysis-based approach to extracting information about what data will be accessed in the future, a compiler analyzes the application at compile-time in order to understand the accesses that the application will make when it is executed. The compiler then transforms the application such that it will provide this information whenever it is executed, e.g. by inserting prefetch calls into the application.

Early work by Trivedi [63] proposed using static analysis to insert prefetch calls, but the proposed analysis applied only to looping array codes that could be tiled (loop tiling [70], also called loop blocking, is a compiler transformation that modifies the way a loop is structured in order to, for example, increase access locality). More recent work by Mowry, Demke and Krieger [36] demonstrated static analysis that could insert prefetch calls into a much broader range of looping array codes. This work also advocates adding a run-time layer which will allow applications to quickly detect which of their pages are in memory. The transformed applications use this run-time layer to avoid the overhead of issuing large numbers of prefetch calls for pages already in memory. This work, and follow-on work by Demke and Mowry [8], also demonstrated static analysis that could insert, into the same kinds of applications, release hints indicating pages that will not be re-accessed before they are ejected from memory. This work demonstrated that, by decreasing memory pressure, correct release hints improve the performance of not only the issuing application, but also any concurrent applications.

Theoretically, approaches based on static analysis could deliver the same performance benefit as having expert programmers modify every application's source code such that the applications will issue prefetch calls. In particular, static analysis tools could potentially perform the same transformation as the expert programmers. In reality, however, these approaches have fallen short of this ideal. The problem is that the static analysis necessary for adding I/O prefetching calls can be prohibitively expensive, in terms of computational cost and/or space. In order to hide the latency of a disk request completely, the compiler should insert a prefetch call such that it will be issued at least an average disk access time earlier than the access. Since disk access times are so large relative to processing times, achieving this requires interprocedural analysis. Many interprocedural static analyses are NP-complete, however [37]. The algorithms that have been developed, therefore, make simplifying assumptions. These assumptions limit the quality of the results they obtain for complex applications. One recent proposal [68] that has leveraged the complexity of static analysis is an approach for protecting trusted software on untrusted hosts based on transforming the trusted software in ways that will make it more difficult to analyze statically. The consequence for I/O prefetching has been that existing static analysis approaches apply only to more structured codes that are easier to analyze – in particular, looping array codes (typically, scientific and engineering applications). On such codes, these approaches have been able to demonstrate impressive results. Most recently, Demke and Mowry [8] demonstrated that, on a four-processor SGI machine with the swap space striped across ten disks, their static analysis approach delivered 16% to 61% reductions in execution time for out-of-core versions of five applications from the NAS Parallel benchmark suite.

### 2.3 Speculative execution

The approach proposed in this dissertation uses a well-known technique called *speculative execution*. Speculative execution is simply the practice of executing when the execution may be incorrect because it is based on one or more possibly incorrect assumptions about data values. Prior and concurrent work has proposed a variety of different ways in which speculative execution could be leveraged to improve performance.