# CoRAM++: Supporting Data-Structure-Specific Memory Interfaces in FPGA Computing

## **Gabriel Leonard Weisz**

CMU-CS-15-135 September 2015

Computer Science Department School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

#### **Thesis Committee:**

James C. Hoe (Chair)

Kayvon Fatahalian

Kenneth Mai

Todd Mowry

Joel S. Emer (M.I.T. / NVIDIA)

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Copyright © 2015 Gabriel Leonard Weisz

This research was sponsored by the National Science Foundation under grant number CCF-1012851, the Industrial Technology Research Institute under grant number ITRIMSL2008, and Intel.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

### **Abstract**

FPGAs offer high performance and power efficient computation, but are difficult to use. In particular, the effort involved in managing data movements between on-chip computation components and off-chip DRAM has prevented FPGAs from being widely adopted by the computing industry. Recently developed FPGA programming environments layer simplifying abstractions on top of the DRAM interfaces provided by FPGA vendors, but existing programming environments have primarily focused on support for simple, regular data access patterns such as block copy and streaming.

This thesis proposes CoRAM++, an FPGA programming environment that efficiently supports complex data structures such as multi-dimensional arrays and linked lists in addition to simple data access patterns. CoRAM++ application developers manage data movements through an extensible library of data-structure-specific application-level interfaces, which generate specialized soft-logic datapaths between application components and memory. This extensible library of data-structure-specific application-level interfaces is layered top of a system interface which allows library components to attach modules directly to a memory interface in order to lower the latency of irregular, pointer chasing operations. Our evaluation of CoRAM++ shows that this approach can provide convenient data access to a variety of data structures without introducing undue performance or resource overheads, which should make CoRAM++ attractive to FPGA application developers.

# Acknowledgments

Thank you James Hoe, for supporting me, guiding towards interesting work, and encouraging me to look into anything that might be useful. You have an incredible ability to discern which aspects of a project are most interesting, and to recruit great students and post-docs.

Thank you committee members: Ken Mai, Kayvon Fatahalian, Todd Mowry, and especially Joel Emer, my external committee member who trekked from Boston to Pittsburgh for my thesis defense. All of you helped me make sure the that the work went in the right direction.

Thank you Eric Chung and Michael Papamichael for immeasurable help. Thank you to all of James' students who concurrent with me at CMU: Peter Milder, Peter Klemperer, Berkin Akin, Yu Wang, Marie Nguyen, Joe Melber, Zhipeng Zhao. Thank you to my GraphGen collaborators: Eriko Nurvitadhi, Skand Hurkat, José Martínez, Carlos Guestrin, for a good project. Thank you to all of CALCM for good conversations and good talks. Thank you A-levelers for a making it a good place to work, and for coming out to lunch. Thank you to all of my friends at CMU, particularly the 7th floor and A-level crews.

Thank you to everyone in my family. Thank you to my parents for stressing the importance of education and hard work, and for supporting me in everything I've ever done. Thank you to my grandparents, for your bravery in leaving Romania to build a life in the U.S. and demonstrating that the American dream still exists for those who are willing to work for it. Thank you Dave, the first to earn a PhD, for showing me the way. Thank you Jon, for making it clear that you need both persistence and chutzpah to finish a PhD. Thank

you Cat for everything good in my life. Without you I wouldn't have seen how much fun pursuing a PhD was. You give me inspiration and more support than I could imagine.

# **Contents**

|   | Abs      | tract                                                               | V   |

|---|----------|---------------------------------------------------------------------|-----|

|   | Ack      | nowledgments                                                        | vii |

| 1 | Intr     | oduction                                                            | 1   |

|   | 1.1      | Enabling Data-Structure-Specific Memory Interfaces                  | 3   |

|   |          | 1.1.1 A Multi-Level System Architecture                             | 3   |

|   |          | 1.1.2 Memory Interfaces Composed of Control and Data Sub-Interfaces | 5   |

|   | 1.2      | Decoupled Computing and the Original CoRAM Architecture             | 7   |

|   | 1.3      | CoRAM++ Data-Structure-Specific Interfaces                          | 8   |

|   | 1.4      | Thesis Contributions                                                | 9   |

|   | 1.5      | Thesis Outline                                                      | 10  |

| • | <b>D</b> |                                                                     | 10  |

| 2 | Вас      | kground and Related Work                                            | 13  |

|   | 2.1      | Computing with FPGAs                                                | 13  |

|   | 2.2      | Soft-logic and Hard-logic Processor Cores on FPGAs                  | 14  |

|   | 2.3      | Higher Level Hardware Description Languages                         | 16  |

|   | 2.4      | High-Level Synthesis Tools                                          | 17  |

|   | 2.5      | Bus infrastructures and Networks-on-Chip                            | 18  |

|   | 2.6 | FPGA          | Computing Application Programming Environments           | 19 |

|---|-----|---------------|----------------------------------------------------------|----|

|   | 2.7 | The C         | oRAM Architecture for FPGA Computing                     | 21 |

|   |     | 2.7.1         | Mapping the CoRAM Architecture to Soft-Logic FPGAs       | 22 |

|   |     | 2.7.2         | C-to-CoRAM: CoRAM as a High Level Synthesis Target       | 24 |

|   |     | 2.7.3         | Limitations of the CoRAM Architecture and its API        | 27 |

| 3 | The | CoRA          | M++ Programming Environment for FPGA Computing           | 31 |

|   | 3.1 | Argun         | nents for Specializing in a Soft-Logic Context           | 31 |

|   | 3.2 | Comp          | lexities in Creating Extensible Interfaces               | 33 |

|   | 3.3 | CoRA          | M++ Scope and Underlying Assumptions                     | 37 |

|   | 3.4 | CoRA          | M++ Programming Environment Overview                     | 39 |

|   | 3.5 | Exam          | ple CoRAM++ Application                                  | 41 |

| 4 | Cur | rently S      | Supported Application-Level Interfaces                   | 45 |

|   | 4.1 | Data-S        | Structure-Specific Interfaces for Memory Access Patterns | 45 |

|   |     | 4.1.1         | Block Copy Interface                                     | 46 |

|   |     | 4.1.2         | Stream Interface                                         | 47 |

|   |     | 4.1.3         | Multi-dimensional Array Interface                        | 48 |

|   |     | 4.1.4         | Linked List Interface                                    | 52 |

|   |     | 4.1.5         | B-Tree Interface                                         | 53 |

|   |     | 4.1.6         | Gather-Scatter Work-List Interface                       | 55 |

|   |     |               |                                                          | 57 |

|   | 4.2 | Utility       | Interfaces                                               | 57 |

|   | 4.2 | Utility 4.2.1 | Scratchpad Interface                                     | 57 |

|   |      | 4.2.3 Channel Interface                              | 60         |

|---|------|------------------------------------------------------|------------|

|   |      | 4.2.4 Kernel-Kernel Communication Interface          | 61         |

|   |      | 4.2.5 Thread Creation Interface                      | 62         |

| 5 | Insi | de the CoRAM++ Programming Environment               | 63         |

|   | 5.1  | The CoRAM++ Compiler                                 | 63         |

|   | 5.2  | CoRAM++ Control Thread Capabilities and Limitations  | 68         |

|   | 5.3  | CoRAM++ Built-in Interfaces                          | 70         |

|   |      | 5.3.1 Block Copy Interface                           | 70         |

|   |      | 5.3.2 Channel Interface                              | 71         |

|   |      | 5.3.3 Thread Creation Interface                      | 71         |

|   |      | 5.3.4 Script Execution Interface                     | 71         |

|   |      | 5.3.5 Control Thread System Library Interface        | 72         |

|   | 5.4  | CoRAM++ Accelerator Agents and Software Accelerators | 72         |

|   | 5.5  | CoRAM++ Cache                                        | 74         |

| _ |      |                                                      | <b>-</b> 0 |

| 6 | Con  | structing the CoRAM++ Agents                         | <b>7</b> 9 |

|   | 6.1  | Stream Agent                                         | 80         |

|   | 6.2  | Multi-Dimensional Array Agent                        | 81         |

|   | 6.3  | Linked List Agent                                    | 81         |

|   | 6.4  | B-Tree Agent                                         | 85         |

|   | 6.5  | Gather-Scatter Work-List Agent                       | 85         |

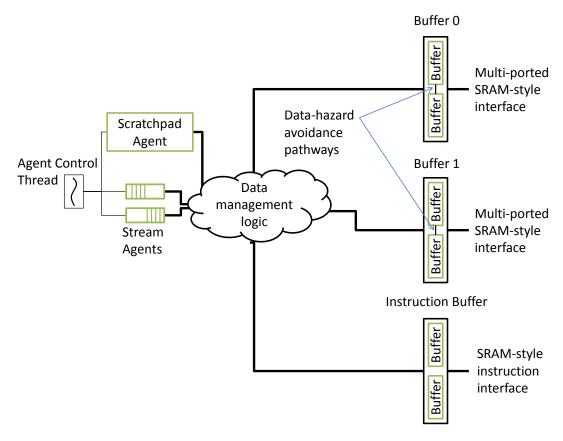

|   | 6.6  | Scratchpad Agent                                     | 87         |

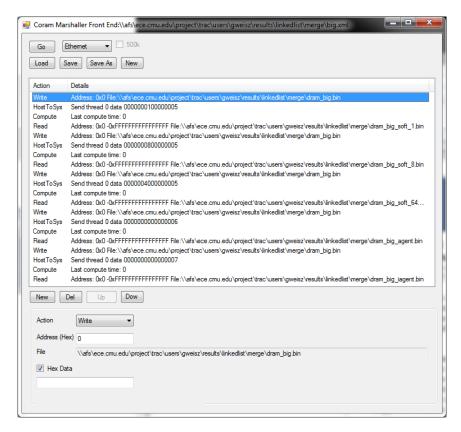

|   | 6.7  | Host Computer Agent                                  | 88         |

|    | 6.8  | Kernel-Kernel Communication Agent                           | 92  |

|----|------|-------------------------------------------------------------|-----|

| 7  | Eval | uating the CoRAM++ Programming Environment                  | 95  |

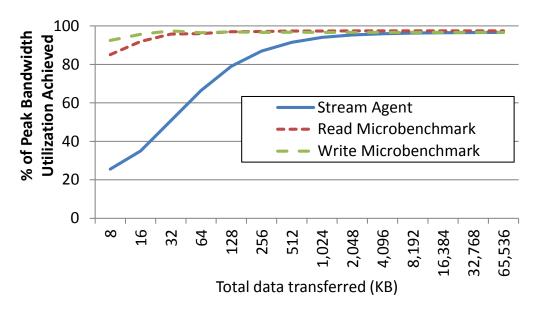

|    | 7.1  | Streaming Accesses                                          | 95  |

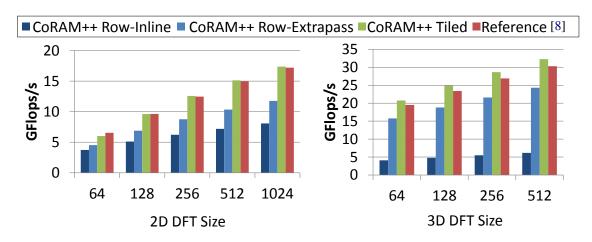

|    | 7.2  | Multi-Dimensional Array Accesses                            | 97  |

|    |      | 7.2.1 Strided Array Accesses                                | 98  |

|    |      | 7.2.2 Tiled Array Accesses                                  | 98  |

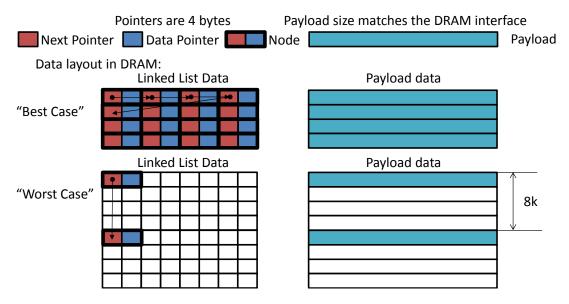

|    | 7.3  | Pointer-Chasing Linked List Accesses                        | 101 |

|    |      | 7.3.1 Linked List Traversal and Merging in Soft Logic       | 101 |

|    |      | 7.3.2 Linked List Traversal using an ARM Processor Core     | 105 |

|    | 7.4  | Graph Computations Using the Gather-Scatter Work-list Agent | 121 |

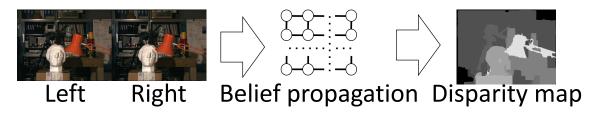

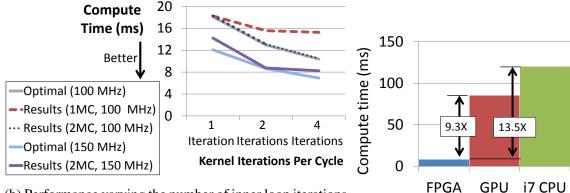

|    |      | 7.4.1 Depth Reconstruction                                  | 124 |

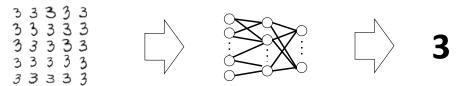

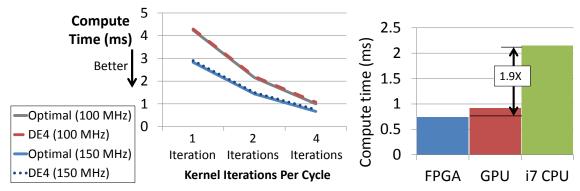

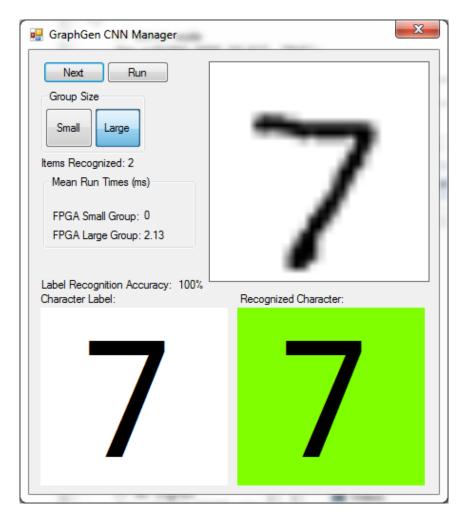

|    |      | 7.4.2 Handwriting Recognition                               | 127 |

|    | 7.5  | Streaming Data Compression                                  | 128 |

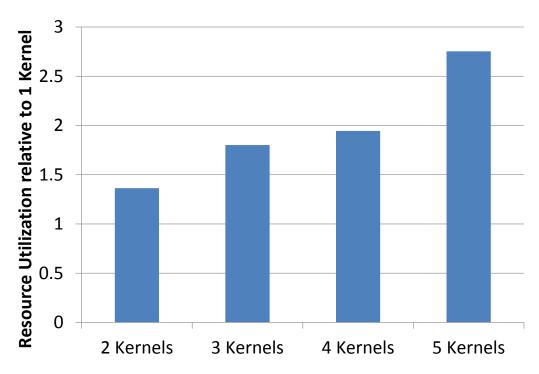

|    | 7.6  | Kernel-Kernel Communication                                 | 129 |

| 8  | Con  | clusion                                                     | 133 |

| ΑĮ | pend | ix A Application Notes for Supported Compiler Targets       | 137 |

|    | A.1  | General Application Notes                                   | 137 |

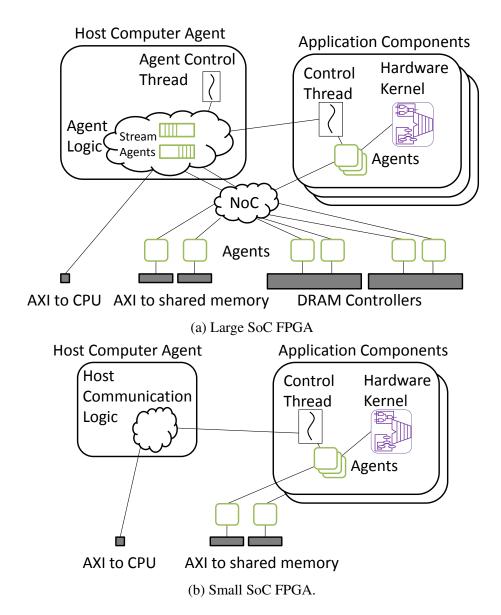

|    | A.2  | ML605 Compiler Target Notes                                 | 138 |

|    | A.3  | DE4 Compiler Target Notes                                   | 139 |

|    | A.4  | ZedBoard and ZC706 Compiler Target Notes                    | 140 |

| Δr | nend | ix B. Host Computer Agent Communication Details             | 145 |

| Referei | nces                                                       | 151 |

|---------|------------------------------------------------------------|-----|

| B.3     | Custom Client Program for the Handwriting Recognition Demo | 148 |

| B.2     | Standard Host Computer Interface Client Program            | 147 |

| B.I     | Host Computer Interface Communication Protocol             | 14/ |

# **List of Figures**

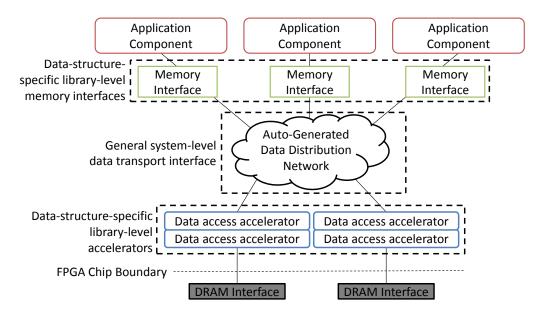

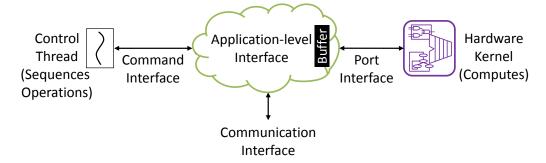

| 1.1 | CoRAM++ system architecture                                    | 4  |

|-----|----------------------------------------------------------------|----|

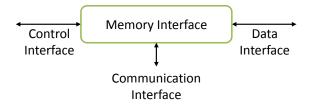

| 1.2 | A memory interface composed of control and data sub-interfaces | 5  |

| 1.3 | CoRAM/CoRAM++ application decomposition                        | 6  |

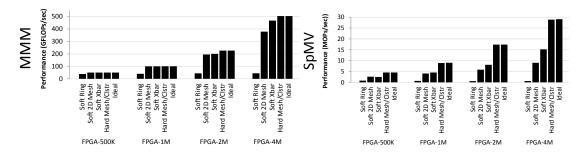

| 2.1 | Simulation results using the CoRAM Architecture                | 22 |

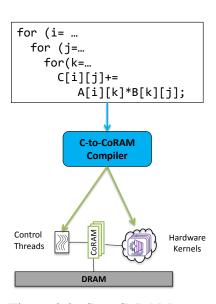

| 2.2 | C-to-CoRAM compilation workflow                                | 25 |

| 3.1 | Application-level view of a streaming CoRAM++ DFT application  | 42 |

| 4.1 | Tiled data layout                                              | 51 |

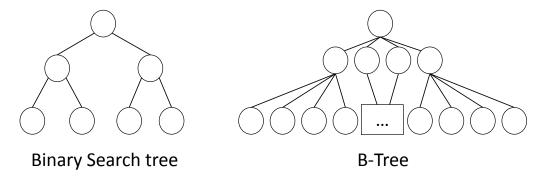

| 4.2 | B-Tree structure as compared to typical binary search trees    | 54 |

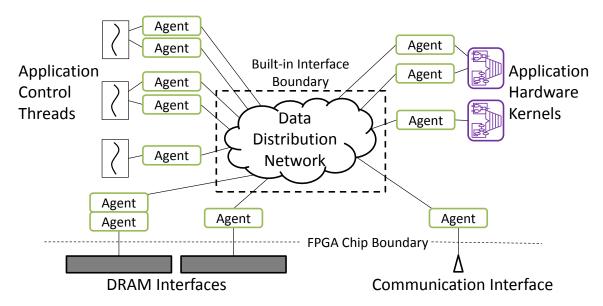

| 5.1 | System-level view of a complete CoRAM++ application            | 64 |

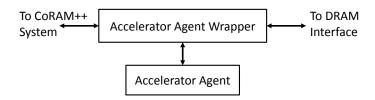

| 5.2 | Accelerator Agent Wrapper Module                               | 73 |

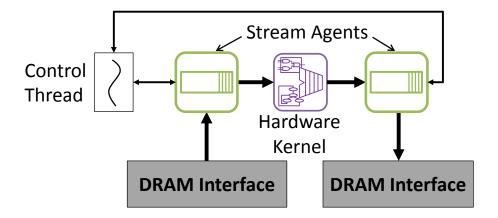

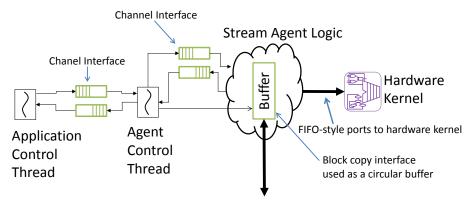

| 6.1 | Stream agent diagram                                           | 80 |

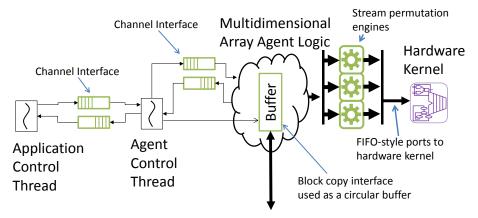

| 6.2 | Mult-dimensional array agent diagram                           | 82 |

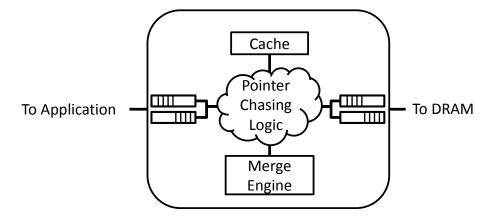

| 6.3 | Linked list engine                                             | 83 |

| 6.4 | Gather-scatter work-list agent diagram                         | 86 |

| 6.5 | Scratchpad agent diagram                                       | 88 |

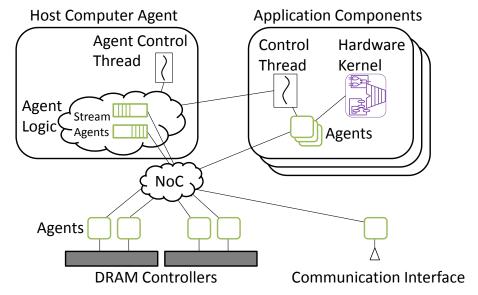

| 6.6 | Host computer agent diagrams for FPGAs without processor cores | 89 |

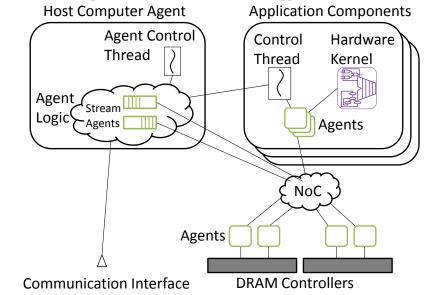

| 6.7  | Host computer agent diagrams for FPGAs with processor cores              | 90  |

|------|--------------------------------------------------------------------------|-----|

| 6.8  | Kernel-kernel communication agent diagram                                | 93  |

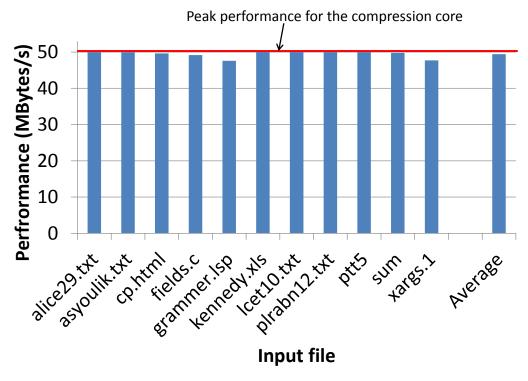

| 7.1  | Saturating DRAM interfaces                                               | 96  |

| 7.2  | 2D and 3D DFT Performance                                                | 100 |

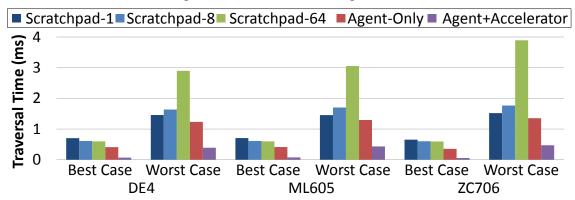

| 7.3  | Linked list configurations                                               | 103 |

| 7.4  | Linked list traversal performance                                        | 103 |

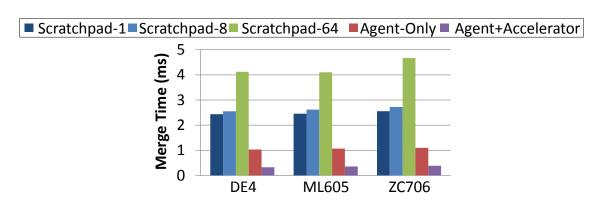

| 7.5  | Sorted linked list merge performance                                     | 105 |

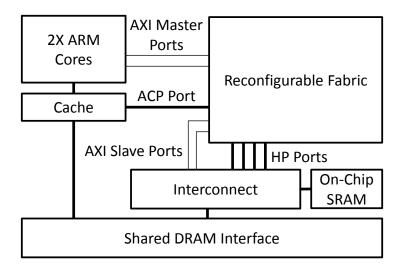

| 7.6  | Datapaths between memory, the ARM cores, and the fabric in the Zynq .    | 106 |

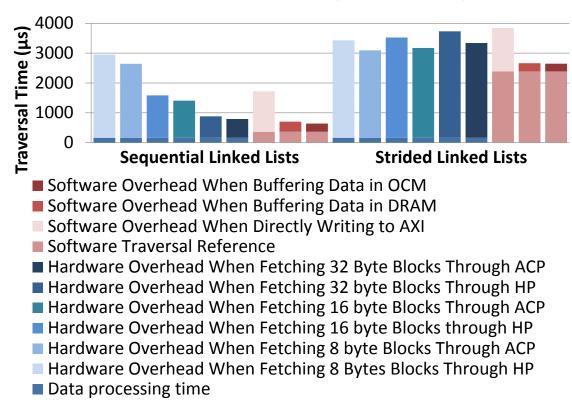

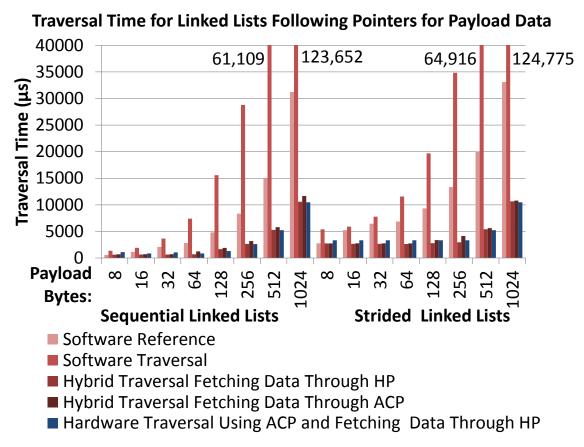

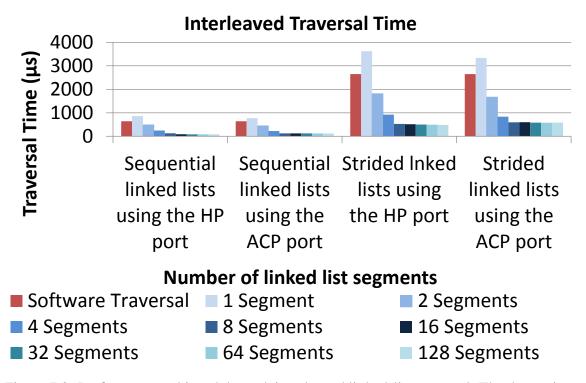

| 7.7  | Performance achieved on simple linked lists                              | 109 |

| 7.8  | Performance achieved with larger indirect data payloads                  | 112 |

| 7.9  | Performance achieved with interleaved memory accesses                    | 115 |

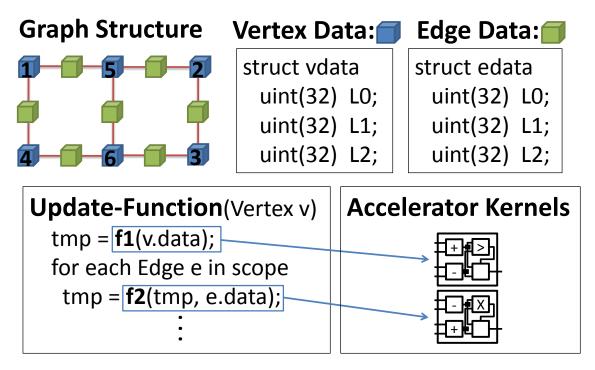

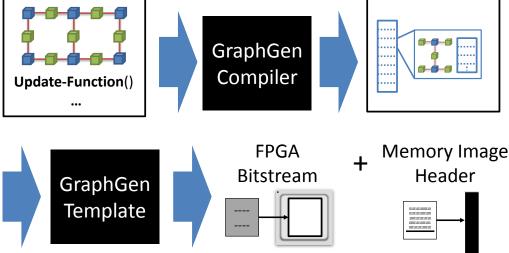

| 7.10 | Vertex-centric graph description                                         | 122 |

| 7.11 | GraphGen compiler workflow                                               | 123 |

| 7.12 | Depth Reconstruction Application Configuration and Performance           | 124 |

| 7.13 | Handwriting Recognition Application Configuration and Performance        | 126 |

| 7.14 | Compression kernel performance                                           | 128 |

| 7.15 | Kernel-Kernel Communication Agent Performance Results                    | 130 |

| 7.16 | Kernel-Kernel Communication Application Resource Utilization             | 131 |

| B.1  | Screen capture of generic host communication program                     | 147 |

| B.2  | Screen capture of host communication program for handwriting recognition | 149 |

# **List of Tables**

| 4.1  | Block copy application-level interface                        | 46  |

|------|---------------------------------------------------------------|-----|

| 4.2  | Read stream application-level interface                       | 47  |

| 4.3  | Write stream application-level interface                      | 48  |

| 4.4  | Read multi-dimensional array application-level interface      | 49  |

| 4.5  | Write multi-dimensional array application-level interface     | 50  |

| 4.6  | Linked list application-level interface                       | 53  |

| 4.7  | B-tree application-level interface                            | 55  |

| 4.8  | Hardware ports provided by the gather-scatter interface       | 56  |

| 4.9  | Scratchpad application-level interface for control threads    | 58  |

| 4.10 | Host computer application-level interface for control threads | 59  |

| 4.11 | Channel application-level interface                           | 60  |

| 4.12 | Kernel-kernel communication interface for control threads     | 61  |

| 5.1  | Supported FPGA boards                                         | 66  |

| 5.2  | CoRAM++ system library for control threads                    | 76  |

| 5.3  | Interface that accelerator agents must support                | 77  |

| 7.1  | CoRAM++ 1D DFT resource breakdown by component                | 97  |

| 7.2  | Resource utilization for CoRAM++ and reference DFTs           | 100 |

|      |                                                               |     |

| B.1 | Host computer interface message definitions | 146 |

|-----|---------------------------------------------|-----|

# Chapter 1

# Introduction

2015 marks the 50<sup>th</sup> anniversary of Moore's Law [63]. Moore's Law is an observation that the number of transistors in mass-marked computer chips doubles on a regular schedule due to decreasing transistor size. However, this schedule has just slipped from 2 years to 2.5 years [42], and Moore's Law is not the whole story for performance—clock frequencies have been stagnant for the last 10 years [2]. As Moore's Law has slowed down and clock frequencies have peaked, the high performance computing community first turned to parallel computing to obtain performance from increased transistor counts, and then created heterogeneous computing systems that combine many CPUs and GPUs into massively parallel supercomputers [5].

Field Programmable Gate Arrays (FPGAs) can further improve performance and reduce power requirements [26, 30, 40, 78]. The computing industry's largest players are working to bring FPGAs into the data center [23, 74], demonstrating real-world interest in harnessing the potential of FPGAs. However, it remains difficult to create FPGA

computing applications, both because of the effort involved in mapping computations to computation kernels, and because of the effort involved in supplying these computation kernels with data. High level synthesis tools and IP core generators (see Chapter 2) make it easier to map computation to the FPGA fabric by generating computation kernels from software source code, and recent work on FPGA programming environments makes it easier to manage data. But existing FPGA programming environments focus primarily on simple, regular data access patterns such as block copy and streaming, forcing the application developer to implement more complex behaviors that may be needed by the application.

This thesis presents CoRAM++, which extends efficient support to more complex data structures, such as arrays, linked lists, and graphs. CoRAM++ simplifies FPGA application development through an extensible library of portable data-structure specific memory interfaces that are easy to use and perform well. These memory interfaces allow applications to trigger data transfers by issuing simple, data-structure-specific commands through a software programming model. For example, a memory interface for a linear array would allow the application to trigger streaming data transfers to or from memory, while a memory interface for a multi-dimensional array would allow the application developer to stream blocks of data across any dimension. An interface for a pointer-based data structure would allow the application to traverse the data structure, and might also provide support for modifying pointers in order to change the relationships between data items. Use of CoRAM++ memory interfaces does not necessarily incur a performance penalty—these interfaces can match the best performance achievable when supporting sequential data accesses, and minimize the latency incurred when supporting irregular, pointer chasing data accesses.

CoRAM++ supports an extensible set of regular and irregular data access patterns, and allows application developers to create the application once and run it on a variety of FPGA boards from different manufacturers by simply recompiling the application, rather than manually creating new logic for each board's unique DRAM and communication interfaces. CoRAM++ targets a decoupled computing paradigm that separates an application into computation and communication components, enforcing a separation of concerns between computation and communication needs, and enabling a software-like programming model for managing communication. This decoupled computing paradigm is a good fit for the way application developers commonly build FPGA applications, which are often designed around computation kernels selected from IP libraries or generated by high level synthesis tools.

### 1.1 Enabling Data-Structure-Specific Memory Interfaces

CoRAM++ incorporates two key architectural features that allow the CoRAM++ programming environment to efficiently and conveniently support data-structure-specific memory interfaces:

- A multi-level system architecture composed of a low-level system layer and an extensible high-level library layer.

- Memory interfaces within the library layer are composed of separate sub-interfaces for control and data.

#### 1.1.1 A Multi-Level System Architecture

CoRAM++ defines a multi-level system architecture in which application components interact with an extensible library layer providing application-level data-structure-specific

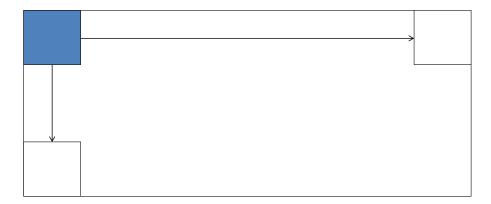

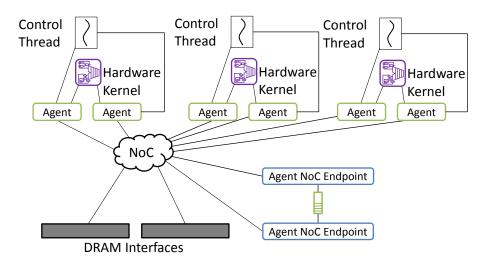

Figure 1.1: CoRAM++ system architecture including a high-level library layer that interacts with a low-level system layer, and can connect data access accelerators directly to a DRAM interface.

interfaces, which is mapped onto a system that providing low-level services. Figure 1.1 depicts this system architecture, showing application components, the library layer, the system layer, and data access accelerator modules that library components can instantiate.

The system layer manages with DRAM and other off-chip communication interfaces and on-chip data transport. The system layer provides a low-level, generic interface that is as simple as possible, in order to ensure an efficient and correct implementation. The extensible library layer builds convenient data-structure-specific interfaces on top of the system layer, and can instantiate data access accelerator modules at DRAM interfaces for performance reasons. These accelerator modules can be hardware engines that are instantiated within the reconfigurable fabric, or can be software running on a tightly integrated hard-logic processor core. The application is not aware of the implementation of the li-

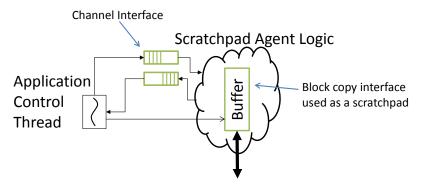

Figure 1.2: A data-structure-specific application-level memory interface composed of control and data sub-interfaces, and including a communication interface to the NoC.

brary components in use, or the existence of accelerator modules, but instead accesses the selected data-structure-specific interfaces through a data-structure-appropriate commands.

This multi-level application development environment is analogous to software development. Software development environments generally include an operating system that supports low-level functionality such as memory allocation and hardware access, and libraries that support high-level functionality, such as formatted I/O and standard implementations of common data structures. Data access accelerators are somewhat similar to the functionally provided by CUDA [68]—acceleration of particular types of operations on specialized hardware. In the case of CUDA, this means SIMD-style code that runs well on a GPU, and in the case of CoRAM++ data access accelerators, this means particular data access functions that run well on specialized hardware attached directly (or in a short pipeline) to a memory interface to minimize latency to that interface.

#### 1.1.2 Memory Interfaces Composed of Control and Data Sub-Interfaces

Figure 1.1 presents the system architecture above used by CoRAM++ to support datastructure-specific memory interfaces. Each of these memory interface includes three subinterfaces, which are depicted in Figure 1.2:

1. A control interface that is used to send commands to the interface, which can trigger

Figure 1.3: CoRAM/CoRAM++ application decomposition into separate compute and control.

or monitor the status of data transfers. The commands supported by each interface are specific to the type of data structure managed by the interface,

- 2. A data interface which provides data for computation.

- 3. A communication interface which connects to the data-distribution network.

Applications consist of modules that attach to the control and data sub-interfaces of the selected memory interfaces. This approach does not define the specific commands that go across the control interface or the ports provided by the data interface (such as SRAM-style or FIFO-style ports) supported by each memory interface, but does define that there are separate control and data sub-interfaces, This approach does not preclude a single module from attaching to both the control and data sub-interfaces of a memory interface. However, CoRAM++ defines a decoupled programming model does define how application components interact with memory interfaces.

### 1.2 Decoupled Computing and the Original CoRAM Architecture

CoRAM++ follows a decoupled computing paradigm [77] that separates applications into modules that sequence operations and modules that perform computation. Figure 1.3 shows this application decomposition, which attaches the different types of modules to the data and control interfaces described in Section 1.1.2. Hardware kernels perform computation, interacting only with locally buffered data. Control threads sequence data transfers and the invocation of hardware computation kernels.

CoRAM++ uses a programming model developed for the original CoRAM architecture [31], which defines that control threads are written in a multithreaded C-like language and compiled to state machines. This decoupled computing model shields computation kernels from the complexity of hardware platform-specific interactions with external DRAM, and shield the application developer from the need to manually create state machines. Since control threads manage long running operations, they do not need the cycle-level control that hardware description languages provide, and the fact that they are compiled from software code (and may not be as optimized as hand-designed state machines) does not hurt performance.

The application-level interfaces used by CoRAM and CoRAM++ applications are divided into two distinct sub-interfaces, as described above in Section 1.1.2:

- 1. Kernels access data through wire-level port interfaces.

- 2. Control threads issue commands through function call interfaces.

The original CoRAM architecture natively supports a block copy application-level interface for DRAM access:

- 1. Kernels access data through wire-level SRAM port interfaces.

- 2. Control threads issue commands (by making function calls) to transfer data between external DRAM and local SRAM blocks.

CoRAM's application-level interface was meant to be hardened into a future FPGA, where it would serve as a universal primitive used to support all memory access patterns. In addition to DRAM interfaces, the original CoRAM architecture supports communication interfaces such as PCI express, ethernet, and serial ports, which are mapped into a global address space and accessed using the natively supported block copy application-level interface. CoRAM++ uses a soft-logic mapping of the CoRAM architecture as its system-level interface, which was enhanced with features that enable CoRAM++ to support convenient, and is described in Section 5.3.

# 1.3 CoRAM++ Data-Structure-Specific Application-Level Interfaces

CoRAM's application-level interface can be realized in the soft logic of today's FP-GAs, but with penalties in terms of both performance and logic overhead [32]. This application-level interface also limits the ways in which libraries can layer new functionality on top of its native application-level interface, as will be illustrated by Section 2.7.3. CoRAM++ resolves these issues by by making better use of the reconfigurability of the FPGA fabric to provide a more customized datapath to memory. These changes improve performance, reduce resource overheads, and offer increased convenience to the application developer through an extensible library of data-structure-specific application-level memory interfaces.

For example, streaming a block of data from memory is a common operation. A

CoRAM++ application-level interface for streaming provides control threads with commands relevant to initiating and monitoring data streaming operations between DRAM and the hardware kernels. The hardware kernels use stream-specialized wire-level port interfaces that resemble a FIFO rather than an SRAM, in that the hardware kernels can only access the next item in the sequence.

An application-level interface used to interact with other data structures would be similarly specialized. For example, the application-level interface for a multi-dimensional array would provide commands for array traversal operations along various dimensions and support selecting between multiple in-memory data layouts at run time. The corresponding wire-level port interface could provide either FIFO-style ports or SRAM-style ports.

Below this abstraction, CoRAM++ allows data-structure-specific application-level interfaces to generate a streamlined soft-logic datapath to memory that can selectively instantiate components in order to improve performance. These performance benefits can be especially noticeable for irregular pointer based structures. For example, the application-level interface for a linked list could attach a hardware linked list engine directly to a DRAM interface to accelerate linked list operations by minimizing the latency of pointer chasing operations.

#### 1.4 Thesis Contributions

CoRAM++ encompasses a data-structure-specific approach to application development, an FPGA application development environment supporting this approach, and an extensible library of data structures. This thesis demonstrates that CoRAM++ supports

conveniently supports a variety of data-structure-specific application-level interfaces without introducing too much overhead in terms of run-time performance or resource utilization, making the following contributions:

- 1. The CoRAM++ approach to FPGA application development, which is designed around a decoupled computing model that supports an extensible library of data-structure-specific application-level memory interfaces.

- 2. An application development environment supporting this computing model, which layers this library of data-structure-specific memory interfaces on top of a low-level system-level interface, and allows library components to instantiate custom data-paths to memory (including custom modules directly connected to memory interfaces) in order to deliver better performance when supporting irregular, pointerchasing data accesses.

- 3. Initial work towards a library of data-structure-specific memory interfaces supporting data access patterns that are important in FPGA computing.

- 4. A demonstration that the CoRAM++ programming environment makes application development easier without undue overhead in terms of run-time performance or resource utilization.

#### 1.5 Thesis Outline

The remainder of this thesis presents the details of CoRAM++, covering both its inner construction and external APIs. Chapter 2 provides background information on the state of the art in FPGA application development. Chapter 3 discusses the CoRAM++ programming environment in detail, and Chapter 4 presents the current library of application-level

interfaces supported by CoRAM++. Chapter 5 discusses the implementation details of the CoRAM++ environment, and Chapter 6 details the implementation of the CoRAM++ interface library. Chapter 7 details benchmark applications that have been built using CoRAM++. Finally, Chapter 8 concludes and proposes future extensions to CoRAM++.

# Chapter 2

# **Background and Related Work**

This chapter summarizes prior work on FPGA computing, programming environments, other tools support the development of FPGA computing applications.

## 2.1 Computing with FPGAs

In addition to their common use as prototyping devices, FPGAs have long been studied as general purpose computation devices. Numerous programming models for computation with reconfigurable devices have been explored, including using reconfigurable logic to implement custom instructions within processors [19], as coprocessors paired with a microprocessor [45], shared between several processors within a multi-core chip [80], connected to a multiprocessor system through the memory bus [21], and as standalone devices connected to Ethernet networks [25]. FPGAs are especially good at power-efficient computing [26, 30, 40, 78].

In spite of the demonstrated abilities of FPGAs as computation devices, very few FP-GAs devices are employed for general purpose computation [9]. The reason that this is the

case is that FPGAs are difficult to use. FPGAs applications are most commonly designed using Register Transfer Languages (RTLs) such as Verilog and VHDL, which require the application designer to manually manage fine grained parallelism at a very low level of abstraction. It is particularly cumbersome to specify sequential actions through this programming model, which requires manually defining states and state transitions, and then manually encoding the states and transitions into register actions. The RTL programming model increases the burden required interact with DRAM and other communication interfaces (such as PCI, Ethernet, USB, and serial ports), as these interactions generally require managing sequential operations.

In addition, DRAM interfaces and other communication interfaces also vary widely between FPGA devices, meaning that the effort that went into making an application work well with the DRAM interface on one FPGA chip must be repeated when transitioning the application to another FPGA. The requirement of re-creating the logic that connects to DRAM interfaces not only applies when moving to an FPGA from a different manufacturer, but also applies to newer devices from the same manufacturer. The remainder of this section will discuss various strategies that have been used to raise the level of abstraction in FPGA application design, including programming environments that layer abstractions on top of FPGAs to simplify application development and provide portability.

# 2.2 Soft-logic and Hard-logic Processor Cores on FPGAs

FPGA development toolkits provide soft-logic processor cores [13, 88], and some FPGA chips include hard-logic processors cores that run much faster than soft-logic cores and can be used without consuming reconfigurable fabric resources [14, 86]. FPGA devel-

opment tools include a software development kit to allow application developers to write software to run on these processor cores, and include a bus interconnects and software toolkits that allow communication between processor cores and custom logic mapped to the FPGA's reconfigurable fabric. Soft processors offer limited performance due to low clock speeds, and can only connect to user-defined logic modules through buses. These buses increase the latency between DRAM and user-defined modules, mitigating the ease-of-use advantages that they provide, and can make it difficult to utilize the full bandwidth that DRAM controllers provide.

Hard processor cores do not necessarily fare any better in terms of achievable DRAM bandwidth, even though they can run at much higher clock speeds. FPGA chips such as the Xilinx Zynq [86] and Altera Arria SoC [14] contain two hard-logic ARM processor cores, hard-logic caches, a hard-logic memory controller, and hard-logic data distribution network, and connect the reconfigurable fabric to the data distribution network through multiple ports. The hard-logic components run at a higher clock rate than they would achieve if implemented in soft logic, but while they support high speed DDR-3 interfaces, Xilinx limits the physical width of the Zynq's hard logic DRAM interfaces to 32 bits. This is half the typical DDR3 chip-to-chip interface width, limiting the ARM cores and reconfigurable fabric to half the bandwidth that these DRAM interfaces would typically provide, since Xilinx runs the interfaces at the typical DDR-3 clock speeds. Some of Altera's Arria SOC chips also limit the DRAM interface to a 32 bit width, but run the interface at twice the clock speed of their Xilinx counterparts, and are less bandwidth constrained.

Both Xilinx and Altera FPGAs with built-in hard processor cores can include addi-

tional DRAM interfaces besides the DRAM interfaces attached to the hard processor cores, which can provide higher bandwidth to custom logic in the reconfigurable fabric, However, neither FPGA manufacturer includes functionality to help the application interact with these DRAM controllers (beyond their standard DMA engines), forcing application developers to interact with the faster DRAM controllers the same way that they would if the ARM cores were not present.

Intel has released Stellarton [49] chip, which included an Atom CPU and FPGA fabric in the same package. This chip connected the FPGA fabric to the remainder of the system through a slow first generation PCI-Express connection – it did not have any access to DRAM. More recently, Intel has announced new tightly coupled CPU-FPGA systems [35], which use a cache coherent connection (over a bus called "QPI") allowing the FPGA to access DRAM. These systems are just becoming more widely available, and provide a coherent cache on the FPGA side of the system, but do not provide higher level data management mechanisms.

# 2.3 Higher Level Hardware Description Languages

The two dominant hardware description languages used for FPGA design—Verilog and VHDL—require designing applications at a very low level, describing the interactions of circuit elements per clock cycle, and manually coordinating between them. While they do support some modularity and template creation, support for these features varies widely across RTL compilation software.

Several higher level languages for hardware development have been created. These languages are commonly based on functional programming languages, which are compiled

to HDL code that can then be processed using the typical hardware design tools. Examples of these languages are Bluespec [66], Chisel [20], and MyHDL [65]. These tools have been used for several large projects, up to and including processors [28, 36], and these tools are increasing in popularity over time. Several prior FPGA computing programming environments, including LEAP [38] and the CoRAM architecture [31], use Bluespec to assist with their implementation.

## 2.4 High-Level Synthesis Tools

High level synthesis is the process of generating hardware designs suitable for implementation on FPGAs from even higher level software source code. Numerous high level synthesis tools have been developed, including Xilinx Vivado High Level Synthesis (formerly AutoPilot and AutoESL) [85], Altera's C2H compiler [12], the Riverside Optimizing Compiler for Configurable Computing (ROCCC) [79], Impulse-C [48], Handel-C [59], and Catapult-C [58].

These tools are able to generate hardware pipelines from software source code, but have some limitations: High level synthesis tools generally do not have the ability to directly manage DRAM controllers (although Altera's tool does allow this and supports pipelined data transfers), and generally rely on the application designer to annotate the software source code in order to capture parallelism and data reuse. These tools also tend to be somewhat limited in the types of source code that they accept, although they are markedly improving over time. Ultimately, the capabilities of these tools are tied to their ability to extract parallelism and pipeline parallelism from sequential code.

There is recent work that utilizes AutoPilot with a variety of polyhedral optimizations

in order to capture parallelism [98], and our own work [81] has shown that the CoRAM abstraction, in concert with simple loop nest optimizations, can produce full implementations of high performance computations that interact with DRAM controllers.

LegUp [24] represents another class of high level synthesis tools. Source code is compiled to a hybrid architecture containing a MIPS soft processor, similar to the soft processors discussed above. The application is then profiled in order to detect hot areas of code, which are converted into custom accelerators.

Restricting the types of applications that a tool will support to a specific domain is one way to make the problem of automated system generation from a high level description more tractable. Domain specific tools have been created to build network processors [54], compile GPGPU applications [70], accelerate MATLAB code [43], implement linear processing transforms [60], and even generate custom FPGA devices [44].

# 2.5 Bus infrastructures and Networks-on-Chip

FPGA computing applications generally include infrastructure for data distribution within the chip. This infrastructure often comes in the form of buses such as AXI [17], but some infrastructure layers can produce point-to-point connections. Adding an infrastructure layer does introduce some overhead, but as some logic is necessary to implement the functionality provided by computing infrastructures, the additional overhead introduced by a well-written infrastructure layer is minimal.

Both Xilinx and Altera provide "system builder" tools that allow users to combine components using a GUI tool [16, 90]. These tools support load-store and streaming interfaces. and allow application developers to manually incorporate descriptor-based DMA

engines [92]. These tools can even support the hard cores and interconnects present on the chip. These tools manage all of the components connecting to a bus, multiplexing multiple interfaces into a single connection using a global address space, and arbitrating between multiple components that connect to DRAM and other communication interfaces. These tools are vendor specific, and it can be even difficult to transition designs between different versions of the tool, which don't always provide an automatic upgrade path for IP modules. It can also become cumbersome to use these point-and-click tools to create large applications.

As FPGAs grow larger and the number of components in use grows, there has been increased interest, from both the commercial and research communities, in replacing shared buses with Networks-on-Chip (NoCs) [46, 71], and even in hardening the NoC [6].

## 2.6 FPGA Computing Application Programming Environments

FPGA computing application programming environments attempt to simplify FPGA application development by automating the process of creating data paths and providing services for moving data across interfaces and within the FPGA. Existing programming environments have primarily focused on simple, regular data access patterns such as streaming and block copy. They tend to use a Network-on-Chip (NoC) for data distribution, mapping applications to a "dance hall" style architecture. A "dance hall" architecture instantiates application components on one side of the NoC and DRAM controllers and communication interfaces on the other, requiring a round trip through the NoC for every data access.

Redsharc[52] provides stream and block APIs to kernels using custom hardware or

on an embedded processor, and also decomposes applications into control and compute, managing global control through software running on an embedded processor.

Maxeler MaxCompiler [57] supports streaming and array operations, and like CoRAM and CoRAM++, decomposes applications into kernels that compute and manager modules that orchestrate computation and I/O. MaxCompiler includes a Java-like language that can be used to assemble kernel pipelines, and supports address generation modules for multi-dimensional arrays.

RCMW[50] is a virtualized FPGA development environment that supports APIs for stream and burst transfers, mapping applications to one or more physical FPGAs. RCMW allows application developers to adjust interface properties and arbitration schemes, but does not support custom logic near DRAM controllers and communication interfaces.

LEAP<sup>1</sup> [38] is an operating system for FPGAs that supports many features, incuding data transport, barriers, and file I/O including standard input and output. LEAP applications consist of modules, which can be created out of hardware or software, that communicate through latency-insensitive communication channels. LEAP supports a memory hierarchy with a "scratchpad" interface, which consistof a NoC-attached hierarchy of caches[7], that can coherently share data between multiple hardware kernels [94]. LEAP can map application components onto multiple FPGA chips, embedded processors, and computers [39], and supports a prefetcher to improve the performance of strided accesses [93]. This prefetcher is transparent to the application, and cannot be tuned for specific data access patterns. The prefetcher is instantiated near application components in the NoC, rather than near the DRAM controllers. LEAP's only model for accessing mem-

<sup>&</sup>lt;sup>1</sup>LEAP stands for both Logic-based Environment for Application Programming and Latency-insensitive Environment for Application Programming

ory is a latency-insensitive load-store interface, although there is ongoing work on using LEAP as a system layer for CoRAM++, and modifying LEAP to support the CoRAM++ concept of accelerators that are directly connected to a memory interface.

Catapult [74] is a recent effort to bring FPGA computing into the mainstream, and is currently part of a large scale effort by Microsoft to move a research effort into production. It provides a standard "shell" interface on the FPGA device that handles off chip communication, and provides compute modules with a streaming interface. Catapult will greatly change the face of FPGA computing, as Microsoft's first goal with it is to double the performance of Bing search, which, if successful, will commercially use FPGAs on a scale at which they have not been used before. The current Catapult shell attaches FPGA DRAM interfaces directly to the application, and does not appear to abstract the raw DRAM interface in any way.

Most similar to CoRAM++ in motivation is APMC [47], which goes beyond simple data access patterns by including a specialized descriptor-based DMA engine supporting load-store, streaming, array, linked list, and tree based data transfers. APMC allows application developers to write software code to manage data transfers, which runs on a Xilinx microblaze processor. APMC's descriptor-based DMA engine includes a scratchpad that can be used as a traversal cache [33] to store the results of a data structure traversal for later reuse.

## 2.7 The CoRAM Architecture for FPGA Computing

The CoRAM architecture proposes new FPGAs with built in data management features (implemented in the hard logic that makes up a CoRAM FPGA), along with a pro-

(a) Matrix-matrix multiply results (b) Sparse matrix-vector multiply results Figure 2.1: Simulation results using the original CoRAM architecture [32].

gramming model that decomposes applications into kernels that perform computation and control threads that manage control and communication. CoRAM defines a fixed set of application-level interfaces that are meant to be used as building blocks for all applications. These application-level interfaces include block copy memory APIs to move data between DRAM interfaces and kernels, and queue-based and register-based messaging APIs for communications between control threads and kernels. The CoRAM architecture supports "personalities" for layering application-level interfaces on top of its own, but does not allow CoRAM personalities to provide the most convenient interfaces to applications, as will be discussed in Section 2.7.3.

#### 2.7.1 Mapping the CoRAM Architecture to Soft-Logic FPGAs

The CoRAM architecture has been realized in soft logic [32], and can perform well when supporting computations that perform regular data accesses. The chart on the left side of Figure 2.1 shows the results of a simulation study on a single precision floating point matrix-matrix multiplication (MMM) on the CoRAM architecture. The results are grouped by simulated FPGA size, ranging from 500k to 4 million logic elements. Each FPGA size includes performance results simulating a soft implementation of CoRAM using a ring, mesh or crossbar NoC, along with a hard implementation using a hard logic

mesh NoC and CoRAM cluster, and an "Ideal" result which is the peak theoretical throughput of the processing elements. In these simulation results, the performance of the soft-logic realizations of the application are almost identical to the hard-logic realizations for the two smaller FPGA sizes (which are still medium-to-large FPGAs when compared to commercially available chips in 2015), and the soft-logic realizations are close in performance to the hard-logic realizations when using the crossbar NoC in the two larger simulated FPGAs.

While the performance of the MMM computation (with regular memory accesses) is good when using a CoRAM implementation that is mapped to soft logic, the performance of irregular computations (which require data dependent memory accesses) is not. The chart on the right side of Figure 2.1 shows how the soft-logic implementation of the CoRAM architecture suffers when computing a Sparse Matrix-Vector Multiplication (SpMV). The figure shows the results of a SpMV using single precision floating point data stored in the common compressed sparse row (CSR) format [3], which omits zero-valued data in a sparse matrix to skip unneeded computations and data transfers. Omitting zerovalued data greatly reduces the number of computations to perform, but requires irregular, data dependent accesses in order to process the non-zero data. The figure shows that all of the soft-logic realizations of the application are much slower than the hard-logic ones when performing the SpMV calculation. The soft-logic realization of the CoRAM architecture can include a cache between the DRAM interfaces and NoC, but the lower clock speeds of the soft-logic realization of CoRAM does not allow the cache to overcome the latency of the NoC round trip for every access. One of goals of CoRAM++ is to resolve this type of problem by allowing CoRAM++ data-structure-specific application-level memory interfaces to attach data-structure specific accelerators directly to the memory interface in order to make irregular, data dependent memory accesses faster. CoRAM++ also allows data-structure-specific application-level memory interfaces to run pointer-chasing code on hard-logic processor of tightly-coupled CPU-FGPA systems (such as the Xilinx Zynq or Intel HARP), using the higher clock speeds and hard-logic caches available on these systems to make pointer-chasing data accesses faster.

ShrinkWrap [29] is an add-on that tunes the NoC used by the soft-logic implementation of CoRAM for the application. ShrinkWrap allows the application to specify how much bandwidth various components need, and uses this information to configure the NoC topology and data path width for this bandwidth in order to reduce NoC resource requirements. Shrinkwrap can also create separate NoCs for components that only read data or only write data, creating a pair of trees that transport data in each direction, are tuned to the aggregated NoC bandwidth needed by application components while reducing the width of the data path going to each component, further reducing resource requirements. The evaluation of ShrinkWrap showed that when an application can benefit from a reduced-bandwidth NoC, ShrinkWrap can reduce resource requirements by an order of magnitude while increasing the maximum clock speed of the application.

#### 2.7.2 C-to-CoRAM: CoRAM as a High Level Synthesis Target

The C-to-CoRAM compiler [81] is an exploration of the original CoRAM architecture as a high-level synthesis target, in order to understand the ramifications of the CoRAM architecture's decoupled computing model on the high-level synthesis process. Most of the high-level synthesis tools discussed above do not support interactions with DRAM, and the goal of C-to-CoRAM was to see if the techniques that they use to generate hardware from

software code could be combined with the CoRAM architecture's data transfer abstraction to generate complete applications.

Another important distinction between C-to-CoRAM and the high-level synthesis tools discussed above is that CoRAM++ is annotation-free. Most high-level synthesis tools require that the user specify which parts of the application to pipeline and parallelize, but the C-to-CoRAM compiler does not. This ability is due to the C-to-CoRAM compiler's focus on loops—by restricting the code that the compiler processes to tight loops. it can find code that be pipelined and parallelized by tracing through data dependencies.

Figure 2.2 shows the workflow used by the C-to-CoRAM compiler. The C-to-CoRAM compiler takes a loop nest program, partitions the program into compute and control portions, and the uses the ROCCC [79] highlevel synthesis tool together with the soft-logic realization of the original CoRAM architecture to generate an FPGA programming file. The C-to-CoRAM compiler uses well known auto-parallelization and data reuse detection techniques in order to create applications that can perform well on FPGAs. The C-to-CoRAM compiler can automatically interleave independent computations pilation workflow.

Figure 2.2: C-to-CoRAM com-

through deeply pipelined kernels, reorganizes data transfers for efficient implementation, and instantiates stream buffers to take advantage of data reuse that it finds.

While reorganizing data transfers, the C-to-CoRAM compiler converts them into a data stream that is delivered to hardware kernels, and can even generated stride-permutation stream buffers to avoid strided accesses that inefficiently use the DRAM row buffer, by performing them on chip using local buffers that can retrieve any row with one cycle latency. These stream buffers instantiated by the C-to-CoRAM compiler are tuned for the exact data access pattern that the application needs. The compiler allows users to easily scale the generated hardware to fit larger or smaller FPGA devices, and target devices from multiple FPGA vendors.

The C-to-CoRAM compiler was tested using FPGA hardware from Xilinx and Altera on floating point matrix-matrix multiplication, 2d direct convolution, and k-nearest neighbor workloads, using one or two DRAM controllers. Application performance on FPGA hardware ranges from  $4\times$  slower to  $2\times$  faster than previously published work on the same hardware. It can use the ShrinkWrap extensions to the original CoRAM architecture to reduce NoC requirements when not all of the DRAM bandwidth is needed.

The main takeaway from the C-to-CoRAM project is that it is possible to use the original CoRAM architecture as a high-level synthesis target. As with many high level synthesis tools, C-to-CoRAM can only provide good performance on code from which parallelism and data reuse can be automatically extracted. C-to-CoRAM extracted parallelism and data reuse by recognizing particular data access patterns and instantiating pipelined and parallel computation kernels and parameterized stream buffers to take advantage of these data access patterns. The C-to-CoRAM compiler could use state-of-the-art polyhedral analysis techniques to find and parallelize more code, but by doing so it would likely lose the ability to perform annotation-free optimization, as most polyhedral analysis tools require annotation to restrict their search space.

#### 2.7.3 Limitations of the CoRAM Architecture and its API

The CoRAM++ abstraction inherits its high level programming model from the original CoRAM architecture, which is the decomposition of applications into Processing Elements that perform computation and Control Threads that manage global control and data transfers. This decomposition allows a separation of concerns between compute and control, and allows Control Threads to be expressed through a software design language rather than a hardware design language. Since Control Threads are meant to preside over data transfers that take many cycles and are limited by the DRAM controller, they would have little to gain from the performance increase provided by the cycle-level control of hardware design languages.

This programing model causes performance issues in soft logic when an application performs data dependent accesses – for example with the sparse matrix-vector multiplication whose simulation results are discussed above in Section 2.7. The simulation results show that when targeting the higher clock speeds of hardware the CoRAM architecture does much better than when targeting soft logic, in spite of the fact that the soft-logic realization of the CoRAM architecture includes a cache attached to the DRAM controllers. The reason for this issue is the latency of DRAM requests, which much start from a control thread (which has been compiled to an FSM), go across the NoC, through the cache (when included), and to the DRAM interface. The data-structure-specific approach of CoRAM++ addresses this issue by allowing data-structure-specific accelerators that are attached directly to the DRAM interface. Chapter 5.1 will provide more detail about data-structure-specific accelerators.

In addition to providing better performance, CoRAM++ also provides more conve-

nience to the application developer through simple data-structure-specific application-level interfaces with "fire-and-forget" semantics—that is application developers can issue commands using these interfaces, and rely on the CoRAM++ programming environment to execute the commands without blocking the application, even if the command takes a long time to run. The original CoRAM architecture does not allow simple "fire-and-forget" style data structure code, as will be explained below.

As a hardware architecture, the original CoRAM architecture contains built-in support for a limited set of application-level interfaces. The original CoRAM architecture defines a block copy application-level interface that moved data between local SRAM blocks (called "CoRAM" blocks) and a global address space that contains DRAM controllers and communication interfaces The original CoRAM architecture also supports bidirectional communication channels between a single Control Thread and a single Processing Element in the form of message queues and shared registers. These application-level interfaces are intended to serve as building blocks for all communication patterns.

The original CoRAM architecture defines "personalities" as a way for library code to supplement its built-in application-level interfaces. CoRAM personalities can encapsulate CoRAM blocks and communication channels, allowing CoRAM personalities to build new application-level interfaces on top of the built-in SRAM interface, such as a FIFO-style interface allowing access to a sequence of data items. CoRAM personalities can also provide library code to application control threads, exposing function calls that allow application control threads to issue commands specific to the CoRAM personality. However, these function calls run within the application control thread, which can cause issues when a command triggers a long-running action.

Consider a CoRAM personality for a stream. A stream personality should expose a FIFO-style interface to hardware kernels, and allow control threads to issue commands that initiate and monitor stream operations. Within the CoRAM personality, stream operations are mapped onto block copy operations by using the SRAM as a circular buffer. The circular buffer will internally maintain head and tail pointers into the buffer, and will not allow writes into the buffer when the buffer is full, or reads when the buffer is empty. The need for these blocking flow control mechanisms prevents CoRAM personalities from providing the most convenient possible application-level interfaces to applications. Section 3.2 discusses the additional code that CoRAM control threads must include when using personalities for complex, long running operations.

# Chapter 3

# The CoRAM++ Programming

# **Environment for FPGA Computing**

## 3.1 Arguments for Specializing in a Soft-Logic Context

Like most of the programming environments for FPGA computing discussed in Section 2, the original CoRAM architecture was designed around support for a single data access pattern—block copy. The original CoRAM's native application-level interface restricts hardware kernels to obtaining data from wire-level ports that connect to SRAM blocks, and restricts control threads to issuing commands that transfer data between DRAM and small SRAM blocks.

While it is possible to map all data access patterns onto a block copy paradigm, datastructure-specific application-level interfaces can be more convenient for the application developer. For example, in the original CoRAM a streaming data transfer can be implemented through repeated block copy commands issued by a control thread. However, the control thread could be simplified if it could issue simple "fire-and-forget" streaming commands to initiate and monitor streaming operations. These simple commands also allow the control thread to avoid the burden of handling subtle issues, such as flow-control related deadlocks.

The hardware kernel could also benefit from specialized interfaces for streaming. Rather than explicitly managing an SRAM as a circular buffer, the hardware kernel could utilize an application-level interface providing FIFO-style ports.

The data-structure-specific approach of CoRAM++ can also improve performance. The original CoRAM's simple, generic application-level interface is intended to serve as the universal primitive supporting all memory access patterns, and would perform well in a hardened implementation within a future FPGA. But a soft-logic implementation of CoRAM on today's commodity FPGA suffers in performance and resource overheads due to the inherent inefficiencies of soft logic. A data-structure-specific approach can recoup some of these losses in addition to providing a more convenient application-level interface.

Consider a hardware kernel operating on data stored in a linked list. Traversing the linked list requires pointer chasing operations to follow the chain of linked list nodes, and may also require pointer chasing to retrieve data payloads. While pointer chasing operations are feasible under the original CoRAM application-level interface, each pointer chasing operation must be performed by the control thread using explicit DRAM operations with very long latencies.

A command set that directly operates on linked lists not only simplifies the control thread, but also permits performance optimization by the underlying implementation. A linked list application-level interface can include a linked-list-specific engine that is be

connected directly to a DRAM interface. As will be explained in Section 3.4 below, this module can make linked list operations faster by minimizing latency when following the linked list pointers, and batching data transfers across the NoC. This linked list application-level interface might provide better even performance than could be achieved by a hardened implementation of CoRAM, which would not allow custom soft-logic modules to be connected directly to a DRAM interface, and consequently would incur many round trips across the NoC when traversing a linked list.

Data-structure-specific application-level memory interfaces can also provide interesting opportunities for hardware-software codesign. For example, Xilinx's Zynq and Intel's HARP are tightly coupled CPU systems—the FPGA fabric access the same DRAM as a CPU core, and can coherently share memory. When running an application with with pointer-chasing memory accesses on a these systems, it might be advantageous to run pointer-chasing operations on a CPU core, which can stream data to the FPGA fabric through either a dedicated hardware port or a DRAM-based queue. The application would benefit from the higher clock speeds and hard-logic cache of the CPU core in this scenario, as well as the ease-of-use of writing pointer-chasing code as software.

# 3.2 Complexities in Creating Extensible Data-Structure-Specific Application-Level Interfaces

Designing a programming environment to conveniently support extensible applicationlevel interfaces (data-structure-specific or not) is not trivial. Library code must map all data transfers onto primitives that are directly supported by the underlying programming environment, and would ideally be able to completely mask their implementation in order to support the most convenient interface possible.

For example, the original CoRAM architecture supports a supports a block copy data transfer primitive. Block copy is universal, but even the most simple data access pattern that is not block copy—streaming contiguous blocks of data to or from DRAM—cannot be built on top of a block copy data transfer primitive without some care. This issue arises because the underlying buffers used for copying blocks of data are finite in size, and flow control mechanisms must be used to ensure that data is not copied into buffers unless the buffers contain sufficient room for the data.

Streaming data transfers are commonly built on top of buffers using a circular buffer, using one pointer into the buffer as the location for writing data and another for reading it. The streaming data transfer library would keep track of both buffers, and prevent data from being written to the buffer unless the buffer contains space for the data. A streaming data transfer component should hide this implementation detail from the application, presenting the application's hardware kernel with FIFO-style ports, and providing control thread commands that initiate and monitor streaming data transfers.

Listing 1 depicts the desired control thread code for a streaming application written for the original CoRAM, using a CoRAM "Personality" to manage data transfers. The corresponding hardware kernel code is identical to the example in Chapter 3, and is omitted in the listing because the hardware kernel code is not the source of the issue at hand. Lines 1-7 and 13-14 are boilerplate—including headers, declaring a function and local variables, creating a loop. Lines 8-12 contain the useful parts of the control thread. The control thread reads a run-time parameter from the host computer, indicating the number of data items to transfer. The control thread then initiates a streaming transfer that writes data

```

1#include "StreamPersonality.h"

2 \# include "CommPersonality.h"

3 void streamer(int IN_ADDR, int OUT_ADDR) {

Personality s in=getStreamPersonality(1);

Personality s_out=getStreamPersonality(2);

5

6

Personality comm=getCommPersonality(3);

7

while (true) {

8

unsigned count=read_comm(comm)*sizeof(unsigned);

9

write_stream(s_in,&IN_ADDR,&count);

10

read_stream(s_out,&OUT_ADDR,&count);

11

wait stream(s out);

12

write comm(comm,0);

13

}

14 }

```

Listing 1: Streaming application code (which deadlocks using CoRAM stream personalities)

from DRAM to the "input" stream, and another that reads data from the "output" stream to DRAM. Finally, the control thread waits until data has been written to the "output" stream, and sends a signal to the host computer.

This control thread will not work as intended, because CoRAM personalities perform data transfers in the context of the application control thread. This prevents CoRAM personalities from performing long-running complex data transfers on behalf of the application without blocking the application control thread. This causes problems when a single control thread manages two stream personalities, because of the need for flow control when using a circular buffer to perform a streaming data transfer.

When the control thread in Listing 1 reaches line 9, it will invoke the stream personality code for that writes data from DRAM to the stream. This code will write a block of data to the circular buffer, and wait until the buffer has more space—that is until the kernel removes the data. At the beginning of the computation, the kernel will remove data, feed the

data into a streaming kernel, and eventually write output data to the output stream. As the kernel removes data from the stream, the control thread will continue issuing commands to copy data into the buffer. However, at some point, the output stream will fill up, because the output stream is also backed by a circular buffer. The only way for that space will open up in the output buffer is if the control thread issues commands to move data from the output stream to DRAM, which will not happen until the control thread reaches line 10. But the control thread cannot reach line 10 until it issues all of the commands necessary to write the entire input data set to the input stream on line 9, leading to a deadlock.

This deadlock is ultimately caused by the fact that CoRAM personalities manage data transfers in the context of application control threads—that is CoRAM personalities cannot manage data transfers independently of application code. There are two solutions available to CoRAM applications that resolve this issue: writing application code that manually invokes callback functions to manage multiple data transfers, or writing application code that manually creates a separate control thread for each stream. Each solution is discussed below.

Listing 2 illustrates a callback-based streaming application. The core of this application is an additional application loop that calls non-blocking functions that issue commands to each stream, and tracks the amount of data written to and read from the stream individually. While it is only four lines longer than the code in Listing 1, the extra loop makes it conceptually much more complicated.

Listing 3 presents the multi-threaded solution. This code creates two separate control threads, along with a communication channel between them. Each control thread manages a separate stream, and proceeds independently as it issues blocking data transfers. As with

```

1// Control Thread code for a callback-based

memory

personality-based streaming application

2 \, \# include \, "StreamPersonality.h"

3 #include "CommPersonality.h"

4 void streamer_callback(int IN_ADDR, int OUT_ADDR, int

SIZE) {

Personality s in=getStreamPersonality(1);

Personality s_out=getStreamPersonality(2);

Personality comm=getCommPersonality(3);

8

while (true) {

9

unsigned count r=read comm(comm) *sizeof(unsigned);

10

unsigned count w=count r;

11

while (count_r>0) {

12

if (count_w>0)

13

write stream nonblocking(s in, &IN ADDR, &count w);

14

read_stream_nonblocking(s_out, &OUT_ADDR, &count_r);

15

16

wait_stream(s_out);

17

write comm(comm, 0);

18 }

```

Listing 2: Streaming application code that uses application callbacks to avoid deadlock

the callback-based solution above, this code is more complex than the desired code in Listing 1. CoRAM++ allows library code to instantiate control threads that are independent from the application components. This feature allows "fire-and-forget" style commands exposing data-structure-specific application-level interfaces that are as convenient as possible.

## 3.3 CoRAM++ Scope and Underlying Assumptions

The CoRAM++ FPGA programming environment is primarily concerned with computations that run entirely within the reconfigurable FPGA fabric, and focuses on data movements between application components and DRAM. It would be possible to partition

```

1// Control Thread code for threaded memory

personality-based streaming application

2 #include "StreamPersonality.h"

3 #include "ThreadThreadPersonality.h"

4 #include "CommPersonality.h"

5// This thread reads from the kernel and writes to DRAM

6void streamer read(int OUT ADDR, int SIZE) {

Personality s_out=getStreamPersonality(2);

Personality comm=getCommPersonality(3);

Personality to_read=getThreadThreadPersonality(4);

while (true) {

10

11

unsigned count=read comm(comm)*sizeof(unsigned);

12

write_to_other_thread(to_write,count);

13

read_stream(s_out,OUT_ADDR,count);

14

wait stream(s out);

15

write_comm(comm, 0);

16

17 }

18// This thread reads from DRAM and writes to the kernel

19 void streamer read(int IN ADDR, int SIZE) {

Personality s_in=getStreamPersonality(1);

21

Personality to write=getThreadThreadPersonality(4);

22

while(true) {

23

unsigned count=read_from_other_thread(to_write);

24

write_stream(s_in, IN_ADDR, count);

25

}

26 }

```

Listing 3: Streaming application code for CoRAM using application threads to avoid deadlock

larger applications into components that run on an embedded processor (such as within the Xilinx Zynq [86]) or within a multi-socket CPU-FPGA system (such as Intel's new Xeon-FPGA hybrid system [35]), but CoRAM++ does not currently provide any tools to help an application developer decide how to partition the application between CPU cores and the FPGA fabric.

However, CoRAM++ does include some support these systems. Section 7.3.2 evaluates the possibility of accelerating pointer-chasing memory operations using the CPU cores of a tightly-coupled CPU-FPGA system. Since the CPU cores in such a system will run at higher clock speeds than the FPGA fabric and contain hard-logic caches, they should be able to perform pointer-chasing memory operations faster than the FPGA fabric. CoRAM++ also supports a host computer interface (see Section 4.2.2) that assists in moving data between a CPU-based system and FPGA DRAM. This host computer interface has a well-defined communication protocol, and uses the ARM cores on the Zynq FPGA to manage data transfers over an ethernet communication interface.

## 3.4 CoRAM++ Programming Environment Overview

Like the original CoRAM architecture, the CoRAM++ FPGA programming environment simplifies FPGA application development while supporting high performance data transfers. The CoRAM++ programming environment retains the decoupled programming model of the original CoRAM architecture. But CoRAM++ makes better use of the reconfigurable nature of soft-logic commodity FPGAs and generates a customized datapath to memory that is tuned for the data structures used by the application.

As discussed in Chapter 1.2, CoRAM++ applications are decomposed into hardware kernels that compute and control threads that control threads that sequence computation and communication. These components communicate using data-structure-specific application-level interfaces which are used to facilitate data transfers in an FPGA-agnostic fashion. An application developer designing an application for CoRAM++ performs the following steps:

- 1. Designs the hardware kernels.

- 2. Selects data-structure-specific application-level interfaces.

- 3. Writes control threads.

- 4. Runs the CoRAM++ compiler.

- 5. Invokes FPGA-vendor-specific tools.

CoRAM++ makes no restrictions on how hardware kernels are created—they can be created using any hardware design methodology, including IP core generators and the HLS generation tools discussed in Chapter 2. The data-structure-specific application-level interfaces are selected from an extensible library, and can be customized if necessary. The underlying implementation modules that support application-level interfaces are called "agents," because they act independently of application components to manage data transfers. Section 4 describes the data structures that are currently supported by this library.

CoRAM++ Control threads are written using a broad subset of the C language, which supports the common control flow constructs, and will be described in more detail in Section 5, which also discusses the CoRAM++ compilation process. CoRAM++ currently supports FPGAs from both Xilinx and Altera, and includes abstracting wrappers that provide a uniform interface to block memories and floating point cores.

## 3.5 Example CoRAM++ Application

This section presents a streaming CoRAM++ application that calculates a double precision Discrete Fourier Transform (DFT). A streaming application is convenient for elaborating CoRAM++ application components, but Chapter 7 demonstrates the CoRAM++ abstraction is not limited to streaming applications.