# Arithmetic Circuit Verification Based on Word-Level Decision Diagrams

Yirng-An Chen May, 1998 CMU-CS-98-131

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

#### **Thesis Committee:**

Randal E. Bryant, Chair Edmund M. Clarke Rob. A. Rutenbar Xudong Zhao, Intel Corporation

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Copyright © 1998, Yirng-An Chen

This research was sponsored by the Defense Advanced Research Projects Agency (DARPA) under contract number DABT63-96-C-0071.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of the National Science Foundation, the Semiconductor Research Corporation, or the U.S. Government.

#### **Abstract**

The division bug in Intel's Pentium processor has demonstrated the importance and the difficulty of verifying arithmetic circuits and the high cost of an arithmetic bug. In this thesis, we develop verification methodologies and symbolic representations for functions mapping Boolean vectors to integer or floating-point values, and build verification systems for arithmetic circuits.

Our first approach is based on a hierarchical methodology and uses multiplicative binary moment diagrams (\*BMDs) to represent functions symbolically for verification of integer circuits. \*BMDs are particularly effective for representing and manipulating functions mapping Boolean vectors to integer values. Our hierarchical methodology exploits the modular structure of arithmetic circuits to speed up the verification task. Based on this approach, we have verified a wide range of integer circuits such as multipliers and dividers.

Our \*BMD-based approach cannot be directly applied to verify floating-point (FP) circuits. The first challenge is that the existing word-level decision diagrams cannot represent floating-point functions efficiently. For this problem, we introduce Multiplicative Power Hybrid Decision Diagrams (\*PHDDs) to represent floating-point functions efficiently. \*PHDDs explode during the composition of specifications in the rounding module in the hierarchical approach. To overcome this problem, we choose to verify flattened floating-point circuits by using word-level SMV with these improvements: \*PHDDs, conditional symbolic simulation and a short-circuiting technique.

Using extended word-level SMV, FP circuits are treated as black boxes and verified against reusable specifications. The FP adder in the Aurora III Chip at the University of Michigan was verified. Our system found several errors in the design and generated a counterexample for each error. A variant of the corrected FP adder was created and verified to illustrate the ability of our system to handle different designs. For each FP adder, verification took 2 CPU hours. We believe that our system and specifications can be applied to directly verify other FP adder designs and to help find design errors. We believe that our system can be used to verify the correctness of conversion circuits which translate data from one format to another.

## Acknowledgements

This thesis would have not been possible without my advisor, Randy Bryant. Six years ago, when I came to CMU, I had no knowledge of Decision Diagrams and Formal Verification. The transition was difficult, but Randy made it easy for me. He patiently initiated me into Binary Decision Diagrams and Formal Verification; he wisely guided me through the maze of graduate studies and research; he ceaselessly gave me confidence when I doubted myself. How many times have I gone into his office frustrated and discouraged about my research and come out smiling!

My committee members, Edmund Clarke, Rob Rutenbar, and Xudong Zhao have given me much help in my research and in writing my thesis. The work I have done on word-level SMV benefits greatly from conversations with and course taught by Edmund Clarke. My three summer jobs at Intel Strategic CAD Labs with Xudong Zhao have, without any doubt, widened my view of formal verification, especially for industrial circuits. Rob Rutenbar led me to obtain the floating-point circuit from the University of Michigan. Prof. Brown and Mr. Riepe at the University of Michigan and Dr. Huff at Intel provided the floating-point adder circuit and valuable discussion about the design. Chapter 6 would not exist without Rutenbar's suggestion and Huff's circuit.

I have enjoyed the School of Computer Science at Carnegie Mellon University since the first day I was here. My wonderful officemates, Bwolen Yang, Henry Rowley and James Thomas made my office a pleasant place to be in and made my time at work more delightful. They have helped in almost every aspect of my daily needs in the department, from Unix commands to paper proofreading. I have also learned much from my former officemate Rujith S. DeSilva. Other friends in CS and ECE departments also made my graduate studies pleasant: Hao-Chi Wong, Karen Z. Haigh, Arup Mukherjee, Claudson F. Bornstein, Manish Pandey, Alok Jain, Shipra Panda, Vishnu A. Patankar, Miroslav N. Velev, Yuan Lu, and many more. Special thanks go to Sharon Burks and Joan Maddamma, who have always greeted me with a pleasant smile when I walked into their office. They have taken care of every administrative detail concerning me and much more.

Pittsburgh is the city where I have lived the longest except for my home town Chia-Yi in Taiwan. Throughout the years, I have grown to love this city, to love many people I have had the pleasure to share my time with. I thank my host family, Ms. Maxine Matz and her family, for sharing their Thanksgiving and Easter holidays with me in my study period. I also thank Mr. and Mrs. Aston and their family, for sharing their Christmas holidays with me. I enjoyed the friendship offered by International Bible study group, especially Jody Jackson, David Palmer, and George Mazariegos.

I also want to thank my parents, who taught me the value of hard work by their own example. I have always felt their love and support despite the fact that they are thousands of miles away.

Finally, I thank my lovely wife, Mei-Ling Liao, who accompanied me for the first four years and gave me her full support in my studies. I could not go through this PhD program without her.

## **Contents**

| 1 | Intro | oductio                                 | n                                   | 1  |  |

|---|-------|-----------------------------------------|-------------------------------------|----|--|

|   | 1.1   | 1.1 Verification of arithmetic circuits |                                     |    |  |

|   | 1.2   | Relate                                  | d work                              | 2  |  |

|   |       | 1.2.1                                   | Decision Diagrams                   | 3  |  |

|   |       | 1.2.2                                   | Verification Techniques             | 6  |  |

|   | 1.3   | Scope                                   | of the thesis                       | 11 |  |

|   | 1.4   | Thesis                                  | overview                            | 11 |  |

| 2 | Rep   | resentat                                | tions for Integer Functions         | 13 |  |

|   | 2.1   | The *F                                  | BMD Data Structure                  | 13 |  |

|   |       | 2.1.1                                   | Function Decompositions             | 13 |  |

|   |       | 2.1.2                                   | Edge Weights                        | 15 |  |

|   | 2.2   | Repres                                  | sentation of Integer Functions      | 17 |  |

|   |       | 2.2.1                                   | Integer Operations                  | 17 |  |

|   |       | 2.2.2                                   | Representation of Boolean Functions | 19 |  |

|   | 2.3   | 2.3 Algorithms for *BMDs                |                                     | 22 |  |

|   |       | 2.3.1                                   | Representation of *BMDs             | 22 |  |

|   |       | 2.3.2                                   | Maintaining Canonical Form          | 23 |  |

|   |       | 2.3.3                                   | The Apply Operations                | 26 |  |

|   | 2.4   | Relate                                  | d Work                              | 30 |  |

| 3 | Veri | fication                     | of Integer Circuits                           | 33 |  |  |  |

|---|------|------------------------------|-----------------------------------------------|----|--|--|--|

|   | 3.1  | Hierar                       | chical Verification                           | 33 |  |  |  |

|   |      | 3.1.1                        | Hierarchical Verification                     | 35 |  |  |  |

|   |      | 3.1.2                        | Component Verification                        | 36 |  |  |  |

|   | 3.2  | Verific                      | eation System: Arithmetic Circuit Verifier    | 36 |  |  |  |

|   | 3.3  | Additi                       | onal Techniques                               | 40 |  |  |  |

|   | 3.4  | Experi                       | imental Results                               | 45 |  |  |  |

|   | 3.5  | Relate                       | d Work                                        | 47 |  |  |  |

| 4 | Rep  | resentat                     | tion for Floating-Point Functions             | 49 |  |  |  |

|   | 4.1  | Reason                       | ns for A New Diagrams                         | 49 |  |  |  |

|   | 4.2  | The *F                       | PHDD Data Structure                           | 51 |  |  |  |

|   |      | 4.2.1                        | Edge Weights                                  | 52 |  |  |  |

|   |      | 4.2.2                        | Negation Edge                                 | 53 |  |  |  |

|   | 4.3  | Repres                       | sentation of Word-Level Functions             | 53 |  |  |  |

|   |      | 4.3.1                        | Representation of Integer Functions           | 54 |  |  |  |

|   |      | 4.3.2                        | Representation of Floating-Point Numbers      | 54 |  |  |  |

|   |      | 4.3.3                        | Floating-Point Multiplication and Addition    | 57 |  |  |  |

|   | 4.4  | Experi                       | imental Results                               | 61 |  |  |  |

|   |      | 4.4.1                        | Integer Multipliers                           | 61 |  |  |  |

|   |      | 4.4.2                        | Floating-Point Multipliers                    | 61 |  |  |  |

|   |      | 4.4.3                        | Floating-Point Addition                       | 63 |  |  |  |

|   | 4.5  | Relate                       | d Work                                        | 64 |  |  |  |

| 5 | Exte | Extensions to Word-Level SMV |                                               |    |  |  |  |

|   | 5.1  | Drawb                        | backs of *BMD-Based Hierarchical Verification | 67 |  |  |  |

|   | 5.2  | Word-                        | Level SMV with *PHDDs                         | 70 |  |  |  |

|   |      | 5.2.1                        | Conditional Symbolic Simulation               | 71 |  |  |  |

|   |      | 5.2.2                        | Short-Circuiting Technique                    | 73 |  |  |  |

|   | 5.3  | Additi                       | onal *PHDD algorithms                         | 73 |  |  |  |

|   |      | 5.3.1    | Equalities and Inequalities with Conditions | 73        |

|---|------|----------|---------------------------------------------|-----------|

|   |      | 5.3.2    | Equalities and Inequalities                 | 74        |

| 6 | Veri | fication | of Floating-Point Adders                    | <b>79</b> |

|   | 6.1  | Floatir  | ng-Point Adders                             | 79        |

|   | 6.2  | Specifi  | ications of FP Adders                       | 84        |

|   |      | 6.2.1    | True Addition                               | 85        |

|   |      | 6.2.2    | True Subtraction                            | 87        |

|   |      | 6.2.3    | Specification Coverage                      | 88        |

|   | 6.3  | Verific  | ation of FP Adders                          | 88        |

|   |      | 6.3.1    | Latch Removal                               | 89        |

|   |      | 6.3.2    | Design with Bugs                            | 89        |

|   |      | 6.3.3    | Corrected Designs                           | 91        |

|   | 6.4  | Conve    | rsion Circuits                              | 92        |

| 7 | Con  | clusion  |                                             | 95        |

|   | 7.1  | Summ     | ary                                         | 95        |

|   | 7.2  | Future   | Work                                        | 96        |

|   |      | 7.2.1    | Floating-Point Multipliers & Dividers       | 96        |

|   |      | 7.2.2    | Arithmetic Circuits for MMX and DSP         | 96        |

| 8 | *PH  | DD Co    | mplexity of Floating-Point Operations       | 99        |

|   | A    | Floatir  | ng-Point Multiplication                     | 99        |

|   | В    | Floatir  | ng-Point Addition                           | 100       |

## **List of Figures**

| Example of BMD vs. *BMD                                                                                                                                           | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

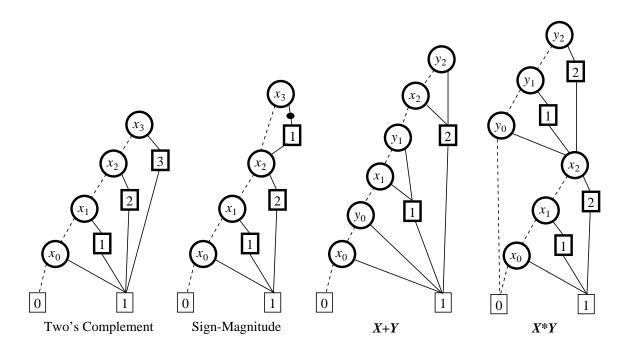

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

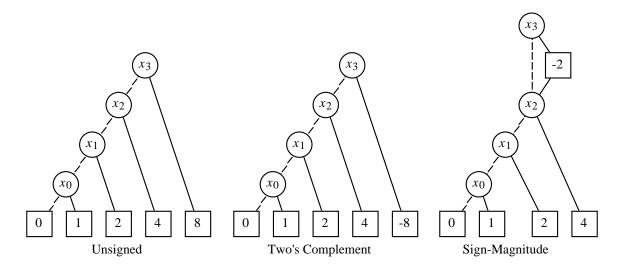

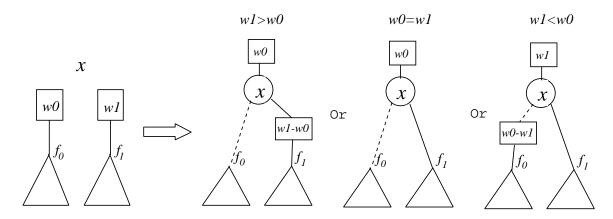

| Representations of Integers                                                                                                                                       | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

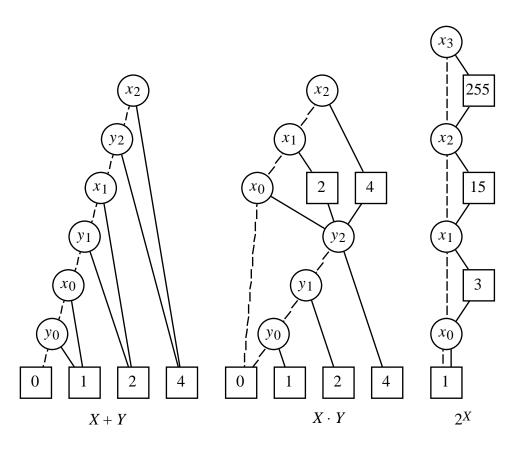

| Representations of Word-Level Sum, Product, and Exponentiation                                                                                                    | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

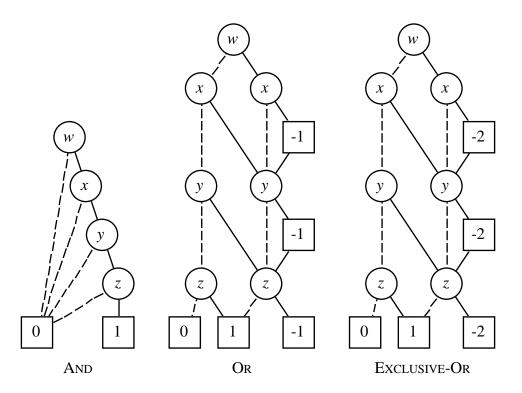

| Representations of Boolean Functions                                                                                                                              | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

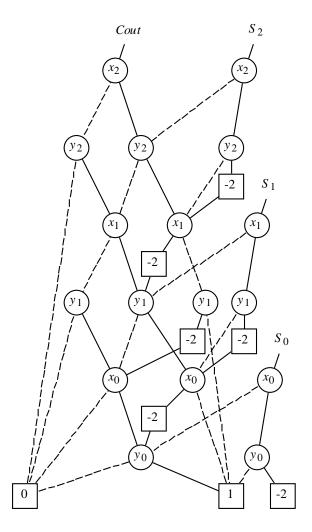

| Bit-Level Representation of Addition Functions.                                                                                                                   | 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Algorithms for Maintaining *BMD                                                                                                                                   | 23                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

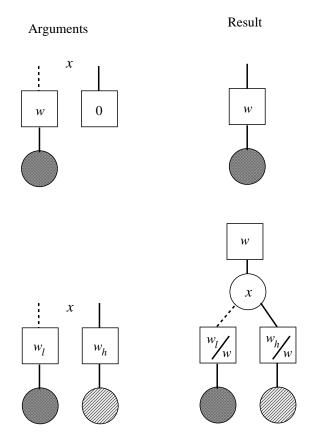

| Algorithm for Multiplying Function by Weight                                                                                                                      | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Normalizing Transformations Made by <i>MakeBranch</i>                                                                                                             | 24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Apply Algorithm for Adding Two Functions.                                                                                                                         | 27                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Recursive Section for Apply Operation for Multiplying Functions                                                                                                   | 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

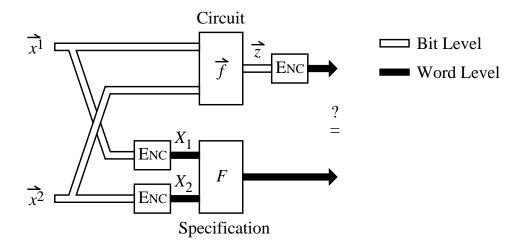

| Formulation of Verification Problem.                                                                                                                              | 34                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Multiplier Circuit Different Levels of Abstraction                                                                                                                | 35                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

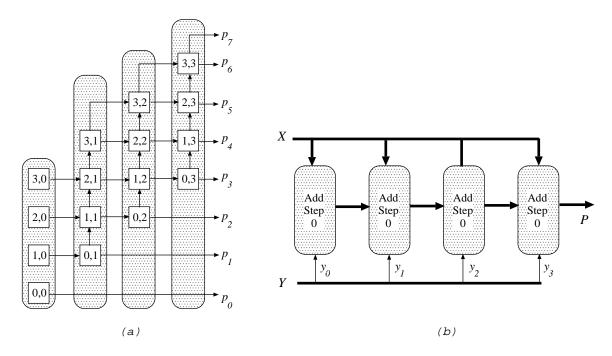

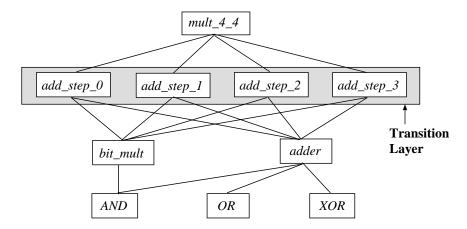

| Module hierarchy of 4×4 multiplier                                                                                                                                | 37                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACV code for Module $mult\_4\_4$ of a $4\times4$ multiplier                                                                                                       | 38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

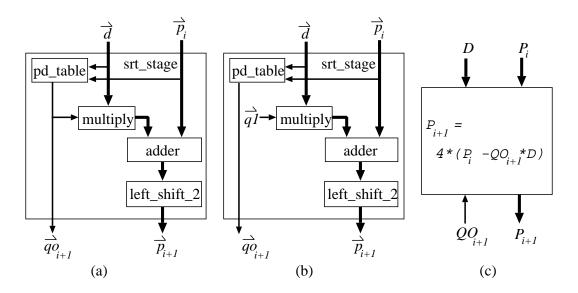

| Block level representation of SRT divider stage from different perspectives                                                                                       | 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACV code for Module $srt\_stage$                                                                                                                                  | 42                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

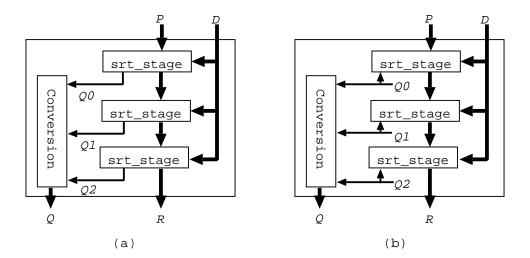

| Block level representation of a $6 \times 6$ SRT divider from two different perspectives.                                                                         | 43                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ACV description of Module $srt\_div\_6\_6$                                                                                                                        | 44                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

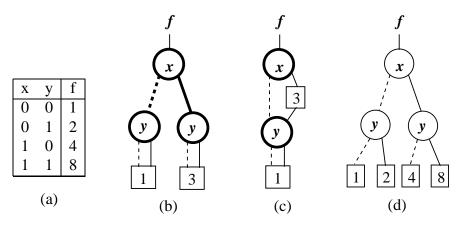

| An integer function with Boolean variables, $f = 1 + y + 3x + 3xy$ , is represented by (a) Truth table, (b) BMDs, (c) *BMDs, (d) HDDs with Shannon decompositions | 50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                   | Representations of Word-Level Sum, Product, and Exponentiation.  Representations of Boolean Functions.  Bit-Level Representation of Addition Functions.  Algorithms for Maintaining *BMD.  Algorithm for Multiplying Function by Weight.  Normalizing Transformations Made by $MakeBranch$ .  Apply Algorithm for Adding Two Functions.  Recursive Section for Apply Operation for Multiplying Functions.  Formulation of Verification Problem.  Multiplier Circuit Different Levels of Abstraction  Module hierarchy of $4\times 4$ multiplier.  ACV code for Module $mult\_4\_4$ of a $4\times 4$ multiplier.  Block level representation of SRT divider stage from different perspectives.  ACV code for Module $srt\_stage$ .  Block level representation of a $6\times 6$ SRT divider from two different perspectives.  ACV description of Module $srt\_div\_6\_6$ . |

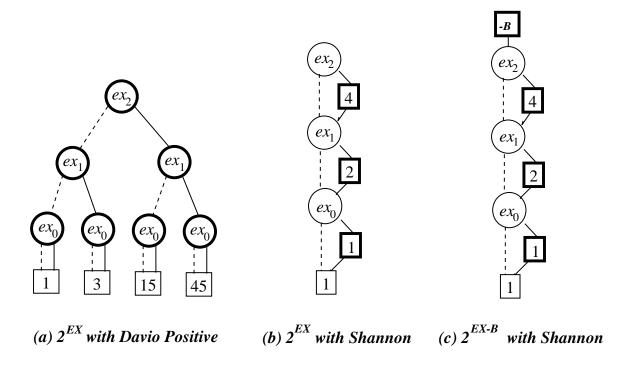

| 4.2 | *BMDs and HDDs for function $f = 2^{X-2}$ , where $X = x + 2y$ | 51  |

|-----|----------------------------------------------------------------|-----|

| 4.3 | Normalizing the edge weights                                   | 52  |

| 4.4 | *PHDD Representations of Integers and Integer operations       | 55  |

| 4.5 | *PHDD Representations of $2^{EX}$ and $2^{EX-B}$               | 56  |

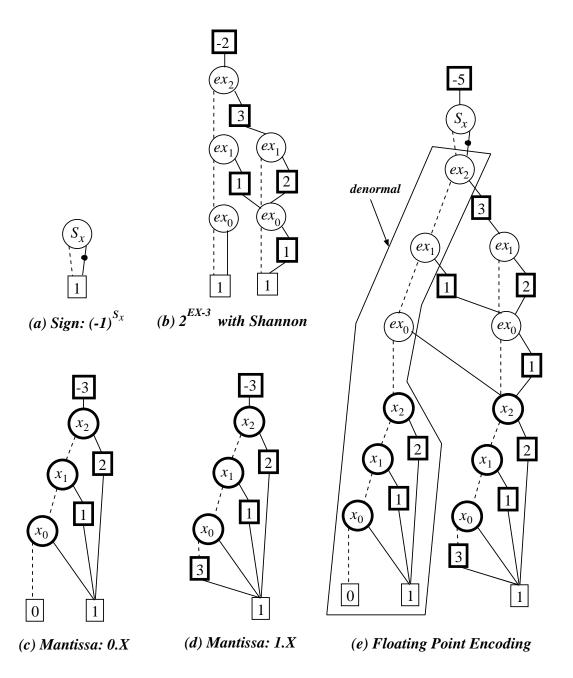

| 4.6 | Representations of floating-point encodings                    | 58  |

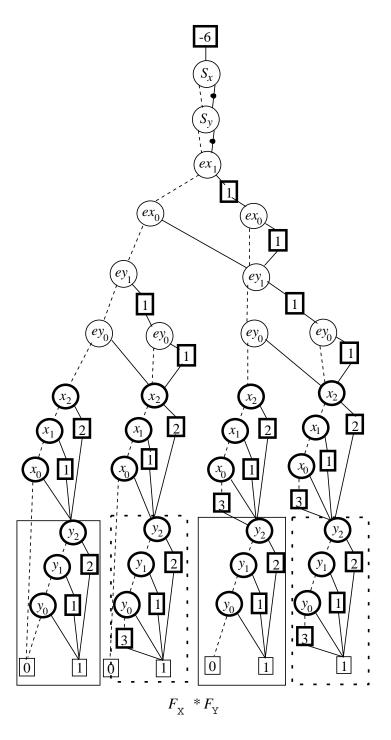

| 4.7 | Representation of floating-point multiplication.               | 59  |

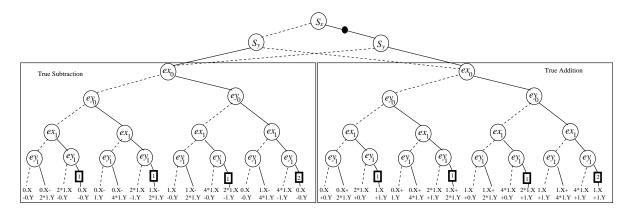

| 4.8 | Representation of floating-point addition.                     | 60  |

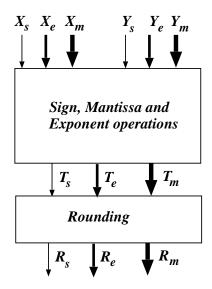

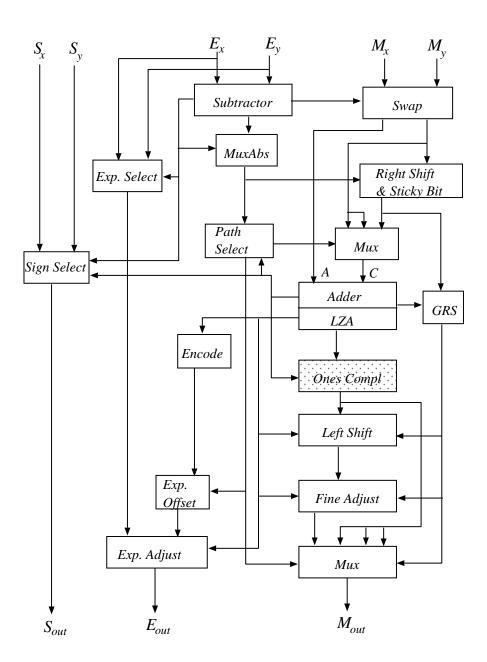

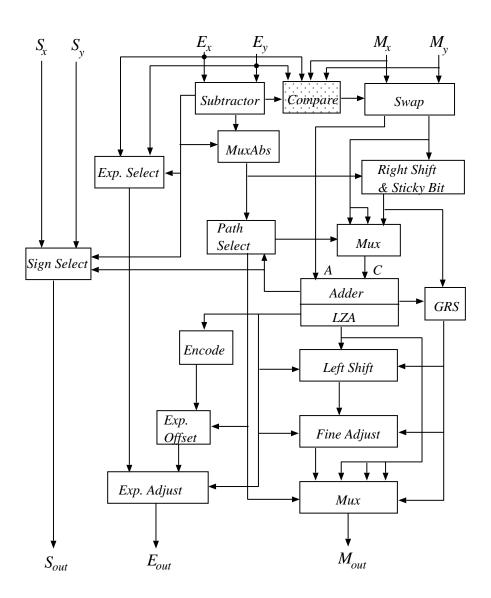

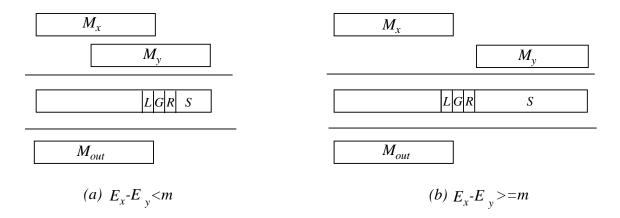

| 5.1 | Block Diagrams of floating-point circuits                      | 68  |

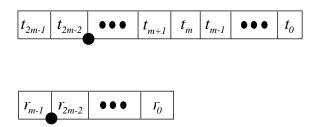

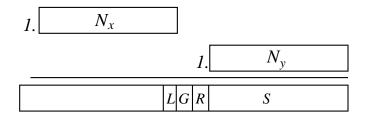

| 5.2 | Bit vectors of $T_m$ and $R_m$                                 | 69  |

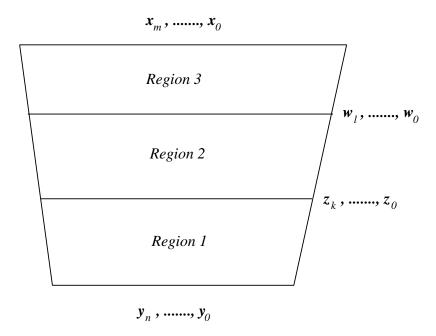

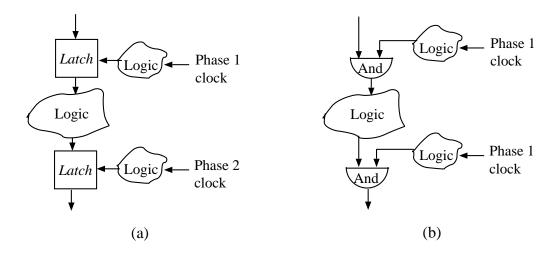

| 5.3 | Horizontal division of a combinational circuit,                | 70  |

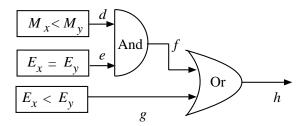

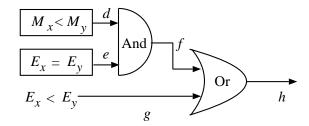

| 5.4 | The compare unit in floating-point adders.                     | 72  |

| 5.5 | algorithm for $H=0$ with conditions                            | 75  |

| 5.6 | Improved algorithm for $F > G$                                 | 76  |

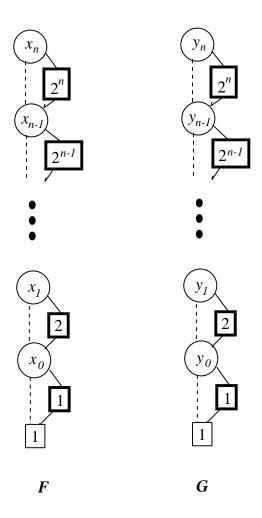

| 5.7 | *PHDDs for $F$ and $G$                                         | 78  |

| 6.1 | The Stanford FP adder                                          | 81  |

| 6.2 | A variant of Stanford FP adder.                                | 83  |

| 6.3 | Detailed circuit of the compare unit                           | 84  |

| 6.4 | Cases of true addition for the mantissa part                   | 86  |

| 6.5 | Latch Removal.                                                 | 90  |

| 6.6 | Sticky bit generation, when $E_x - E_y = 54$                   | 91  |

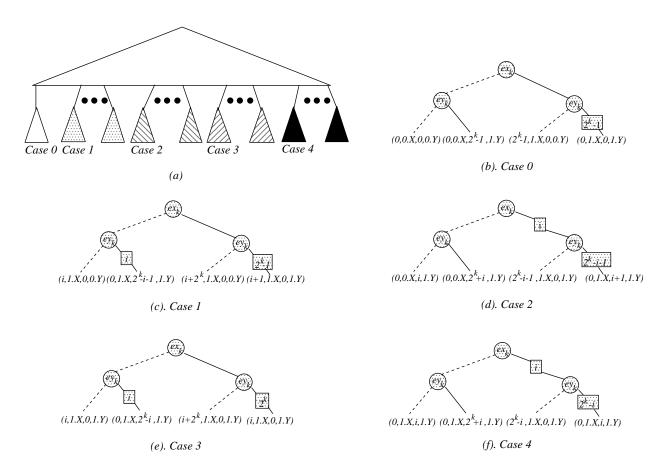

| 8.1 | Distinct sub-graphs after variable $ey_{k-1}$                  | 104 |

## **List of Tables**

| 2.1 | Termination Cases for Apply Algorithms                                          | 26 |

|-----|---------------------------------------------------------------------------------|----|

| 2.2 | Rearrangements for Apply Algorithms.                                            | 26 |

| 2.3 | Word-Level Operation Complexity.                                                | 31 |

| 3.1 | Verification Results of Multipliers                                             | 46 |

| 3.2 | Verification Results of Dividers and Square Roots.                              | 46 |

| 4.1 | Performance comparison between *BMD and *PHDD for different integer multipliers | 62 |

| 4.2 | Performance for different floating-point multipliers                            | 62 |

| 4.3 | Performance for floating-point additions                                        | 63 |

| 4.4 | Differences among four different diagrams.                                      | 64 |

| 6.1 | Summary of the FP addition of two numbers of $X$ and $Y$                        | 80 |

| 6.2 | Performance measurements of a 52-bit comparator with different orderings        | 85 |

| 6.3 | Performance measurements of verification of FP adders                           | 92 |

## Chapter 1

## Introduction

Microprocessors have been widely used in digital systems such as workstations, personal computers, aircraft control systems. In AD 2010, microprocessors running at frequencies over 1GHz will contain 90 million logic transistors and several hundred million cache transistors according to the Roadmap of Semiconductors [5]. Thus, more function units, such as digital signal processors, 3D graphic and multimedia instructions, will be added into microprocessors. The intense competition in the microprocessor field is resulting in ever shorter design cycles. To achieve it, more designers are added into design teams. To amortize the costs of development and manufacturing, microprocessors go to mass production a very short time after their introduction. Thus, a design error in a microprocessor can have a severe financial cost (e.g. the \$475 million cost of Pentium DIV bug [36, 92]) and may lead to serious injuries or even loss of life when used in life-support or control systems.

Proving the correctness of a microprocessor design is an important task. Simulation is the most popular verification technique in the industry. However, increasing complexity makes simulation insufficient to verify modern microprocessors. It is impossible to simulate all possible combinations and sequences of inputs. For example, the Pentium microprocessors have been tested by over 1 trillion of test vectors before production [29]. Gwennap [48] summarized the reported design bugs in Intel Pentium and Pentium Pro processors after mass production. Several bugs in the Pentium Pro processors can cause data corruption or system hangs and thus are visible to end users. Thus, the industry is interested in formal verification techniques for circuit designs.

Arithmetic circuits, such as the Arithmetic Logic Unit (ALU) and the Floating-Point Unit (FPU) are important parts of microprocessors. These circuits performs data operations such as addition, multiplication, division, etc. The verification of arithmetic circuits is an important part of verification of microprocessors. The goal of our work is to develop techniques which

enable the formal verification of arithmetic circuits.

Section 1.1 discusses verification of arithmetic circuits. Section 1.2 briefly surveys work in the area of formal verification, especially verification of arithmetic circuits. The goals of the thesis are summarized in Section 1.3. Finally, section 1.4 discusses the thesis organization, and a summary of each chapter.

#### 1.1 Verification of arithmetic circuits

Verification of arithmetic circuits has always been an import part of processor verification. In modern processors, arithmetic circuits contains ALUs, integer multipliers, integer dividers, floating-point (FP) adder, FP multipliers, FP dividers, FP square roots, and most of multimedia instructions. These circuits form an important part of microprocessors. Because of area and performance constraints, these circuits are not synthesized by automatic synthesis tools, rather they are custom designed. They can occupy as much as 20%-50% of the processor chip area. In Intel's Pentium II processor [51], these circuits occupied 20% of the chip area, and they accumulated up to 50% of the chip area in Sun's SuperSparc-2 processor [47].

The importance and difficulty of arithmetic circuit verification has been illustrated by the famous FDIV bug in Intel's Pentium processor which cost Intel \$475 million. This bug was not covered by the one trillion test vectors used for this processor [29]. Traditional approaches to verifying arithmetic circuits are based on simulation or emulation. However, these approaches can not exhaustively cover the input space of the circuits. For example, the whole input space of each IEEE double precision floating-point circuit with one rounding mode is  $2^{128}$  test vectors, which is impossible to simulate in practice. Theorem proving approaches require verification experts to manually guide the systems to complete the proof. Thus, to automatically verify arithmetic circuits, we need to employ a formal technique which can handle large circuits. Among all the formal verification technique, decision diagram approach comes closest to meeting these requirements. However, there are still many fundamental and pragmatic issues to be resolved. These issues include the explosion problem of decision diagrams, and specification and efficient verification of these circuits. We have addressed these issues in this thesis.

### 1.2 Related work

In this section, we summarize the research work on decision diagrams, which have been used in many applications such verification, logic synthesis. Then, we discuss different verification approaches which can be used to verify arithmetic circuits. Since this discussion is general and 1.2. RELATED WORK 3

quite broad, the specific work which is more closely related to our research will be discussed at the end of each chapter.

#### 1.2.1 Decision Diagrams

Decision Diagrams are data structures to represent discrete functions and are derived from decision trees using reduction rules which produce a canonical form. The idea of representing Boolean functions as decision digrams can be traced back to Akers' paper [2], but the widespread use as a data structure for symbolic Boolean manipulation only started with the formulation of a set of algorithms to operate on these data structures by Bryant in 1986 [13]. After that, the basic ideas of BDDs have been extended to allow efficient representation of other classes of functions. As mentioned in [94], we encountered more than 43 different decision diagrams in the past several years. Good surveys of decision diagram related work can be found in [15, 16, 94].

In this section, we summarize a few decision diagrams which have had strong impact, especially in the area of formal verification. Based on the range of the function values, decision diagrams can be divided into two classes: Bit-Level diagrams which have Boolean values and Word-Level diagrams which have integer or floating-point values.

#### **Bit-Level Diagrams**

Binary Decision Diagrams (BDDs) [13] represent switching functions  $f: B^n \to B$ , where n is the number of input variables. BDDs are based on a decomposition of Boolean functions called the "Shannon expansion". A function f can be in terms of a variable x as

$$f = \overline{x} \wedge f_{\overline{x}} \vee x \wedge f_{x} \tag{1.1}$$

where  $\land$ ,  $\lor$  and overline represent Boolean product, sum and complement. Term  $f_x$  (respectively,  $f_{\overline{x}}$ ) denotes the positive (negative) *cofactor* of f with respect to variable x, i.e., the function resulting when constant 1 (0) is substituted for x. This decomposition is the basis for the BDD representation.

Two alternative function decompositions can be expressed in terms of the XOR (exclusive-or) operation:

$$f = f_{\overline{x}} \oplus x \wedge f_{\delta x} \tag{1.2}$$

$$= f_x \oplus \overline{x} \wedge f_{\delta x} \tag{1.3}$$

where  $f_{\delta x}$  denotes the Boolean difference of function f with respect to variables x, i.e.  $f_{\delta x} = f_x \oplus f_{\overline{x}}$ . Equation 1.2 is commonly referred to as the "positive Davio" or "Reed-Muller"

expansion, while Equation 1.3 is referred to as the "negative Davio" expansion. Functional Decision Diagrams (FDDs) [68] use the positive Davio expression as the basis of the graph representation of Boolean functions. For some classes of functions, FDDs are exponentially more compact than BDDs, but the reverse can also hold. To obtain the advantage of each, Drechsler *et al* have proposed a hybrid form called Kronecker FDDs (KFDDs) [42]. In this representation, each variable has an associated decomposition, which can be any one of the three given by Equations 1.1-1.3.

Minato has developed another variant of BDDs, called "Zero-suppressed" BDDs (ZBDDs) [58], for combinatorial problems that can be solved by representing and manipulating sparse sets of bit vectors of length n [58]. The data for a problem are encoded as bit vectors of length n. Then any subset of the vectors can be represented by a Boolean function over n variables yielding 1 when the vector corresponding to the variable assignment is in the set. Minato has shown that a number of combinatorial problems can be solved efficiently using a ZBDD representation [78]. It can be shown that ZBDDs reduce the size of the representation of a set of n-bit vectors over BDDs by at most a factor of n [90]. In practice, the reduction is large enough to have a significant impact.

Bit-level diagrams are not suitable for the verification of complex arithmetic circuits. First, it is very difficult to write the specification for each output bit as a Boolean function. Second, bit-level diagrams usually explode in size when representing arithmetic circuits. For example, BDD representations for integer multiplication have been shown to be exponential in the number of input bits [14]. Yang *et. al* reported that the number of BDD nodes to represent integer multiplication grows exponential at a factor of about 2.87 per bit of word size [97]. For a 16-bit multiplier, building the BDDs for the output bits requires about 3.8GB memory on a 64-bit machine (i.e. 1.9GB on a 32-bit machine).

#### **Word-Level Diagrams**

Building on the success of BDDs, there have been several efforts to extend the concept to represent functions over Boolean variables, with non-Boolean ranges, such as integers and real numbers. For example, it is very useful for verification of arithmetic circuits to represent vectors of Boolean functions as word-level functions such as integer or floating-point functions. A vector of m Boolean functions  $(f_0, f_1, ..., f_{m-1})$  can be interpreted as a integer function F whose value at  $\vec{x} = (x_0, x_1, ..., x_{n-1})$  is  $F(\vec{x}) = \sum_{i=0}^{m-1} f_i(x_0, ..., x_{n-1}) \times 2^i$ . Keeping the variables Boolean allows the use of a branching structure similar to BDDs. The challenge becomes finding a compact way to encode the numeric function values.

One straightforward way to represent numeric-valued functions is to use a decision diagrams like a BDD, but to allow arbitrary values on the terminal nodes. This representation is called Multi-Terminal BDDs (MTBDDs) [34] or Algebraic Decision Diagrams (ADDs) [4]. For expressing functions having numeric range, the Boole-Shannon expansion can be generalized

1.2. RELATED WORK

5

as:

$$f = (1-x) \cdot f_{\overline{x}} + x \cdot f_x \tag{1.4}$$

where  $\cdot$ , +, and - denote multiplication, addition, and subtraction, respectively. Note that this expansion relies on the assumption that variable x is Boolean, i.e., it will evaluate to either 0 or 1. Both MTBDDs and ADDs are based on such a pointwise decomposition. For some applications, the number of possible values is small enough that the graph size is not too big. In such applications, the simplicity of the representation makes MTBDDs viable candidate. However, these diagrams grow exponentially with the number of Boolean variables for the common integer encodings such as unsigned binary, ones complement and two's complement. For the case of unsigned binary numbers of length n, there are  $2^n$  possible values and hence the MTBDD representation must have  $2^n$  leaf nodes.

For applications where the number of possible function values is too high for MTBDD, Edge-Valued BDDs (EVBDDs) are introduced by incorporating numeric weights on the edges in order to allow greater sharing of subgraphs [72, 73]. The edge weights are combined additively. The common integer encodings can be represented in linear size of EVBDDs. For two integers X and Y represented by EVBDDs, the sum and difference also have linear complexity. However, for the multiplication, the complexity and size of EVBDDs grows exponentially. Multiplicative edge weights are added into EVBDDs to yield another representation called Factored EVBDDs (FEVBDDs). However, these diagrams still cannot represent  $X \cdot Y$  in polynomial size.

To overcome this exponential growth, we proposed Binary Moment Diagrams (BMDs) which provides a compact representation for these integer encodings and operations. BMDs use a function decomposition with respect to the input variables in a manner analogous to FDDs. The function decomposition used by BMDs [20, 21], is obtained by rearranging the terms of Equation 1.4:

$$f = f_{\overline{x}} + x \cdot f_{\delta x} \tag{1.5}$$

where  $f_{\delta x} = f_x - f_{\overline{x}}$  is called the *linear moment* of f with respect to x. This terminology arises from viewing f as being a linear function with respect to its variables, and thus  $f_{\delta x}$  is the partial derivative of f with respect to x. The negative cofactor will be termed the *constant moment*, i.e., it denotes the portion of function f that remains constant with respect to x.

An extension of BMDs is to incorporate weights on the edges, yielding a representation called Multiplicative BMDs (\*BMDs) [21]. These edge weights combine multiplicatively, rather than additively as with EVDDs. With \*BMDs, word-level functions such as X + Y, X - Y,  $X \cdot Y$  and  $2^X$  all have linear-sized representations. The development of \*BMDs enables us to verify arithmetic circuits such as multipliers, dividers, etc.

Adapting the idea of KFDDs, Clarke, *et al* have developed a hybrid between MTBDDs and BMDs, which is called Hybrid Decision Diagrams (HDDs) [30]. In their representations, each variable can use one of six different decompositions, including Shannon, positive Davio and negative Davio decompositions. In their experience, the variables for the control signals should use Shannon decomposition to achieve smaller graph sizes.

Adding both additive and multiplicative weights into HDDs yields another representation called Kronecker \*BMDs (K\*BMDs) [41]. In this representation, the variables can only use one of Shannon, positive Davio and negative Davio decompositions. Both HDDs and K\*BMDs are superset of MTBDDs and BMDs. However, we do not find the additive edge weight useful for the verification of arithmetic circuits.

For the word-level diagrams mentioned above, functions mapping Boolean variables into floating-point values can not be represented efficiently without introducing rational weights on the edges or the leaf nodes. The overhead of storing and manipulating the rational edge weights make them less attraction for representing floating-point functions.

We introduced Multiplicative Power HDDs (\*PHDDs) [28] to provide a compact representation for integer and floating-point functions by extracting powers of 2 for the edge weights rather than greatest common divisors in \*BMDs. The edge weights only record the powers. In other word, the edge weight k represents  $2^k$  and the edge weights are combined multiplicatively in the same way as \*BMDs. With this feature, \*PHDDs can represent and manipulate integer and floating-point functions efficiently and can be used in the verification of floating-point circuits such as adders.

## **1.2.2** Verification Techniques

#### **Theorem Proving**

In a theorem proving approach, the circuit is described as a hierarchy of components, and there is a behavioral description of each component in the hierarchy. The proof of the correctness of a design is based on the proofs of the correctness of its components, which is obtained by composing and inferring the proofs of the components at lower levels. Theorem provers, HOL [46], Boyer-Moore [8], PVS [80] and ACL2 [67], have been successfully used to verify several hardware systems.

HOL, developed at Cambridge University, is one of the best know theorem provers applied to hardware verification [46]. Joyce [64] and Melham [77] also used HOL to perform verification of circuits. A significant application of the Boyer-Moore theorem prover is the verification of the FM8501 microprocessor by Hunt [57]. PVS provides a specification language integrated with a theorem prover, and support procedures to ease the burden of developing proofs. Srivas

1.2. RELATED WORK

and his colleagues have used PVS to verify several hardware designs such as a commercial processor [93].

Theorem provers have been used to verify arithmetic circuits and algorithms. Most of the IEEE floating point standard has been formalized by Carreño and Miner [26] in the HOL and PVS theorem provers. Verkest *et al* verified a nonrestoring division algorithm and hardware implementation using the Boyer-Moore theorem prover. Leeser *et al* verified a radix-2 square root algorithm and hardware implementation [74].

In response to Intel's famous DIV bug in Pentium processor based on SRT algorithm [76, 87, 96], the correctness of the SRT algorithm and implementation has been verified by Clarke *et al* [31] using a theorem prover, Analytica [35], and by Rueß *et al* [89] using PVS. Miner and Leathrum [79] generalized Rueß's verification work to encompasses many division algorithms and to includes a formal path relating the algorithms to the IEEE standard. AMD hired the CLI company to prove the correctness of the AMD 5K86's floating-point division algorithm using ACL2 [11]. They reported that over 1600 definitions and lemmas were involved in this proof. Kapur *et al* [66] used a theorem prover to prove the correctness of a family of integer multipliers based on Wallace trees.

However, the basic weakness of the theorem proving approach is that it requires a large amount of user intervention to create specifications and to perform proofs, which makes them unsuitable for automation. Attempts at automation of proofs have not been particularly successful, and proofs still require substantial interaction and guidance from skilled users.

#### **Model Checking**

Model checking is an automatic verification methodology to verify circuits. In this approach, a circuit is described as a state machine with transitions to describe the circuit behavior. The specifications to be checked are described as properties that the machine should or should not satisfy. Based on the data structure for representing state transitions, the model checkers can be categorized into: 1) pure BDD-based model checkers such as SMV [75], VIS [10] and COSPAN [53], and 2) other model checkers such as SPIN [55], Murphi [40] and COSPAN [53]. Note that COSPAN can use either BDD-based or explicit-state enumeration algorithms. COSPAN is the core engine of commercial verification tool  $FormalCheck^{TM}$  from Lucent Technology Inc.

Traditionally, model checkers used explicit representations of the state transition graph, which made their use impractical for all but the smallest state machines. To overcome this capacity limitation, BDDs are used to represent the state transition graphs and thus allows model checkers (SMV, VIS and COSPAN) to verify systems with as many as  $10^{100}$  states, much larger than can be verified using an explicit state representation technique. However, these model checkers still have the state explosion problem (i.e., BDD size explosion) while verifying large circuits. A number of approaches [23, 45] have focused on the use of partitioned transition relations to

reduce the BDD size during state machine exploration, but the capacity limitation is still a major problem preventing model checkers from verifying industrial circuits without abstraction.

Model checkers, SPIN, Murphi and COSPAN, use other techniques to improve the capacity of the model checking without using BDDs. SPIN uses an optimized depth-first-search graph traversal method to perform the verification task. To avoid a purely exhaustive search, SPIN uses a number of special purpose algorithms such as partial order reduction [54], state compression, and sequential bitstate hashing. Murphi explicitly generates the states and stores them in a hash table. To increase its capacity, Murphi uses many state reduction techniques including symmetry reduction [59] and exploitation of reversible rules [60]. To increase its capacity and performance, COSPAN uses several caching and hashing options, and a state minimization algorithm in its explicit-state enumeration algorithm.

In general, these model checkers can verify systems with up to 500 latches. To handle the real circuit designs in industry, the circuits must be simplified by manual abstraction. For example, the verification of the circuit to handle the cache coherence among 16 processors must be abstracted to a model that contains fewer processors (e.g. 4 processors) and a smaller word size (e.g. 1 or 2 data bits instead of 32 or 64). A number of approaches [32, 84] have been proposed to perform the abstraction automatically.

To verify arithmetic circuits, these model checkers have the following difficulties. First, their specification languages are not powerful enough to express arithmetic properties. For arithmetic circuits, the specifications must be expressed as Boolean functions, which is not suitable for complex circuits. Second, these model checkers cannot represent arithmetic circuits efficiently in their models. For example, SMV will have the BDD explosion problem for representing integer multipliers.

In order to overcome these problems, Clarke *et al* presented word-level SMV based on BDDs for Boolean functions and HDDs for integer functions [30, 33]. The specifications of arithmetic circuits are expressed in word-level and represented by HDDs. Chen *et al* [29] have applied word-level SMV to verify arithmetic circuits in one of Intel's processors. In this work, floating-point circuits were partitioned into several sub-circuits whose specifications could be expressed in terms of integer operations, because HDDs can not represent floating-point functions efficiently. The main drawback of this partitioning approach is that the specifications are implementation dependent and cannot be reused for for different implementations. For example, two different implementations of the floating-point adder can yield different partitions, and thus the specifications for the sub-circuits for one design are different from those in another. Another drawback is that this approach requires user intervention to partition the circuits and reason about the correctness of the overall specifications from the verified sub-specifications.

#### **Symbolic Simulation**

Symbolic simulation is a well know technique for simulation and verification of digital circuits

1.2. RELATED WORK 9

and is an extension of conventional digital simulation, where a simulator evaluates circuit behavior using symbolic Boolean variables to encode a range of circuit operating conditions. The initial internal state variables as well as the input values can be Boolean expressions, which are usually expressed in parametric form [12]. This makes each run of a symbolic simulator equivalent multiple runs of a conventional simulator. Jain *et al* [63] presented an efficient method to generate the parametric form.

After the introduction of BDDs by Bryant, symbolic simulation became more practical. Both COSMOS [18] developed at Carnegie Mellon University and Voss [91] developed at the University of British Columbia use BDDs as the representations for Boolean functions. These two simulators have been the framework for verification of different classes of circuits [6, 19, 61, 81, 82]. Beatty *et al* [6] verified a microprocessor using COSMOS. Voss has been used to verify memory arrays in the PowerPC processor [82]. Bose and Fisher [7] have used symbolic simulation to a verify pipelined hardware system.

Compared with model checking, the symbolic simulation technique can handle much larger circuits, because this approach can only cover some of the input spaces in each simulation run. However, symbolic simulation can not used to completely verify arithmetic circuits such as integer multipliers, dividers, etc, because the input spaces of these circuits are very large and the BDDs blow up exponentially for these circuits. An exhaustive simulation to cover the entire input space is almost impossible for large integer multipliers, dividers and floating-point circuits. Another problem for symbolic simulation is that the specifications must be expressed as Boolean functions, which are very complicated for arithmetic circuits.

#### **Equivalence Checking**

In recent years, many CAD vendors offered equivalence checking tools for design verification. For example, the partial list of equivalence checkers are Formality (from Synopsys), Design Verifyer (from Chrysalis), VFormal (from Compass), Verity (from IBM). These tools perform logic equivalence checking of two circuits based structural analysis and BDD techniques.

Some equivalence checking techniques have been described in [37, 38, 70]. The common assumption used in the equivalence checking is that two circuits have identical state encodings (latches) [70]. With this assumption, only the equivalence of the combinational portions of two circuits must be checked. Coudert *et al* [37, 38] and Cabodi *et al* [24] use a symbolic breadth first exploration of the product machine state graph to do equivalence checking for two circuits without identical state encodings. These tools can handle the large designs with similar structures. However, these tools can not handle the equivalent designs with little structure similarity. For example, an array multiplier and a booth-encoding multiplier can not be proved to be equivalent using these tools. Another drawback of equivalence checkers is that they all need "golden" circuits as the reference to be compared with. The correctness of "golden" circuits is still questionable.

#### Hybrid approaches: Theorem prover with model checking or simulation

Another approach to verifying circuits is combining a theorem prover with a model checking or symbolic simulation tool [85, 65]. In this approach, theorem provers handle the high-level proofs, while the low-level properties are handled by the model checking or symbolic simulation tool.

Camilleri [25] used simulation as an aid to perform verification of circuits using the HOL theorem prover. Kurshan *et al* [71] verified local properties of the low-level circuits of a multiplier using COSPAN and verified the correctness of the whole multiplier by a theorem prover to compose of the verified local properties. Aagaard *et al* [1] used Voss and a theorem prover to verify a IEEE double-precision floating-point multiplier. Compared with the theorem proving approach, this approach is much more automatic, but still requires user guidance.

#### **Other Approaches**

Burch [22] has implemented a BDD-based technique for verifying certain classes of integer multipliers. His method effectively creates multiple copies of the multiplier variables, leading to BDDs that grow cubically with the word size. The limiting factor in dealing with larger word sizes would be the cubic growth in memory requirement. Furthermore, this approach cannot handle multipliers that use multiplier recoding techniques, although Burch describes extensions to handle some forms of recoding.

Jain et al [62] have used Indexed Binary Decision Diagrams (IBDDs) to verify several multiplier circuits. This form of BDD allows multiple repetitions of a variable along a path from root to leaf. They were able to verify C6288 (a 16-bit multiplier) in 22 minutes of CPU time on a SUN-4/280, generating a total of 149,498 graph vertices. They were also able to verify a multiplier using Booth encoding, but this required almost 4 hours of CPU time and generated over 1 million vertices in the graphs.

Based on the Chinese remainder theorem, Kimura [69] introduced residue BDDs, which have bounded size, to verify a  $16 \times 16$  integer multiplier. In [86], Ravi *et al* discuss how to choose a good modulus and also show how to build residue BDDs for complex circuits involving function blocks. They have shown that this approach can detect the bugs efficiently. However, this approach cannot be extended to verify larger integer multipliers such as 64-bit multipliers.

Bryant [17] has used BDD to check the properties and invariants that one iteration of the SRT circuits must preserve for the circuit to correctly divide. To do the verification, he needed to construct a gate-level checker-circuit (much larger than the verified circuit) to describe the desired behavior of the verified circuit, which is not the ideal level of specification.

11

## 1.3 Scope of the thesis

Approaches based on decision diagrams have been used to verify arithmetic circuits. However, direct application of decision diagrams in this domain is not without challenges. We classify these challenges into two categories – *representation* and *methodology*. The main representation challenges are to overcome the explosion problem of the existing decision diagrams and to provide a compact representation for integer and floating-point functions such that the specification can be easily be expressed in word level. The methodology related challenges includes problems like having a framework to specify and verify arithmetic properties, automating the verification process, and making the specification reusable. We have built on earlier work on decision diagrams and methodologies to overcome these challenges. The principal contributions of this thesis are the following:

- \*BMD-based hierarchical verification for integer circuits

We have developed \*BMDs to represent integer functions efficiently and thus have enabled

the verification of integer circuits. Based on \*BMDs and a hierarchical verification

methodology, we have built a system to verify several integer circuits such as integer

multipliers, dividers and square roots.

- Representation for floating-point functions

We have developed \*PHDDs to represent floating-point functions efficiently. We also have analyzed the complexities of representing floating-point addition and floating-point multiplication using \*PHDDs.

- Methodologies for verification of floating-point circuits

We have developed several methodologies for the verification of floating-point circuits, especially floating-point adders. These methodologies have been integrated into word-level SMV.

- Verification of floating-point adders and conversion circuits

A FP adder designed by Dr. Huff at the University of Michigan was verified by our approach with reusable specifications. Several bugs were found in the design. A counterexample for each bug can be generated within 5 minutes. The reusability of our specifications is demonstrated by the verification of a variant of Huff's FP adder.

#### 1.4 Thesis overview

Chapter 2 presents Multiplicative Binary Moment Diagrams (\*BMDs) which enable the verification of arithmetic circuits. The data structures and algorithms for \*BMDs provide a compact

representation for integers functions.

Chapter 3 discusses the verification of integer circuits such as multipliers, dividers and square roots. A hierarchical verification method based on \*BMDs is presented for verification of integer circuits along with other methods. Based on these methodologies, the Arithmetic Circuit Verifier (ACV) was built to verify integer multipliers, dividers and square roots.

Chapter 4 presents Multiplicative Power Hybrid Decision Diagrams (\*PHDDs) for the verification of floating-point circuits. First, we discuss the limitations of \*BMDs and HDDs and thus the need for a new diagram to represent floating-point functions. A performance comparison between \*BMDs and \*PHDDs is discussed.

Chapter 5 discusses methodologies for verification of floating-point circuits, especially floating-point adders. First, we discuss the drawbacks of ACV which lead us to verify flattened designs of floating-point circuits. Then, we present several improvements of word-level SMV to enable the verification of floating-point circuits.

Chapter 6 presents the verification work of a floating-point adder obtained from the University of Michigan. We discuss the circuit design of this FP adder and the reusable specifications for FP adders. Several bugs were found in this design by our system. A variant of this FP adder is created and verified to illustrate that our approach is implementation independent.

Chapter 7 rounds off the thesis with an evaluation of the work and possible future research directions.

The appendix shows the complexity analysis of representing floating-point addition and multiplication using \*PHDDs.

## Chapter 2

## **Representations for Integer Functions**

To verify integer arithmetic circuits, we must have concise representations for word-level functions that map Boolean vectors to the integer values. Such Boolean vectors correspond to the input operands and the final result. In this chapter, we discuss Multiplicative Binary Moment Diagrams (\*BMDs) which provide a compact representation for integer functions. \*BMDs have efficient representations for common integer encodings as well as operations such as addition and multiplication, and enable us to easily verify integer circuits such as multipliers and dividers. The verification of these circuits will be described in Chapter 3.

Section 2.1 presents the data structure for \*BMDs. The \*BMD representations of integer functions and operations are shown in Section 2.2. Then, the algorithms for \*BMDs are presented in Section 2.3. Section 2.4 describes the related work.

#### 2.1 The \*BMD Data Structure

\*BMDs represent functions having Boolean variables as arguments and numeric values as results. Their structure is similar to that of Ordered BDDs, except that they are based on a "moment" decomposition, and they have numeric values for terminal values and edge weights. As with OBDDs we assume there is some total ordering of the variables such that variables are tested according to this ordering along any path from the root to a leaf.

### 2.1.1 Function Decompositions

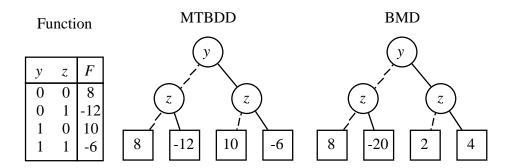

To illustrate ways of decomposing a function, consider the function F over a set of Boolean variables y and z, yielding the integer values shown in the table of Figure 2.1. BDDs are

Figure 2.1: **Example Function Decompositions.** MTBDDs are based on a pointwise decomposition (left), while BMDs are based on a linear decomposition (right).

based on a pointwise decomposition, characterizing a function by its value for every possible set of argument values. By extending BDDs to allow numeric leaf values, the pointwise decomposition leads to a "Multi-Terminal" BDD (MTBDD) representation of a function [34] (also called "ADD" [4]), as shown on the left side of Figure 2.1. In this drawing, the dashed line from a vertex denotes the case where the vertex variable is 0, and the solid line denotes the case where the variable is 1. Observe that the leaf values correspond directly to the entries in the function table.

Exploiting the fact that the function variables take on only the values 0 and 1, we can write a linear expression for function F directly from the function table. For variable y, the assignment y=1 is encoded as y, and the assignment y=0 is encoded as 1-y. Expanding and simplifying the resulting expression yields:

$$F(x,y) = \begin{bmatrix} 8 & (1-y) & (1-z) & + \\ -12 & (1-y) & z & + \\ 10 & y & (1-z) & + \\ -6 & y & z & \end{bmatrix}$$

$$= 8 - 20z + 2y + 4yz$$

This expansion leads to the BMD representation of a function, as shown on the right side of Figure 2.1. In our drawings of graphs based on a moment decomposition, the dashed line from a vertex indicates the case where the function is independent of the vertex variable, while the solid line indicates the case where the function varies linearly. Observe that the leaf values correspond to the coefficients in the linear expansion.

Generalizing from this example, one can view each vertex in the graphical representation of a function as denoting the decomposition of a function with respect to the vertex variable. The different representations can be categorized according to which decomposition they use.

Boolean function f can be decomposed in terms of variable x in terms of an expansion (variously credited to Shannon and to Boole):  $f = \overline{x} \wedge f_{\overline{x}} \vee x \wedge f_x$ . In this equation we use  $\wedge$  and  $\vee$  to represent Boolean sum and product, and overline to represent Boolean complement. Term  $f_x$  (respectively,  $f_{\overline{x}}$ ) denotes the positive (resp., negative) *cofactor* of f with respect to variable x, i.e., the function resulting when constant 1, (resp., 0) is substituted for x. This decomposition is the basis for the BDD representation.

For expressing functions having numeric range, the Boole-Shannon expansion can be generalized as:

$$f = (1-x) \cdot f_{\overline{x}} + x \cdot f_x \tag{2.1}$$

where  $\cdot$ , +, and - denote multiplication, addition, and subtraction, respectively. Note that this expansion relies on the assumption that variable x is Boolean, i.e., it will evaluate to either 0 or 1. Both MTBDDs and EVBDDs [73] are based on such a pointwise decomposition. As with BDDs, each vertex describes a function in terms of its decomposition with respect to the variable labeling the vertex. The two outgoing arcs denote the negative and positive cofactors with respect to this variable.

The moment decomposition of a function is obtained by rearranging the terms of Equation 2.1:

$$f = f_{\overline{x}} + x \cdot (f_x - f_{\overline{x}})$$

=  $f_{\overline{x}} + x \cdot f_{\delta x}$  (2.2)

where  $f_{\delta x} = f_x - f_{\overline{x}}$  is called the *linear moment* of f with respect to x. This terminology arises by viewing f as being a linear function with respect to its variables, and thus  $f_{\delta x}$  is the partial derivative of f with respect to f. Since we are interested in the value of the function for only two values of f, we can always extend it to a linear form. The negative cofactor will be termed the *constant moment*, i.e., it denotes the portion of function f that remains constant with respect to f. Each vertex of a BMD describes a function in terms of its moment decomposition with respect to the variable labeling the vertex. The two outgoing arcs denote the constant and linear moments of the function with respect to the variable.

The moment decomposition of Equation 2.2 is analogous to the Reed-Muller expansion for Boolean functions:  $f = f_{\overline{x}} \oplus x \wedge (f_x \oplus f_{\overline{x}})$ . The expression  $f_x \oplus f_{\overline{x}}$  is commonly known as the *Boolean difference* of f with respect to f, and in many ways is analogous to our linear moment. Other researchers [68] have explored the use of graphs for Boolean functions based on this expansion, calling them Functional Decision Diagrams (FDDs). By our terminology, we would refer to such a graph as a "moment" diagram rather than a "decision" diagram.

### 2.1.2 Edge Weights

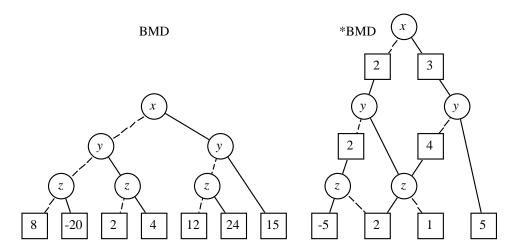

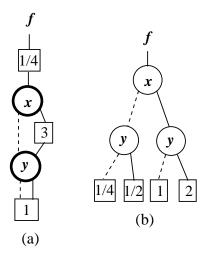

Figure 2.2: **Example of BMD vs. \*BMD.** Both represent the function 8 - 20z + 2y + 4yz + 12x + 24xz + 15xy. \*BMDs have weights on the edges that combine multiplicatively.

The BMD data structure encodes numeric values only in the terminal vertices. As a second refinement, we adopt the concept of edge weights, similar to those used in EVBDDs. In our case, however, edge weights combine multiplicatively, and hence we call these data structures \*BMDs. As an illustration, Figure 2.2 shows representations of the function 8 - 20z + 2y + 4yz + 12x + 24xz + 15xy. In the BMD representation, leaf values correspond to the coefficients in the linear expansion. As the figure shows, the BMD data structure misses some opportunities for sharing of common subexpressions. For example, the terms 2y + 4yz and 12x + 24xz can be factored as 2y(1 + 2z) and 12x(1 + 2z), respectively. The representation could therefore save space by sharing the subexpression 1 + 2z. For more complex functions, one might expect more opportunities for such sharing.