# A Quantitative Approach to the Formal Verification of Real-Time Systems

Sérgio Vale Aguiar Campos

September 1996 CMU-CS-96-199

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy

Thesis Committee:

Edmund M. Clarke, Chair

Rance Cleaveland, North Carolina State University

Daniel Jackson

John P. Lehoczky

© 1996 Sérgio Vale Aguiar Campos

This research was sponsored in part by the National Science Foundation under grant no. CCR-9217549, by the Semiconductor Research Corporation under contract 95-DJ-294, and by the Wright Laboratory, Aeronautical Systems Center, Air Force Materiel Command, USAF, and the Advanced Research projects Agency (ARPA) under grant F33615-93-1-1330.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of NSF, the Semiconductor Research Corporation, ARPA or the U.S. government.

Keywords: real-time systems, formal verification, symbolic model checking, binary decision diagrams, rate-monotonic scheduling, schedulability, quantitative timing analysis, Verus language, CTL, LTL, FDDI, Futurebus, PCI Local Bus, robotics controller, aircraft controller.

## Carnegie Mellon

## **School of Computer Science**

#### DOCTORAL THESIS in the field of Pure and Applied Logic

A Quantitative Approach to the Formal Verification of Real-Time Systems

#### S'ERGIO VALE AGUIAR CAMPOS

Submitted in Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy

| ACCEPTED:                               |          |      |

|-----------------------------------------|----------|------|

| Edmind M. Clarke THESIS COMMITTEE CHAIR | 12/18/96 | DATE |

| Menie                                   | 12/18/96 |      |

| DEPARTMENT HEAD                         |          | DATE |

| APPROVED:                               |          |      |

| TS: TOUS DEAN                           | 1/28/97  | DATE |

### **Abstract**

The task of checking if a computer system satisfies its timing specifications is extremely important. These systems are often used in critical applications where failure to meet a deadline can have serious or even fatal consequences. This work proposes an efficient method for performing this verification task. The method is based on temporal logic model checking, a technique for verifying concurrent reactive systems. In the proposed technique, a real-time system is modeled by a state-transition graph represented by binary decision diagrams. Efficient symbolic algorithms exhaustively explore the state space to determine whether the system satisfies a given specification.

In addition to accepting an explicit timing constraint, and checking if it is satisfied, our approach computes quantitative timing information such as minimum and maximum time delays between given events. These results provide insight into the behavior of the system as well as assist in the determination of its temporal correctness. The technique evaluates how well the system works or how seriously it fails, as opposed to only if it works or not, allowing a much richer analysis than previous methods. Response time to events, schedulability of a task set and system performance are examples of information produced by our algorithms. They also provide insight into how changes in the parameters affect global behavior and allow fine-tuning of the system based on these results.

These techniques have been used in the verification of several industrial real-time systems such as an aircraft controller, a robotics system and the PCI local bus, demonstrating that the method proposed is efficient enough to be used in real-world designs. The examples show how the information produced can assist in designing more efficient and reliable real-time systems.

Abstract

"You must remember this, a kiss is just a kiss, A sigh is just a sigh; The fundamental things apply, As time goes by."

— Herman Hupfeld.

Abstract

## Acknowledgments

To my wife Alessandra, for providing complete unrestricted support whenever I needed it, even when I didn't deserve it. But even more important, for giving me a reason to go on, for being the light at the end of my tunnel. There would be no reason for writing this thesis without her.

To my advisor Edmund Clarke, for the incredible amount of time he spent with me, from the beginning when he patiently listened to my so wrong ideas about verification to the end when he always found the time to read and comment on the thesis. For teaching me so much not only about formal verification, but also about all aspects of research, from writing papers that can actually be understood to grant proposals that can actually be accepted. If I ever succeed in becoming a good researcher I will be using what he has taught me.

To Marius Minea, for the many long discussions on formal verification and all other topics. For all the help with ideas on how to do things, prove the algorithms, comments and suggestions on papers we've written and on this thesis. It's been a pleasure working with Marius all this time, and I hope we can continue to work together.

To David Long, a former student of Ed, for the patience to explain to me everything I've always wanted to know about model checking but couldn't find anyone with enough time to answer. And for continuing to help with so many other questions after he left CMU by patiently answering my e-mails and phone calls.

#### **Acknowledgments**

To Orna Grumberg, for showing me a very special style of doing research. She is clear, concise and very efficient. It is a pleasure to work with Orna, whose style I've been trying to learn. Unfortunately, I still have a long way to go.

To many other researchers that have helped me. To Andreas Kuehlmann from IBM for the original insight behind the optimized condition counting algorithms. To Ken McMillan, Jerry Burch, Xudong Zhao and Somesh Jha for the many important discussions that helped shape this work. To the Real-Time Mach group members, particularly R. Rajkumar for many discussions about real-time systems and how to verify them.

To the members of my committee, Rance Cleaveland, Daniel Jackson and John Lehoczky for trying to understand all my crazy ideas and not only succeeding (in some cases better than me), but also for helping me understand them better as well. Their comments and suggestions have made this thesis significantly better.

To my parents Lia and Daniel and to my sister Daniela, for the help and support throughout my whole life. Even though they have not been present during my Ph.D., without their support I would not have been able to be here.

## **Table of Contents**

|           | Abstract 3                                                                                                                                                                  |  |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| •         | Acknowledgments 7                                                                                                                                                           |  |  |  |

|           | Table of Contents 9                                                                                                                                                         |  |  |  |

| Chapter 1 | Overview 13                                                                                                                                                                 |  |  |  |

|           | Motivation 13                                                                                                                                                               |  |  |  |

|           | Verification Tools for Real-Time Systems 15                                                                                                                                 |  |  |  |

|           | The Proposed Approach 18                                                                                                                                                    |  |  |  |

|           | Modeling a Real-Time System 20                                                                                                                                              |  |  |  |

|           | The Verus Language 21                                                                                                                                                       |  |  |  |

|           | Verification Algorithms 22                                                                                                                                                  |  |  |  |

|           | Analysis of the results 25 Summary and Main Contributions 27                                                                                                                |  |  |  |

|           | Summary and Iviam Controlutions 27                                                                                                                                          |  |  |  |

| Chapter 2 | Related Approaches 31                                                                                                                                                       |  |  |  |

|           | Temporal Logic Symbolic Model Checking 31  Computation Tree Logic 33  Symbolic Model Checking 35  Verus and Symbolic Model Checking 41  Rate Monotonic Scheduling Theory 42 |  |  |  |

|           |                                                                                                                                                                             |  |  |  |

#### **Table of Contents**

The Liu and Layland Theory 42

Extensions of the Liu and Layland Theory 45

Verus and the Rate Monotonic Theory 48

#### Chapter 3

#### The Verus Language 51

Introduction 51

Overview of Verus 52

Verus Syntax 60

#### Chapter 4

#### The Semantics of Verus 65

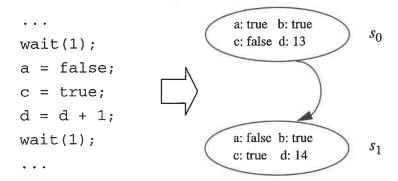

State-Transition Graphs in Verus 65

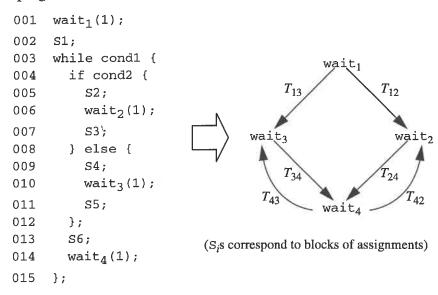

Tracking the Control Flow — Wait Graphs 67

Core Language Semantics 71

Expressions 73

Statements 75

Verus Extension Semantics 78

The Semantics of Concurrency in Verus 82

#### **Chapter 5**

#### Verification Algorithms 87

RTCTL Model Checking 87

Quantitative Analysis: Minimum/Maximum Delay 89

Minimum Delay Algorithm 90

Maximum Delay Algorithm 92

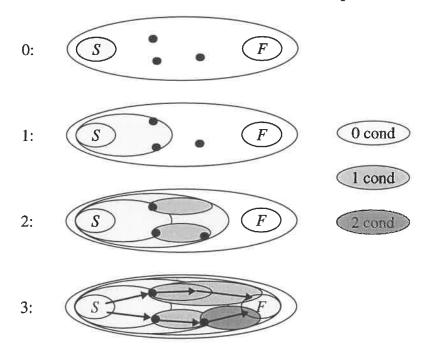

Quantitative Analysis: Condition Counting 96

Minimum Condition Counting 97

Maximum Condition Counting 101

Quantitative Analysis: Optimized Condition Counting 101

Optimized Minimum Condition Counting 102

Optimized Maximum Condition Counting 106

Selective Quantitative Analysis and

Interval Model Checking 109

A tableau for LTL 111

Selective Quantitative Analysis Over Paths 116

Selective Quantitative Analysis Over Intervals 117

Interval Model Checking 120

Correctness of the Algorithms 121

Lazy Composition 136

Chapter 6

Analyzing Real Systems 141

A Priority Inversion Example 141

An Aircraft Controller 157

A Robotics System 165

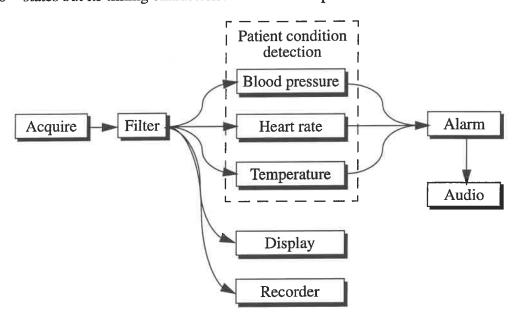

A Medical Monitoring System 170

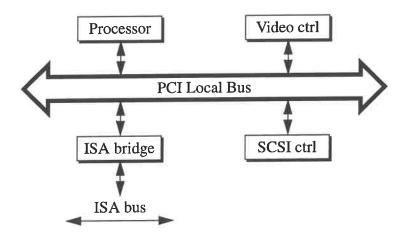

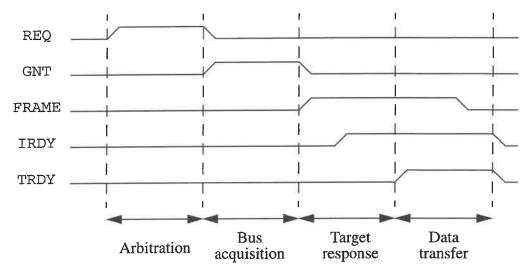

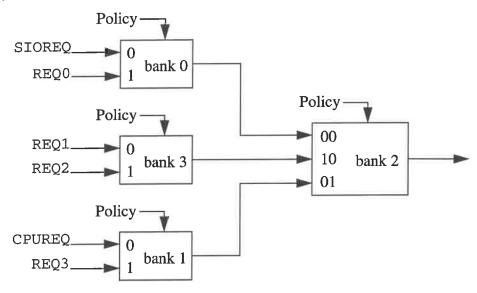

The PCI Local Bus 175

A Distributed Real-Time System 186

Chapter 7

Conclusions 193

**Chapter 8**

References 199

Index 207

**Table of Contents**

## Chapter 1 Overview

#### 1.1 Motivation

In many computer applications predictable response times are essential for the correctness of the system. Such systems are called *real-time systems*. They occur in many critical applications in which a late (or sometimes early) response can have severe consequences. Examples of such applications include controllers for aircraft, industrial machinery and robots. Due to the nature of such applications, errors in real-time systems can be extremely dangerous, even fatal. Guaranteeing the correctness of a complex real-time system is an important and non-trivial task. Because of this, only conservative and usually ad hoc approaches to design and implementation are routinely used. This leads to predictable but inefficient designs. The use of modern software engineering techniques can improve the efficiency of these systems without forgoing predictability. Recently, the development of methods such as the *rate monotonic scheduling theory* [53,59,68] has helped increase the popularity of formal approaches by providing designers with powerful tools for analyzing real-time systems. Current real-time designs incorporate these ideas with increasing frequency.

Other factors make the validation of real-time and non real-time systems particularly difficult. The architecture of computer applications is becoming more and more complex each

day. The more complex a system, the higher the possibility of errors being introduced in its design. Moreover, performance is also becoming a more important factor in the success of new applications. Due to competition, new products have to fully utilize the available resources. A slow component can compromise the performance of the whole system, and consequently its acceptance by the market. Although not traditionally associated with real-time systems, verifying timing properties of these applications is also critical. The task of verifying that new applications satisfy their timing specifications is more critical and difficult today than ever.

The main objective of this work is to explore the application of formal methods to the validation of real-time systems. Methods such as temporal logic model checking [10,19,20] have been very successful in validating realistic industrial designs. Model checking techniques have the ability to verify designs with extremely large state spaces efficiently. Models with up to 10<sup>20</sup> states can be verified in minutes [10,15]. Methods such as rate monotonic theory offer an elegant way of analyzing the performance of a real-time system. We have developed a tool for the analysis of real-time systems by combining ideas from both techniques. This tool allows the user to define a real-time system using a language especially designed to simplify the description of time related characteristics. Algorithms derived from model checking are used to extract quantitative properties of such a model. This information is used to check if the system does indeed satisfy its temporal specifications. Moreover, our algorithms provide an insight into the behavior of the system, helping to understand and optimize its design. We believe that the use of formal methods can increase the efficiency and reliability of systems in general, and particularly of real-time systems. It is our hope that this work and its future extensions can contribute to this goal and open new possibilities in the design of efficient and reliable real-time and non real-time systems.

#### 1.2 Verification Tools for Real-Time Systems

#### **Temporal Logic Model Checking**

Temporal logic model checking [19,20] is an approach for the verification of concurrent systems that has achieved significant results recently. In this technique, computer systems are represented by state-transition graphs and specifications are written as formulas in a propositional temporal logic. Verification is accomplished by an efficient search procedure that views the transition system as a model for the logic, and determines if the specifications are satisfied by that model.

There are several benefits to this approach. An important one is that the procedure is completely automatic. The model checker accepts a model description and logic formulas describing the specifications; it then determines if the formulas are true or not for that model. If a formula is not true, the model checker can often provide a *counterexample*. The counterexample is an execution trace that shows why the formula is not true. This is an extremely useful feature because it can help locate the source of the error and speed up the debugging process. Another benefit is the ability to verify partially specified systems using *nondeterminism*. If the behavior of the component that determines the value of a given variable hasn't been specified, the variable can be assigned any possible value non-deterministically. The actual behavior of the variable is a subset of the modelled behavior, and useful information about correctness can be gathered before all the details have been determined. This allows the verification to proceed concurrently with the design.

The concept of *symbolic model checking* has been developed later [10,62]. In this approach the transition relation is represented implicitly by boolean formulas, and implemented by *binary decision diagrams* [6]. This usually results in a much smaller representation for the transition relation and set of reachable states, allowing the size of the models being verified to increase up to more than 10<sup>20</sup> states. By using such techniques it has become possible to verify realistic industrial systems formally. Significant results have been achieved, such as the verification of the Futurebus<sup>+</sup> protocol, adopted by the U.S. Navy [23]. That work has uncovered protocol errors that were not previously known.

It is possible to use symbolic model checking to verify real-time systems. However, current tools have limitations that make it difficult to perform this verification. It is difficult, for example, to express timing properties. It is possible to express the property that "event p will happen in the future", but it is not simple to express the property that "event p will happen in at most p time units". Moreover, quantitative information such as response time or the number of occurrences of events cannot be directly obtained using these techniques. Pure symbolic model checking cannot be used in a natural and efficient way to verify many types of real-time systems that occur frequently in practice.

#### **Rate Monotonic Scheduling Theory**

Because real-time systems are used in critical applications, until recently only conservative approaches have been commonly used in their design, leading to simple but inefficient designs. One example of such a safe technique is static time-slicing, which divides time equally among all tasks. Each task executes until its time slot has been used and then releases the processor. The resulting program is very simple to analyze, but rather inefficient, since all tasks are given equal resources, regardless of their importance or resource utilization. Recently, more powerful techniques to analyze the behavior of a real-time system have become more popular. The rate monotonic scheduling theory (RMS) [53,59,68] is one example. The RMS theory is applicable to systems described by a set of periodic tasks. It consists of two components, the first being an algorithm for assigning priorities to tasks in order to maintain predictability. This algorithm assigns higher priorities to processes with shorter periods. Optimal response time with respect to static priority algorithms is guaranteed by the RMS theory if priorities are assigned according to this rule [59]. The second component of the RMS theory is a schedulability test based on total CPU utilization; a set of processes (which have priorities assigned according to RMS) is schedulable if the total utilization is below a computed threshold. If the utilization is above this threshold, schedulability is not guaranteed. RMS is a powerful tool for analyzing real-time systems. It is simple to use, yet it provides very useful information for designers.

However, this analysis imposes a series of restrictions on the set of processes. Only certain types of processes are considered, with limitations, for example, on periodicity and syn-

#### **Verification Tools for Real-Time Systems**

chronization. Recent work has extended this theory to more general classes of processes, but limitations still exist [38]. Although suited to the verification of real-time systems, RMS can only handle systems that can be described within the theory. Moreover, the types of properties that can be verified is also restricted to properties that can be modeled as task execution times. Verifying different types of systems such as distributed systems or systems that do not have a regular communication pattern is not a trivial task in general. The task of checking for properties that cannot be easily expressed as task execution times such as the number of occurrences of arbitrary events in the system can also be complex.

#### Other Methods

Another approach to schedulability analysis uses algorithms for computing the set of reachable states of a finite-state system [18,35,36]. A model for the real-time system is constructed with the added constraint that whenever an exception occurs (e.g. a deadline is missed) the system transitions to a special exception state. Verification consists of computing the set of reachable states and checking whether the exception state is in this set. No restrictions are imposed on the model in this approach, but the algorithm only checks if exceptions can occur or not. Other types of properties cannot be verified, unless encoded in the model as exceptions. Even though most properties can be encoded as exceptions, this can sometimes be difficult and error-prone. Symbolic model checking techniques have also been extended to handle real-time systems [28,29,77]. However, these methods as well as the others mentioned only determine if the system satisfies a given property, and do not provide detailed information on its behavior. Restricted quantitative analysis on discrete-time models can be performed in [27], but only to the extent of computing minimum/maximum delays.

In this work we use a discrete notion of time. In recent years, there has been considerable research on algorithms that use continuous time [1,2,34,39,41,55,63]. Most of these techniques use a transition relation with a finite set of real-valued clocks and constraints on times when transitions may occur. It can be argued that such algorithms lead to more accurate results than discrete time algorithms. However, an uncountable infinite state space is required to handle continuous time, because the time component in the states can take

arbitrary real values. Most verification procedures based on this paradigm depend on constructing a finite quotient space called a *region graph* out of the infinite state space. Unfortunately, the region graph construction is very expensive in practice and current implementations of the algorithms can only handle quotient spaces with at most a few thousand states. This makes it impossible to verify large complex systems such as the ones described in chapter 6 using continuous time tools. Dense time models in which restricted quantitative analysis can be performed can be found in [42,75].

#### 1.3 The Proposed Approach

In this work we propose a new method for specifying and verifying real-time systems. The system being verified is specified in the *Verus* language and then compiled into a state-transition graph. Algorithms derived from symbolic model checking are used to compute *quantitative* information about the model. An important benefit of this approach is that the Verus language has been especially designed to allow a straightforward description of the temporal characteristics of programs. Another advantage is that the information produced allows the user to check the temporal correctness of the model: schedulability of the tasks of the system can be determined by computing their response time; reaction times to events and several other parameters of the system can also be analyzed by this method. This information provides insight into the behavior of the system and in many cases it can help identify inefficiencies and suggest optimizations to the design. The same algorithms can then be used to analyze the performance of the modified design. The evaluation of how the optimizations affect the design can be done *before* the actual implementation. This can significantly reduce development costs.

Other advantages of our approach include the fact that the Verus code serves as a precise description for the system, which can uncover subtle ambiguities and can be used for documentation purposes. Also, because we use a discrete notion of time, we are able to take advantage of symbolic techniques in which the transition relation is represented by a

#### The Proposed Approach

binary decision diagram. This enables us to handle systems that are several orders of magnitude larger than can be handled using continuous time techniques.

Our method extends several others that have been mentioned. The model of a real-time system, and the algorithms for exploring the state space are derived from model checking. However, the method proposed allows the natural expression of many types of real-time properties that cannot be easily described in the original method, such as properties that depend on the exact timing behavior of the system. The definition of real-time system, and of its main characteristics are derived from the rate monotonic theory. But unlike RMS, our approach does not impose *a priori* restrictions on the types of systems and properties being verified. Limitations do exist, however, due mostly to the complexity of the verification algorithms. But they do not depend on the structure of the system, only on the amount of time and memory required for verification.

An important characteristic of the method proposed is that it counts the number of computation steps between events, or the number of occurrences of events in an interval. Because of this it finds application in synchronous systems in general, such as computer circuits and protocols. Real-time systems usually do not execute in lock-step, and would not seem to be appropriate for our method. However, they are subject to tight timing constraints, which are difficult to satisfy in an asynchronous design. For this reason real-time system developers often significantly reduce asynchronism in their designs to ensure predictability. In fact, most real-time systems we have analyzed are more synchronous than traditional circuits, and have been successfully verified using the method proposed [13,14,16].

The main limitation of our approach is the inherent complexity of the model checking problem. Constructing the model has an exponential asymptotic complexity in the number of components and there are no guarantees that our algorithms will terminate in any practical sense. However, we have achieved good success in this area; in most cases verification is performed in minutes, even for complex real-world systems. It must be said, however, that these problems are inherent to formal verification of timed systems, and that we know of no approach that has solved them.

The remainder of the chapter gives an overview of the proposed method. We describe how a real-time system is modeled as a state-transition graph, and present the Verus language, used to describe the system being verified. We then briefly explain how the verification algorithms work, and how these results can be used to analyze real systems. We conclude the chapter by outlining the main contributions of this work.

#### 1.3.1 Modeling a Real-Time System

A model of the system in our algorithms is a labeled state-transition graph M. The labels correspond to the values of the variables in the program, and transitions correspond to the passage of time in the model. The key to the efficiency of the algorithms is to use BDDs to represent the labeled state-transition graph and to verify if the formula is true or not.

In this method transitions are represented by boolean formulas. A formula f represents a transition between states s and s' iff the formula is true when we substitute the variable values in states s and s' for the variables in f (using different variables for current and next state). The formula f is represented by a BDD. Details about this representation can be found in Section 4.1 and [8,62].

#### Lazy composition

In the vast majority of cases a real-time system is described by a set of processes that execute concurrently. Given the transition relation for each process, a parallel composition algorithm constructs the global transition relation of all processes and their interaction. The composition algorithm is essential to the verification of non-trivial real-time systems. It is, however, extremely expensive. The number of states of a composed model can be exponential in the number of processes. The complexity of the composition algorithm is the main limiting factor on the size of systems being verified. We propose a new approach in process composition called *lazy composition*. The basic idea is to avoid composing processes whenever possible, performing the operation only when necessary.

#### The Proposed Approach

With the new technique the composition algorithm is applied at each time the verifier computes the image or pre-image of a state set. When computing the image of a state set S, we are only interested in transitions that start in S. At this point the lazy composition algorithm reduces the transition relations of each process by simplifying and possibly eliminating transitions that do not start in S. The resulting transition relations are often much simpler than the original ones, while preserving all transitions that start in S. The simplified relations are then composed and the normal image computation algorithm can be applied. Significant gains in time and space during verification can be accomplished by this method.

#### 1.3.2 The Verus Language

We have designed a new language to be used as the specification language for the real-time systems verified. The main goal of this language is to allow engineers and designers to describe real-time systems easily and efficiently. It is an imperative language with a syntax resembling that of C. Special primitives are provided to express of timing aspects such as deadlines, priorities, and time delays. The available data types are integer and boolean. Nondeterminism is supported, which allows partial specifications to be described. The language constructs have been kept simple in order to make an efficient compilation into a state-transition graph possible. Smaller representations can then be generated, which is critical to the efficiency of the verification and permits larger examples to be handled.

There are several other languages for specifying finite-state real-time systems. However, they are suited for different applications, and usually only allow a natural description of characteristics that are typical of those applications. For example, Lustre [72] and Signal [37] are languages for describing sequential circuits. They are declarative languages, and in this sense they resemble the SMV language [62], used for describing circuits in our original symbolic model checker. In these languages one describes explicitly the relationship between variables, but not the flow of control. Imperative languages take the opposite approach, by explicitly describing the control flow. Declarative languages, however, do

not provide a natural way of describing real-time programs, usually implemented on imperative languages. In fact, our experience with SMV was the motivation for developing Verus.

Esterel [5], on the other hand, is an imperative language, better suited for describing programs. Its syntax, however, may be very unfamiliar to most designers of real-time systems, used to program in C or similar languages. Moreover, Esterel constructs, unlike those of Verus, have not been designed to simplify modeling real-time systems. For example, specifying the execution of a periodic process with a deadline is not as straightforward as in Verus. Finally, Esterel is a deterministic language; it does not allow the expression of nondeterminism. Modechart [47] is another example of real-time specification language. It is a graphical language in which nodes represent states, and transitions are explicitly drawn between states. This language, however, is more restrictive than Verus due to its graphical nature. Complex constructs such as periodic may be difficult to draw. Moreover, it is an explicit state enumeration language, since individual states are drawn in the program. Many systems are too large to be naturally described using graphical languages.

A different approach is taken in Spin [43] and Murφ [30]. These systems use languages that resemble C, but that have actually a significantly different semantics. Modeling a system originally written in C in one of these systems may cause confusion between a similar syntax, but different semantics. Moreover, both systems are better suited to verify asynchronous designs. Their languages have been designed to allow the straightforward expression of such systems. It is not clear how natural or efficient it is to write a synchronous program in one of these languages.

#### 1.3.3 Verification Algorithms

In the previous section we have described how to model a real-time system in a form amenable to formal analysis. This section will describe the algorithms that perform this analysis. The types of properties that can be expressed are also discussed.

#### The Proposed Approach

#### **Real-Time CTL Model Checking**

Computation Tree Logic, CTL, is the temporal logic used in our verification system [19,20]. In CTL it is possible to express properties such as "p will eventually occur", or "p will never be asserted". However, it is not possible to express bounded properties such as "p will occur in less than 10ms" directly. Properties such as this can only be expressed using nested next state operators. However, the resulting formula can be very complex and cumbersome to work with. The bounded until operator overcomes this restriction by allowing bounds on all CTL operators to be specified [33]. It has the form:  $U_{[a,b]}$ , where [a,b] defines the time interval in which the property must be true. Informally,  $fU_{[a,b]}g$  is true of some path if g holds in some future state s on the path, s is true in all states between state s at the beginning of the path and s, and the distance from s to s is within s and s. All other CTL temporal operators are defined in terms of the bounded until [11]. The logic obtained by augmenting CTL with bounded operators is called RTCTL.

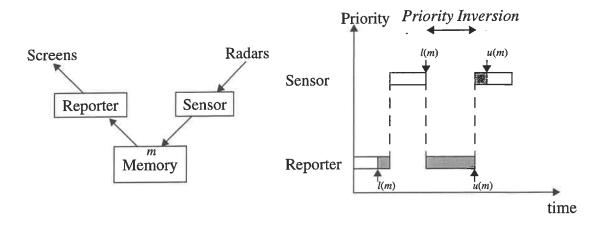

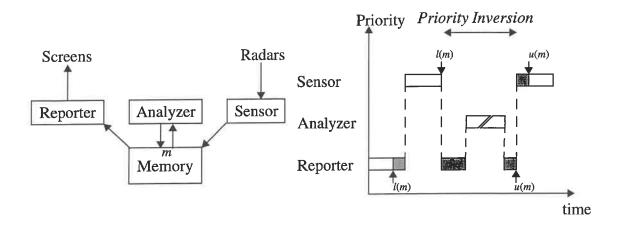

The new logic allows many important properties of real-time systems to be verified. For example, we have used it to show the existence of priority inversion [66] in a real-time system [11]. In this example, we have modeled a simple real-time system in which processes communicate in a non-regular pattern. The main objective is to determine which problems can arise from this communication and how to avoid them. The bounded until operator has allowed us to determine the existence of priority inversion, and to check that the solution implemented, priority inheritance, avoids the problem.

We have also used RTCTL model checking in several other occasions to verify time bounded properties of real-time and non real-time systems. Some examples include verifying that an industrial communications circuit would *not* meet its timing specification [78] and the verification of the generalized railroad crossing example [40].

#### **Quantitative Algorithms**

Most verification algorithms assume that timing constraints are given explicitly in some notation like temporal logic. Typically, the designer provides a constraint on response time for some operation, and the verifier automatically determines if it is satisfied or not. Unfortunately, these techniques do not provide any information about how much a system deviates from its expected performance, although this information can be extremely useful in fine-tuning the behavior of the system.

We present algorithms that determine the minimum and maximum length of all paths leading from a set of starting states to a set of final states. We also present algorithms that calculate the minimum and the maximum number of times a specified condition can hold on a path from a set of starting states to a set of final states. Our algorithms provide insight into *how well* a system works, rather than just determining whether it works at all. They enable a designer to determine the timing characteristics of a complex system given the timing parameters of its components. This information is especially useful in the early phases of system design, when it can be used to establish how changes in a parameter affect the global behavior of the system.

Several types of information can be produced by this method. Response time to events is computed by making the set of starting states correspond to the event, and the set of final states correspond to the response. Schedulability analysis can be done by computing the response time of each process in the system, and comparing it to the process deadline. Performance can be determined in a similar way. The algorithms have been used to verify several real-time and non real-time systems. Several examples of systems verified are discussed in later chapters.

#### Selective Quantitative Analysis and Interval Model Checking

The algorithms described above compute the minimum and maximum time delays along *every* possible execution sequence of a real-time system. In many situations, however, we may be interested in computing time delays that relate only to a subset of the execution sequences that satisfy a given property. For example, in the aircraft controller example

#### The Proposed Approach

[13] the time between requesting the activation of the weapons and their actual firing time is computed. The maximum time in that example is infinity. The weapons may never fire because the firing sequence can be aborted. It may be the case, however, that the designers want to compute the maximum response time of the weapon subsystem *provided that no abort occurs*.

We propose a method for specifying and verifying properties such as these. The user can restrict the set of paths that will be considered by specifying a property that must be satisfied in all paths traversed. This property is expressed using *linear-time temporal logic* (LTL). Special model checking techniques [22] are then used to ensure that only paths that satisfy the formula are considered by the algorithms.

#### 1.3.4 Analysis of the results

The power of our method comes mostly from the different types of analysis that can be performed with the results produced by the algorithms. This section explores different ways in which these results can be used to extract the correctness of a design, its performance and insight into its behavior.

The basic algorithms compute minimum and maximum time delays between two state sets start and final. We can use them to determine response time to events by applying the algorithms to the predicates start = event and final = response. Such numbers also give information about the correctness of a design. If the maximum is less than infinity then event always implies response in the future:

$$MAX(event, response) < \infty \text{ iff } AG(event \rightarrow AF response)$$

Notice that a similar statement can associate a minimum value to the existence of a path. This shows that our algorithms can express the same properties as these specific CTL formulas. It can be argued that CTL can express more complex properties than those described above. However, properties such as the one described are certainly some of the most frequently checked, and this correspondence is extremely useful in practice.

The minimum and maximum algorithms can also be used to perform the schedulability analysis of a real-time task set. We can compute bounds on the execution time of all processes, and check if they are within the corresponding deadlines. That also gives the user information about the load on the system: maximum execution times close to the deadline indicate high load. We have applied this technique to various real-time systems, such as the aircraft controller described in [13]. Non real-time systems can also benefit from this analysis. We can compute response time for any event in the system, and check the performance against the specifications. These results can provide information that may have significant impact in market acceptance when compared to the expected behavior or competitor products. For example, a correct product may have a performance bottleneck that may compromise the performance of the whole system. If the bottleneck cannot be identified and corrected, the product may lose its market share due to poor performance. We have applied this method to the verification of the PCI local bus [15].

The algorithms that count the number of times a condition occurs in a path can be extremely useful in this analysis as well. Given a *condition* to be counted and two events *start* and *final*, these algorithms compute the minimum and maximum number of times *condition* holds on any path from *start* to *final*. They make it possible to determine even more detailed information about the system. For example, in real-time systems it is possible to compute information such as priority inversion time by making *start* and *final* 'request for execution' and 'end of execution' at a certain priority level respectively, and the *condition* to be counted to be 'executing at lower priority'. In non real-time systems for example, it is possible to compute the overhead associated with processing of data by making *start* a 'request for transaction', *final* the 'end of transaction', and *condition* to be 'data being processed'.

Another way in which designers can benefit from this method is by fine-tuning the system for optimal performance. After computing the response times for important events, the designer can change parameters in the model and check how the response times are affected. In this way it is possible to optimize performance by determining the effect of the parameters on the global behavior. Even finer tuning is possible by using selective quanti-

#### **Summary and Main Contributions**

tative analysis. For example, a very useful practice is to optimize the performance for the most common case, while maintaining the correctness of uncommon cases. Selective quantitative analysis can be used to restrict the model to the common cases. Optimization can then be performed on this model. Finally, the complete system can be checked for correctness by removing the selection condition.

Several real-time systems have been analyzed using the method proposed. One example is the aircraft controller described in [60]. This control system is characterized by a set of real-time tasks, each controlling one subsystem of the aircraft. We have modeled this control system and analyzed it using the algorithms described. We have been able to determine the schedulability of the task set and to determine the response times for specific events of the system such as how long it takes from the moment the pilot presses the firing button until the weapons are actually fired.

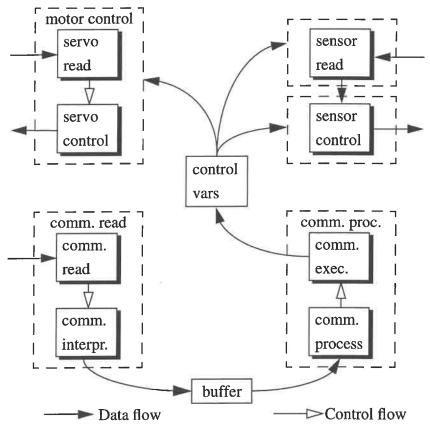

Another example that we have analyzed is a robotics system used in nuclear plants to measure the shape of pipes by moving around them with a distance sensor [38]. We have been able not only to determine the schedulability of this task set but also to discover inefficiencies in the design. The results produced by the algorithms also suggested optimizations. The modified design has also been analyzed by the same algorithms. It has a lighter load and data is consumed faster than in the original design.

Other systems that have been analyzed include a medical monitoring system, the PCI Local Bus and a distributed real-time system. In all these cases we have been able to analyze the correctness and performance of the system, and in most cases optimize it using the method proposed.

#### 1.4 Summary and Main Contributions

In this work we propose a new method for the formal verification of real-time systems. The method allows a detailed and accurate analysis of the behavior of the system and is efficient enough to be used in the verification of real systems. We have used it to analyze

several complex systems. The analysis performed using this method not only demonstrates the correctness of the design, but in many cases it can uncover ambiguities in the behavior that might be difficult to find otherwise.

Verus extends previous methods in several directions. It allows the natural expression of many types of real-time systems that occur in practice via a language especially designed to simplify the description of timing characteristics such as periods and deadlines. Previous languages cannot in general be used as efficiently because they either do not have the primitives needed to express timing characteristics (e.g. SMV [62]), lack nondeterministic features (e.g. Esterel [5]) or can be more restrictive than the language proposed (e.g. Modechart [47]).

Moreover, many other verification methods such as model checking cannot directly verify several types of properties that can be checked in a straightforward way in Verus. Time bounds and other quantitative information such as the number of occurrences of events in the system are examples of properties that cannot be easily obtained using standard model checking. Analyzing the performance and determining the timing characteristics of a model is very simple in Verus, but it is not possible (except to a very limited extent) with traditional model checking or reachability based systems. For example, model checkers can only check time bounded properties by expressing them using nested next state operators. The resulting formula, however, is often very large and cumbersome, and impractical to work with. Quantitative information can be obtained by adding counters that flag the occurrence of the event of interest, and checking that the value of the counter is within a certain range. However, adding counters is an expensive operation, significantly increasing the complexity of the verification.

Even though it allows the expression of a richer set of timing properties than standard model checking, the rate monotonic theory is also more limited than the Verus approach in many aspects. The description of a system verified by RMS has to fit a very rigid structure. For example, tasks have to be periodic or to be modelled using an sporadic server (see [70] and Section 2.2.2); synchronization has to follow protocols such as priority inherit-

#### **Summary and Main Contributions**

ance (see [66] and Section 2.2.2) which can be very restrictive. Any deviation from this structure has to be reformulated or the system cannot be verified. In some cases it is possible to change the system description to allow the verification, for instance, by describing an aperiodic processes using an aperiodic server, but in many cases this is not possible.

Distributed systems represent an important class of systems in which modifying the system description may be insufficient to correctly analyze its timing behavior. To date, RMS has required the imposition of intermediate deadlines to analyze distributed systems [69]. However, intermediate deadlines significantly change system behavior. In Verus there are no restrictions on the structure of the system; any Verus program can be verified. Moreover, RMS allows the expression of a very limited type of property; basically it computes the maximum execution times of tasks in the system. Even though a large number of interesting properties can be expressed using this paradigm, this may be very difficult in some cases. On the other hand, in Verus it is possible to determine the temporal relation between any two events in the system. For example, counting the number of occurrences of arbitrary events in specific intervals is a property that is simple to express in Verus, but difficult to express in RMS.

In most verification techniques it is possible to extend its expressive power by changing the system to fit the limitations of the algorithms and verify a modified model. For example, a counter can be introduced to represent the number of occurrences of an event, and a CTL formula can be written stating that the counter never overflows. However, modifying the system may introduce additional errors, or hide existing ones. Some properties similar to those verified by Verus can be checked using model checking or RMS by introducing modifications to the system (such as the aperiodic servers or intermediate deadlines described). But even in these cases, one important advantage of Verus is that it allows the verification of these properties without changing the model, ultimately performing a more accurate analysis.

One example of a system that has been verified using Verus that might have been difficult to verify using other techniques is the distributed real-time system described in

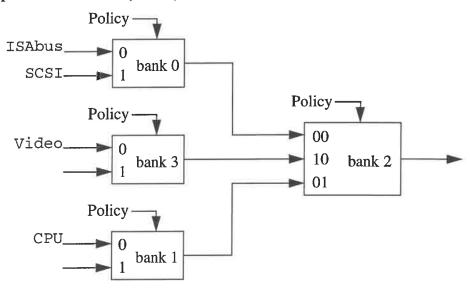

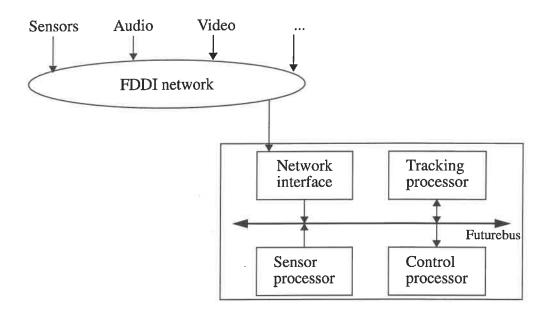

section 6.6. It is a large complex system which has three main components: a network to which audio and video sources are connected, a multi-processor bus transporting this data and the destination processor for it. In this example, we analyze the time it takes for data to traverse the various components of the system. The type of quantitative analysis performed cannot be done directly using model checking or reachability based techniques. The system cannot be easily described in RMS because it is a distributed system (limitations on the ability of RMS to handle distributed systems are discussed in [69]). Finally, because it is a large system, it is not likely that a continuous time method would be able to handle its complexity.

# Chapter 2 Related Approaches

This chapter will present the two methods for analyzing real-time systems that are most closely related with the proposed approach: symbolic model checking and rate monotonic scheduling. The algorithms used by Verus have been derived from symbolic model checking algorithms. The analysis performed is, however, derived from the rate monotonic theory. Knowledge about these methods is not a required prerequisite, but it can simplify understanding the Verus approach.

#### 2.1 Temporal Logic Symbolic Model Checking

Extensive simulation is currently the most widely used verification technique for finite-state systems. However, simulation cannot usually cover all possible behaviors of a computing system. Traditional simulation is too expensive, and non-exhaustive simulation can miss important events, especially if the number of states in the system being verified is large. Other approaches for verification include theorem provers, term rewriting systems, and proof checkers. These techniques, however, are usually very time consuming, and require user intervention to a large degree. Such characteristics limit the size of the systems they can verify in practice.

#### **Related Approaches**

Temporal logic model checking [19,20] is an alternative approach that has achieved significant results recently. Efficient algorithms are able to verify properties of extremely large systems. In this technique, specifications are written as formulas in a propositional temporal logic and computer systems are represented by state-transition graphs. Verification is accomplished by an efficient search procedure that views the transition system as a model for the logic, and determines if the specifications are satisfied by that model.

There are several advantages to this approach. An important one is that the procedure is completely automatic. The model checker accepts a model description together with specifications written as temporal logic formulas and determines if the formulas are true or not for that model. Another advantage is that, for most formulas of interest (e.g. safety formulas) if the formula is not true, the model checker will provide a counterexample. The counterexample is an execution trace that shows why the formula is not true. This is an extremely useful feature because it can help locate the source of the error and speed up the debugging process. Another benefit is the ability to verify partially specified systems. Useful information about the correctness of the system can be gathered before all the details have been determined. This allows the verification of a system to proceed concurrently with its design. Consequently verification can provide valuable hints that will help designers eliminate errors earlier and define better systems.

Properties to be verified are described as formulas in a propositional temporal logic. The system for which the properties should hold is given as a state transition graph. It defines a model for the temporal logic since the semantics of the logic are given in terms of state transition graphs. The model checker traverses this graph and verifies if the model satisfies the formula. Checking that a single model satisfies a formula is much simpler than proving that a formula is valid for all possible models. Because of this fact model checkers can be more efficiently implemented than theorem provers. The first algorithms [19] use adjacency lists to represent the transition graph and have polynomial complexity in the size of the model and in the length of the formula. These systems are able to handle graphs with up to  $10^5$  states.

#### **Temporal Logic Symbolic Model Checking**

Recently, more efficient algorithms have been developed using *symbolic* techniques. In the new approach the transition relation is represented implicitly by boolean formulas, and implemented by *binary decision diagrams* [6]. This usually results in a much smaller representation for the transition relation, allowing the size of the models being verified to increase to more than  $10^{30}$  states.

#### 2.1.1 Computation Tree Logic

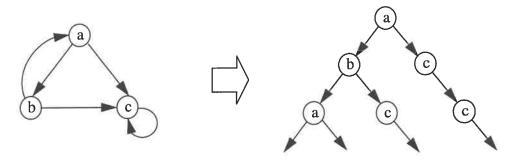

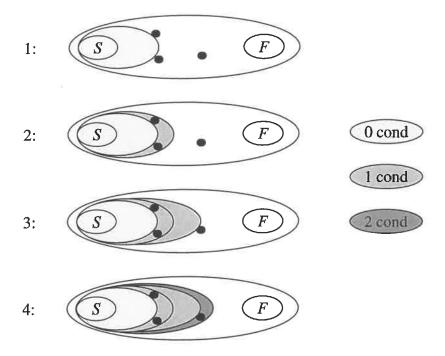

Computation tree logic, CTL, is the logic used by SMV to express properties that will be verified [20]. Computation trees are derived from state transition graphs. The graph structure is unwound into an infinite tree rooted at the initial state, as seen in figure 2. The tree is infinite because no final states are considered, only infinite paths. Paths in this tree represent all possible computations of the program being modelled. Formulas in CTL refer to the computation tree derived from the model. CTL is classified as a branching time logic because it has operators that describe the branching structure of this tree.

Figure 1. A state transition graph and the corresponding computation tree

Formulas in CTL are built from atomic propositions, where each proposition corresponds to a variable in the model, boolean connectives  $\neg$  and  $\land$ , and temporal operators. Each operator consists of two parts: a path quantifier followed by a temporal operator. Path quantifiers indicate that the property should be true of all paths from a given state (A), or some path from a given state (E). The temporal quantifier describes how events should be ordered with respect to time for a path specified by the path quantifier. They have the following informal meanings:

#### **Related Approaches**

- **F** f (f holds sometime in the future) is true of a path if there exists a state in the path that satisfies f.

- Gf(f) holds globally) is true for a path if f is satisfied by all states in the path.

- $\mathbf{X} f(f)$  holds in the next state) means that f is true in the next state of the path.

- $f \mathbf{U} g$  (f holds until g holds) is satisfied by a path if g is true in some state in the path, and in all preceding states, f holds.

Formally, the syntax for CTL can be defined by:

- Every atomic proposition *p* is a CTL formula.

- If f and g are CTL formulas, then so are  $\neg f, f \lor g$ , **EX** f, **EG** f and **E**[f **U** g].

The semantics of CTL formulas are defined with respect to a labeled state-transition graph, which is a 5-tuple  $M = (P, S, L, N, S_0)$ , where P is a set of atomic propositions, S is a finite set of states, L is a function labeling each state with a set of atomic propositions,  $N \subseteq S \times S$  is a transition relation, and  $S_0$  is the set of initial states. A path is an infinite sequence of states  $s_0 s_1 s_2 \dots$ , such that  $N(s_i, s_{i+1})$  is true for every i.

If f is true in a state s of structure M, we write M,  $s \models f$ . We write  $M \models f$  if M,  $s \models f$  for all states s in  $S_0$ . The satisfaction relation is defined inductively as follows (Given the model M, we abbreviate M,  $s \models f$  by  $s \models f$ ):

- 1. If f is the atomic proposition  $v \in P$ , then  $s \models f$  if and only if  $v \in L(s)$ .

- 2.  $s \models \neg f$  iff it is not the case that  $s \models f$ .

- 3.  $s \models f \lor g \text{ iff } s \models f \text{ or } s \models g$ .

- 4.  $s \models \mathbf{EX} f$  iff there exists a path  $\pi = s_0 s_1 s_2 \dots$  starting at  $s = s_0$ , such that  $s_1 \models f$ .

- 5.  $s \models \mathbf{EG} f$  iff there exists a path  $\pi$  starting at s such that for every state s' on  $\pi$ ,  $s' \models f$ .

- 6.  $s \models \mathbf{E}[f \mathbf{U} g]$  iff there exists a path  $\pi = s_0 s_1 s_2...$  starting at  $s = s_0$  and some  $i \ge 0$  such that  $s_i \models g$  and for all j < i,  $s_j \models f$ .

### **Temporal Logic Symbolic Model Checking**

The following abbreviations are used in CTL formulas:

$$f \wedge g \equiv \neg(\neg f \vee \neg g)$$

$$\mathbf{AX} f \equiv \neg \mathbf{EX} \neg f$$

$$\mathbf{EF} f \equiv \mathbf{E}[true \ \mathbf{U} f]$$

$$\mathbf{AF} f \equiv \neg \mathbf{EG} \neg f$$

$$\mathbf{AG} f \equiv \neg \mathbf{EF} \neg f$$

$$\mathbf{A}[f \ \mathbf{U} \ g] \equiv \neg \mathbf{E}[\neg g \ \mathbf{U} \neg f \wedge \neg g] \wedge \neg \mathbf{EG} \neg g$$

Some examples of CTL formulas are given below to illustrate the expressiveness of the logic.

- AG (req → AF ack): It is always the case that if the signal req is high, then eventually ack will also be high.

- **EF** (started  $\land \neg$  ready): It is possible to get to a state where started holds but ready does not hold.

- AG EF restart: From any state it is possible to get to a state where restart holds.

- AG (send → A[send U recv]): It is always the case that if send occurs, then eventually

recv is true, and until that time, send must remain true.

# 2.1.2 Symbolic Model Checking

Early model checking algorithms represent the transition graph by adjacency lists [19]. All existing states are explicitly enumerated. However, the number of states in the model can be exponential in the number of concurrent components in the system. This frequently causes state explosion problems. The size of systems that can be verified is severely limited. Symbolic model checking represents states and transitions using boolean formulas. This usually generates smaller representations, because it can automatically eliminate

#### **Related Approaches**

redundancy in the graph. Implementing these boolean formulas as BDDs leads to very efficient algorithms for model checking that are able to verify much larger systems than previous ones. This section explains the symbolic model checking approach.

# **Binary Decision Diagrams**

Binary decision diagrams (BDD) are an efficient way to represent boolean formulas. BDDs often provide a much more concise representation than traditional representations like conjunctive normal form or disjunctive normal form. They can also be manipulated very efficiently [6]. Another advantage offered by BDDs is that they provide a canonical representation for boolean formulas. This means that two boolean formulas are logically equivalent if and only if they have isomorphic representations. It greatly simplifies the execution of operations that are performed frequently like checking equivalence of two formulas or deciding if a given formula is satisfiable or not. Because of all these characteristics, BDDs have found application in the implementation of many computer aided design and verification tools.

BDDs can be better understood by first considering how boolean formulas can be represented by binary decision trees. The nodes in the decision tree correspond to the variables of the formula. Descendants of a node are labelled with *true* or *false*. The value of the formula for a given assignment of values to the variables can be found by traversing the tree from root to leaf. At each node the descendant labelled with the value of that variable is chosen. Each leaf corresponds to a particular assignment to the variables, and contains the truth value of the formula for that assignment.

This representation is not particularly compact, because it may store the same information repeatedly in different places. BDDs are derived from binary decision trees, but their structure is a directed acyclic graph instead of a tree. Redundant information in the structure is avoided by sharing common subtrees. As in decision trees, nodes are visited in sequence, from root to leaf. Note that BDDs impose a total ordering in which the variables occur in this sequence. This order is preserved for all BDDs in use at the same time. For

#### **Temporal Logic Symbolic Model Checking**

example, the BDD shown in figure 1 represents the formula  $f = (a \land b) \lor (c \land d)$  using the ordering a < b < c < d for the variables.

Given an assignment for the variables in f we can decide if this assignment satisfies the formula by traversing the BDD from root to leaf. At each node we follow the path that corresponds to the value assigned to the variable in the node. The leaf indicates if the formula is satisfied or not for that particular assignment. Notice that redundancy is eliminated in two ways. Common subtrees are not replicated, as can be seen in the figure below on the paths when a is false and when b is false. Also, when all the leaves of a subtree have the same value, the subtree is eliminated, and a leaf of that value is inserted at its place. In the figure, when a and b are both true a subtree containing the variables c and d is eliminated because all of its leaves would have the value 1.

Figure 2. BDD for formula  $(a \land b) \lor (c \land d)$

For any boolean formula there exists a unique BDD for a given variable ordering [6]. The BDD size is critically dependent on the variable ordering. It is exponential in the number of variables in the worst case. Given a good variable ordering, however, the size is linear in many practical cases. Using a good variable ordering is very important, but finding the optimal order is in itself an exponential problem. Nevertheless, there are many heuristics that work quite well in practice.

#### **Related Approaches**

Efficient algorithms exist to handle boolean formulas represented by BDDs. Given BDD representations for f and g, algorithms for computing  $\neg f$  and  $f \lor g$  are given in [6]. Algorithms for quantification over boolean variables and substitution of variable names are also required by the model checker. It is simple to compute the restriction of a formula f with a variable v set to 0 or 1. We will denote the restriction of f with v set to 0 by  $f|_{v=0}$ , and the restriction of f with v set to 1 by  $f|_{v=1}$ . The formula  $\exists v \ [f]$  is defined as  $f|_{v=0} \lor f|_{v=1}$ , and  $\forall v[f]$  is defined as  $\neg \exists v[\neg f]$ . Variable substitution can be accomplished using the quantification algorithm.  $f\langle v \leftarrow w \rangle$  denotes the substitution of variable v in formula v. It is computed as v and v are v and v are v and v are v are v and v are v are v and v are v and v are v are v and v are v are v and v are v and v are v are v and v are v are v and v are v and v are v are v and v are v are v and v are v and v are v are v and v are v and v are v and v are v are v and v are v are v and v are v and v are v are v are v and v are v are v and v are v are v and v are v and v are v are v and v are v are v are v are v are v and v are v and v are v are v and v are v are v and v are v and v are v are v are v and v are v are v and v are v and v are v are v and v are v are v are v and v are v are v are v are v and v are v are v are v are v and v are v are

# Representing the Model

The key to the efficiency of the algorithm is to use BDDs to represent the labeled state-transition graph and to verify if the formula is true or not. The representation used in Verus is the same as the one used by symbolic model checking. Details can be found in Section 4.1 and [8,62].

By definition, time passes by one time unit at each transition. This does not restrict the models that can be verified by the method, because non-unit transitions can be modeled as a sequence of unit transitions. Nondeterministic transition times can also be implemented in the same way, by using stuttering [11].

Frequently a model is described by a set of processes that execute concurrently. Given a set of processes and a state-transition graph for each, a parallel composition algorithm is used to construct a global transition system in which all processes execute concurrently. Two composition models are normally implemented by model checking: synchronous and asynchronous composition. In synchronous composition, all processes transition at the same time, while in asynchronous composition only one transitions. In asynchronous composition the choice of which process executes is non-deterministic and fairness is used to avoid starvation [62]. Both models are implemented using BDDs.

#### Temporal Logic Symbolic Model Checking

The composition algorithm is extremely expensive; it often generates an exponential number of states in the composed graph. However, the efficiency of symbolic model checking and the fact that our method uses discrete time allows the use of composition in several practical systems without state explosion problems.

## Fixpoint characterization

Consider a labeled transition graph M with set of states S. We can denote a lattice of predicates over S by Pred, where each predicate is identified with the set of states in S that make it true, and use set inclusion as ordering. A functional F that maps Pred(S) to Pred(S) is called a Pred(S) to Pred(S) is a set of states, and F is a function from sets of states to set of states.

As described in [25], if a predicate transformer F is monotonic, it has a least fixpoint **lfp**  $Z[F(Z)] = \bigcup_i F^i(false)$  and a greatest fixpoint **gfp**  $Z[F(Z)] = \bigcap_i F^i(true)$ . We can compute both fixpoints by iteration. Starting with  $Z^0 = false$  (for **lfp**) or  $Z^0 = true$  (for **gfp**), we have  $Z^{i+1} = Z^i \cup F(Z^i)$  for **lfp** and  $Z^{i+1} = Z^i \cap F(Z^i)$  for **gfp**. The fixpoint is found when  $Z^i = Z^{i+1}$ . If the number of elements in Pred(S) is finite, termination is guaranteed, because there can be no infinite sequence of  $Z^i$ s such that  $Z^i \neq Z^{i+1}$ .

We can identify each CTL formula f with the predicate  $\{s \mid M, s \models f\}$  in Pred(S) (this is the set of states that satisfy f). Then, we can characterize each basic CTL temporal operator as a fixpoint of an appropriate predicate transformer. The set of states that satisfy the until operator  $\mathbf{E}[f \mathbf{U} g]$  is given by the least fixpoint of  $Z = g \lor (f \land \mathbf{E} \mathbf{X} Z)$ . Informally  $\mathbf{E}[f \mathbf{U} g]$  is true at state s, if either g is true in s, or f is true in s and there exists a successor state where  $\mathbf{E}[f \mathbf{U} g]$  is true. The set of states that satisfy the  $\mathbf{E} \mathbf{G} f$  operator is given by the greatest fixpoint  $\mathbf{E} \mathbf{G} f$  of  $Z = f \land \mathbf{E} \mathbf{X} Z$ . Informally, this means that  $\mathbf{E} \mathbf{G} f$  holds in a state s if f holds in s and  $\mathbf{E} \mathbf{G} f$  holds in a successor state of s. Proofs that the characterizations above correspond to the expected semantics are given in [25].

#### **Related Approaches**

# The Model Checking Algorithm

Given a CTL formula f and a model M represented as described above, the model checking problem consists of finding the set of states in M that satisfy f. The model checking algorithm is defined inductively over the structure of CTL formulas. It accepts the formula as an argument (and M as an implicit argument), recurses over the structure of f and returns a BDD that has one boolean variable for every atomic proposition in V. The resulting BDD is true of a state if and only if f is true in that state. The algorithm is:

- If f is an atomic proposition p, return the BDD that is true if and only if p is true. This is simply the BDD for p.

- If f is  $\neg g$  or  $g \land h$ , use the standard BDD algorithms for computing boolean connectives.

- If f is EX g, then we must verify if g is true in a successor state of the current state. EX f is true in a state t if and only if there exists a state s such that g is true in state s, and there exists a transition from t to s:

$$t \models \mathbf{EX} \ g \ \text{iff} \ \exists \ s \ [\ g\langle s \rangle \land N(t, s) \ ]$$

Where  $g\langle s \rangle$  means the value of formula g in state s. This value can be computed using the existential quantification algorithms described previously.  $g\langle s \rangle$  is true if and only if  $s \models g$ . However, this operation occurs frequently, and it is important to compute it in an efficient manner; efficient algorithms for this purpose are discussed in [8].

• If f is  $E[g \cup h]$ , the BDD that represents the states where  $E[g \cup h]$  is true can be computed by iterating:

$$\mathbf{E}[g \mathbf{U} h] = h \vee (g \wedge \mathbf{EX} \mathbf{E}[g \mathbf{U} h])$$

• If f is EG g, the algorithm is defined in a similar way. It searches for the greatest fix-point EG g instead, and uses the following formula:

$$\mathbf{EG} g = g \wedge \mathbf{EX} \mathbf{EG} g$$

• All other CTL operators are written in terms of the ones presented.

#### **Temporal Logic Symbolic Model Checking**

# 2.1.3 Verus and Symbolic Model Checking

Verus shares many important characteristics with symbolic model checking, such as the use of symbolic algorithms implemented by BDDs. The model is represented in a similar way, and the quantitative algorithms have similar fixpoint characterizations. The main differences are in the way the system is specified, and in the types of results produced by the algorithms.

Most model checkers use specification languages that have not been designed to simplify the specification of real-time systems. In some systems, such as SMV, the specification language simplifies the description of synchronous circuits. Writing a real-time program in such languages is difficult and error-prone. Too much time is spent trying to accommodate the system into the language constructs. Other verifiers use languages better suited for describing timing constraints such as Esterel, but they usually have an unfamiliar syntax. Too much time may be spent learning the language and in trying to understand how to represent the desired features of the system. The Verus language, on the other hand, uses a syntax that is familiar to most real-time system designers. It also has constructs that make it easy to express timing characteristics. Because of this, it is better suited to specify the real-time systems that will be verified than most languages used by other model checkers.

The most important differences, however, are the results produced and their analysis. Model checking concentrates on determining if events will or will not happen at some point in the future. This information is essential in asserting the correctness of a model, but it is not sufficient to assure predictability of a real-time system. Verus overcomes this limitation by concentrating on the determination of time bounds between events. This information provides important insight into the behavior of the system. The quantitative information produced by Verus cannot be easily produced by a standard model checker or reachability system, yet it is vital in determining the correctness of a real-time system.

# 2.2 Rate Monotonic Scheduling Theory

Computers have been used in critical situations for a long time. Their ability to react faster than humans and to perform under dangerous conditions was foreseen early on. However, it was also realized early on that the behavior of a computer system is not always simple to predict. In some cases the interaction between the various components in the system can cause a response to be delayed unexpectedly, making the system unpredictable. However, unpredictable behavior is not acceptable in critical applications. Because of this a very conservative approach was usually taken, by designing the system to support a significantly larger load than expected. The rationale was that if enough computing power is given to the application, the response time would be acceptable even for cases in which unexpected delays occur. The erroneous but still common idea that being real-time is the same as being fast may have originated at this time.

This approach is incorrect, however. In some cases it may work, because sometimes unexpected delays are bounded. However, there may be situations in which unbounded delays can occur caused by problems such as priority inversion [66]. In this case a response may never be produced. But the approach of designing the system to support larger loads is not a good one, even in the cases where it leads to correct results. It is not scalable, and it is very expensive in general. In order to be able to design predictable systems it is necessary to use methods that determine a priori if the system will meet its timing requirements. These methods must guarantee that the system is predictable, even if not necessarily fast.

# 2.2.1 The Liu and Layland Theory

Liu and Layland presented one of the first techniques that addressed analytically the problem of determining the predictability of a real-time system [59]. The original rate monotonic scheduling theory is a subset of their work. In this approach a real-time system is given by a set of tasks that execute periodically on a single processor. They have shown how to schedule task execution in order to guarantee that the timing requirements will be satisfied, and to optimize resource utilization. Their method assumes that:

#### **Rate Monotonic Scheduling Theory**

- All tasks are periodic, that is, they execute once every t time units, where t is a parameter of the task. The period of a task is a time interval of length t such that the union of all periods partition the time line starting at time 0. Tasks execute once every period, and are ready to execute at the start of each period. They have known, deterministic execution times.

- The deadlines for each task are at the end of the period, that is, every execution *must* finish by the end of the period. If the deadline for *any* period of *any* task is not met, an error condition occurs and the system becomes unschedulable.

- Tasks do not suspend themselves during execution.

- Tasks are independent and can be preempted instantaneously. Preemption overhead is assumed to be zero, that is, the context switch time is assumed to be negligible.

- There is no synchronization between tasks.

Under these assumptions Liu and Layland studied both static and dynamic scheduling algorithms. Static scheduling assigns a fixed priority for each task, this priority does not change. Under dynamic scheduling priorities may change in time.

# **Dynamic Scheduling**

An example of a dynamic priority algorithm is the earliest deadline first algorithm. Under the earliest deadline first algorithm, the process that has the closest deadline is given the highest priority. This algorithm guarantees schedulability of task sets that utilize the processor up to its full capacity. However, some practical problems associated with dynamic scheduling have not been solved such as its behavior under transient overload, scheduling of aperiodic tasks and priority granularity in communication scheduling [49]. For this reason, static scheduling algorithms are more popular than dynamic scheduling algorithms.

#### **Related Approaches**

# **Static Scheduling**

The rate monotonic scheduling algorithm is an example of a static priority algorithm. It assigns higher priorities to tasks with shorter periods. It is an optimal static priority algorithm in the sense that if a task set can be scheduled using some static priority algorithm, it can be scheduled using the rate monotonic scheduling algorithm.

Liu and Layland derived a sufficient condition for a task set to be schedulable by the rate monotonic algorithm under the assumptions given above. A set of n periodic tasks  $\tau_1$ ,  $\tau_2,...,\tau_n$  is characterized by a period  $t_i$  and an execution time  $c_i$  for each task. The formula  $u_i = c_i/t_i$  gives the percentage of the time task  $\tau_i$  is utilizing the processor. The formula  $U = u_0 + u_1 + ... + u_n$  gives the total processor utilization for the task set. If a task set with n tasks has total processor utilization of at most  $n(2^{1/n}-1)$  then its schedulability is guaranteed under rate monotonic scheduling. For large values of n, this bound converges to  $\ln 2 \approx 0.693$ . This is a sufficient, but not necessary condition; some task sets with utilization higher than this bound can be schedulable.

Another important result is shown in [59]. It states that the longest response time for any invocation of task  $\tau_i$  occurs when all tasks start executing simultaneously. The time when all processes request execution is called critical instant. This result can be used to check schedulability in some cases where the total utilization is higher than the bounds described above. It is possible to guarantee that the task set is schedulable by assuming that all tasks start execution at the same time, and checking if the deadline of the first instantiation of each task is met.

# 2.2.2 Extensions of the Liu and Layland Theory