### **Pandora:**

### **Facilitating IP Development for Hardware Specialization**

### Michael K. Papamichael

CMU-CS-15-121 August 2015

Computer Science Department School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Thesis Committee: James C. Hoe, Chair Ken Mai Todd Mowry Onur Mutlu Mark Horowitz, Stanford University

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Copyright © 2015 Michael K. Papamichael All Rights Reserved

This research was sponsored by equipment and tool donations from Xilinx and Bluespec, an Intel PhD Fellowship, and the National Science Foundation under grants CCF-0811702 and CCF-1012851.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

**Keywords:** Computer Architecture, Network-on-Chip, NoC, FPGA, ASIC, Reconfigurable Hardware, Hardware Specialization, Hardware Acceleration, IP Block, IP Development, IP Optimization, Design Space Exploration, Hardware Instrumentation, Runtime Monitoring

to Azra

#### Abstract

In an effort to continue increasing performance in the power-constrained setting of the post-Dennard era, there is growing interest in hardware specialization. However, a major obstacle to the more widespread use of hardware acceleration is the level of difficulty in hardware design today. Despite the increased availability of rich IP libraries and even IP generators that span a wide range of application domains, developing hardware today is limited to experts, takes more time and is more expensive than ever.

This thesis presents the Pandora IP development paradigm that facilitates hardware development and specialization by extending the concept of generator-based IPs. Pandora encapsulates the IP author's expertise and domain knowledge to offer supporting infrastructure and assist the users' interactions with the IP. In contrast to existing IPs and IP generators that only capture the structural and microarchitectural view of a design, Pandora argues for augmenting IPs with: (1) detailed IP design space characterization to help the user understand the effects of parameter choices with respect to hardware implementation and IP-specific metrics, (2) application-level goal-oriented parameterization that is meaningful to the IP user and automatically sets low-level structural parameters to achieve the desired design optimizations, and (3) purpose-built domain-aware simulation-time and run-time monitoring mechanisms to assist functional and performance debugging.

To highlight the benefits of hardware specialization and demonstrate the key principles of the Pandora IP development paradigm, this thesis presents our research efforts on: (1) CONNECT, a flexible Network-on-Chip (NoC) IP generator that embodies the Pandora principles and is actively used by hundreds of researchers around the world, (2) DELPHI, a framework for fast easy IP characterization that facilitates mapping the design space of arbitrary RTL-based IPs, (3) Nautilus, an IP optimization engine that demonstrates how incorporating IP author knowledge in genetic algorithms can enable very fast—orders of magnitude faster than conventional methods—highlevel goal-oriented IP optimization, and (4) IRIS, an instrumentation and introspection framework that combines hardware monitors with software-based post-processing and visualization engines to accelerate debugging of complex IPs and enable higher system-level visibility.

#### Acknowledgments

First and foremost, I would like to thank my advisor James Hoe for supporting, guiding, and encouraging me throughout my PhD, always being available to help and offer advice, giving me freedom to explore and grow as a researcher, and maintaining a happy, friendly, comfortable environment. James taught me how to think, ask the right questions, identify truly interesting research problems, and perhaps more importantly, how to become a better, happier, more complete human being. Thank you.

I thank my committee members, Professors Ken Mai, Onur Mutlu, and Todd Mowry for their support, feedback, and for always being available to meet with me and discuss about research. I thank my external committee member, Professor Mark Horowitz for his advice and feedback that helped shape and improve this thesis. I owe special thanks to Professor Babak Falsafi for offering his support and advice throughout the years even all the way from Switzerland. I thank Professor Derek Chiou and my mentors at Intel Labs, Hong Wang and Graham Schelle, for their support. I thank Professor Manolis Katevenis, who introduced me to computer architecture and encouraged me to pursue a PhD. I also thank the Computer Science Department staff, especially Deb Cavlovich, for working tirelessly to ensure student happiness.

I thank all of my friends and collaborators at Carnegie Mellon. I am grateful to my friend, office-mate and collaborator Eric Chung for mentoring me during my first years as a graduate student and for the lengthy research discussions (and pingpong sessions) that often ran into the early morning. I thank my CMU collaborators Yoongu Kim, Peter Milder, Gabriel Weisz, Eriko Nurvitadhi, Cagla Cakir, Professor Mor Harchol-Balter, as well as my external collaborators, Chen Sun, Chia-Hsin Owen Chen, and Professors Li-Shiuan Peh and Vladimir Stojanovic. I thank my friends and fellow CMU graduate students Nikos Hardavellas, Evangelos Vlachos, Kiki Levanti, Theodoros Strigkos, Ippokratis Pandis, Brian Gold, Mike Ferdman, Jared Smolens, Peter Klemperer, Berkin Akin, Yu Wang, Marie Nguyen, Malcolm Taylor, Felix Hutchinson, Jangwoo Kim, Chris Fallin, Chris Craik, Vivek Sheshadri, Lavanya Subramanian, Rachata Ausavarungnirun, Gennady Pekhimenko, Justin Meza, Samira Khan, Stephen Somogyi, Michelle Goodstein, Burak Erbagci, Kaushik Vaidyanathan, Mark McCartney for their support, advice, and for making grad school fun. Finally, I want to thank my friends in Greece, as well as all the new friends I made in Pittsburgh for all the fun times and for keeping me company during work and the occasional all-nighter.

I thank my family, my father Konstantinos, my mother Irene, and my wife Marina for their unconditional love, support and constant encouragement. I love you very much.

This work was supported in part by hardware and tool donations from Xilinx and Bluespec, NSF grants CCF-0811702 and CCF-1012851, and an Intel PhD Fellowship.

## Contents

| 1 | Intr | oduction                                                         | 1  |

|---|------|------------------------------------------------------------------|----|

|   | 1.1  | The Rise of Hardware Complexity                                  | 2  |

|   | 1.2  | Pandora: Facilitating IP Development for Hardware Specialization | 4  |

|   | 1.3  | Thesis Contributions                                             | 5  |

|   | 1.4  | Thesis Organization                                              | 6  |

| 2 | The  | CONNECT Network-on-Chip IP Generator                             | 9  |

| 4 | The  | -                                                                | ,  |

|   | 2.1  | Introduction                                                     | 9  |

|   | 2.2  | Background: NoC Terminology                                      | 12 |

|   | 2.3  | NoC Design Parameterization                                      | 14 |

|   |      | 2.3.1 Network Topologies                                         | 16 |

|   |      | 2.3.2 Router Architectures                                       | 17 |

|   | 2.4  | Generated NoCs                                                   | 19 |

|   |      | 2.4.1 Specializating for the FPGA Substrate                      | 21 |

|   |      | 2.4.2 Specializing for the Application                           | 24 |

|   | 2.5  | CONNECT Principles                                               | 25 |

|   | 2.6  | Pandora Motivation                                               | 27 |

|   | 2.7 | Related Work                                              | 28 |

|---|-----|-----------------------------------------------------------|----|

| 3 | The | Pandora IP Development Paradigm                           | 31 |

|   | 3.1 | Background: The Rise of Design Complexity                 | 32 |

|   | 3.2 | Pandora Principles                                        | 35 |

|   |     | 3.2.1 Detailed IP Characterization                        | 35 |

|   |     | 3.2.2 Automated IP Optimization                           | 37 |

|   |     | 3.2.3 Sophisticated IP Instrumentation                    | 39 |

|   |     | 3.2.4 The IP "Uncore"                                     | 42 |

|   | 3.3 | Existing Efforts to Tackle Design Complexity              | 44 |

|   | 3.4 | Demonstrating Pandora                                     | 47 |

| 4 | DEI | PHI - Fast IP Characterization                            | 51 |

|   | 4.1 | The Need for Fast Accurate Architecture Design Evaluation | 52 |

|   | 4.2 | Background                                                | 54 |

|   |     | 4.2.1 RTL Synthesis                                       | 54 |

|   |     | 4.2.2 The DSENT Tool                                      | 58 |

|   | 4.3 | DELPHI                                                    | 60 |

|   |     | 4.3.1 The DELPHI Flow                                     | 61 |

|   |     | 4.3.2 Strengths of the DELPHI Approach                    | 66 |

|   |     | 4.3.3 Limitations of the DELPHI Approach                  | 67 |

|   | 4.4 | Evaluation                                                | 69 |

|   |     | 4.4.1 Methodology                                         | 69 |

|   |     | 4.4.2 Results                                             | 70 |

|   | 4.5 | Related Work                                              | 75 |

| 5 | Nau  | tilus - Guided IP Optimization                  | 77  |

|---|------|-------------------------------------------------|-----|

|   | 5.1  | Introduction                                    | 78  |

|   | 5.2  | Background: Genetic Algorithms                  | 81  |

|   | 5.3  | Incorporating Author Knowledge                  | 84  |

|   |      | 5.3.1 Nautilus Hints                            | 85  |

|   | 5.4  | Evaluation                                      | 88  |

|   |      | 5.4.1 Methodology                               | 88  |

|   |      | 5.4.2 Results                                   | 89  |

|   | 5.5  | Related Work                                    | 93  |

| 6 | IRIS | S - IP Instrumentation & Introspection          | 95  |

|   | 6.1  | Introduction                                    | 96  |

|   | 6.2  | The IRIS Framework                              | 97  |

|   |      | 6.2.1 IRIS Instrumentation Library              | 99  |

|   |      | 6.2.2 IRIS Introspection Engine                 | 104 |

|   |      | 6.2.3 IRIS Visualization Engine                 | 105 |

|   | 6.3  | Evaluation                                      | 106 |

|   |      | 6.3.1 Hardware Implementation Characteristics   | 106 |

|   |      | 6.3.2 IRIS Instrumentation in CONNECT           | 109 |

|   | 6.4  | Related Work                                    | 113 |

| 7 | Putt | ing It All Together                             | 115 |

|   | 7.1  | Fast NoC Design Cost and Performance Estimation | 115 |

|   | 7.2  | High-level NoC Configuration and Optimization   | 116 |

|   | 7.3  | Effortless Monitoring and Debugging             | 119 |

| 8  | Conclusions                                            | 123   |

|----|--------------------------------------------------------|-------|

|    | 8.1 Future Directions                                  | . 125 |

| Ар | opendix A CONNECT Command-Line Interface Options       | 127   |

| Ap | opendix B DELPHI Flow Overview                         | 133   |

| Ар | opendix C IRIS Event Specification and Output Examples | 139   |

|    | C.1 IRIS Event Specification                           | . 139 |

|    | C.2 IRIS Event Output Example                          | . 142 |

# **List of Figures**

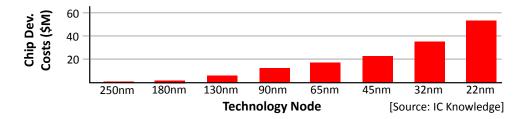

| 1.1 | Chip Development Cost by Process Node.                                       | 2  |

|-----|------------------------------------------------------------------------------|----|

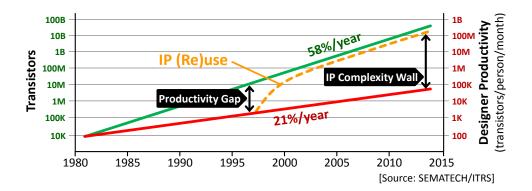

| 1.2 | The Design Productivity Gap and IP Complexity Wall.                          | 3  |

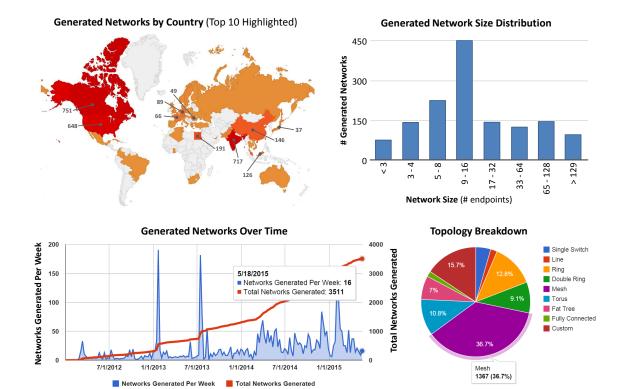

| 2.1 | CONNECT Network Generation Statistics.                                       | 11 |

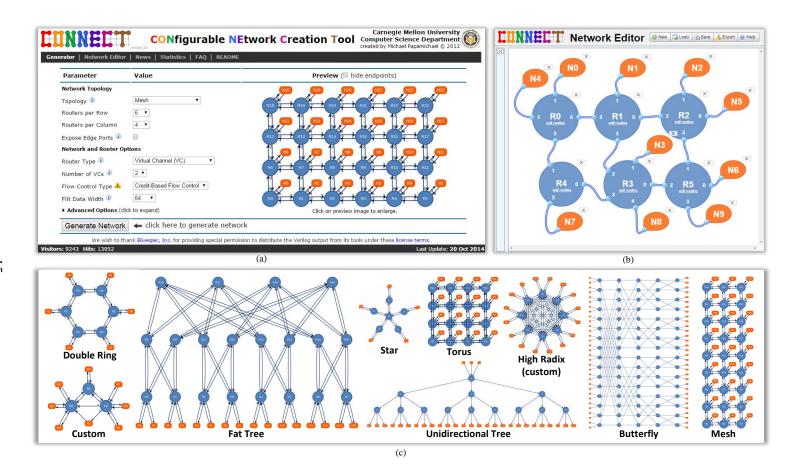

| 2.2 | The Web-Based CONNECT NoC Generator (a) and Network Editor (b) along with    |    |

|     | Samples of Pre-Selected and Custom Topologies (c).                           | 15 |

| 2.3 | High-Level Architectural Diagram of a CONNECT Router.                        | 17 |

| 2.4 | FPGA Efficiency and Network Performance Comparison of CONNECT-Generated      |    |

|     | RTL Against High-Quality ASIC-Oriented RTL [98] for a 4x4 Mesh Network       | 23 |

| 2.5 | Performance of Four Sample CONNECT Networks Under "Uniform Random" and       |    |

|     | "Unbalanced" Traffic                                                         | 24 |

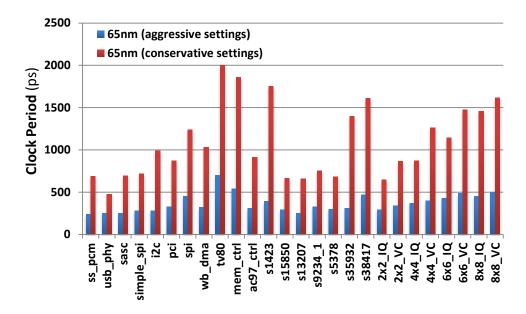

| 4.1 | Clock Period with Aggressive vs. Conservative Synthesis Settings             | 56 |

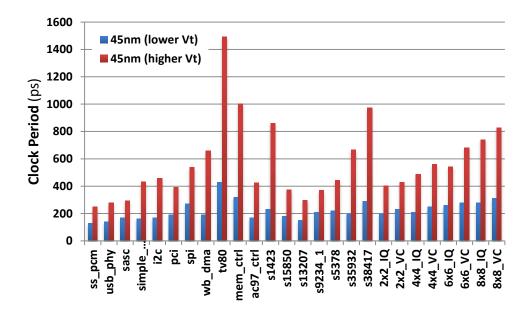

| 4.2 | Clock Period with Lower vs. Higher Vt Cells.                                 | 57 |

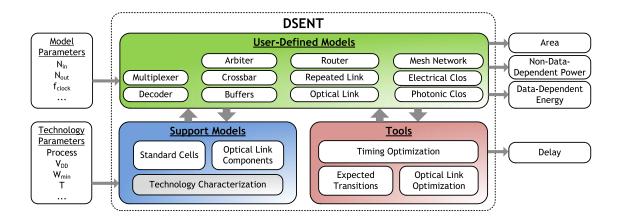

| 4.3 | DSENT Internal Hierarchy (with authors' permission).                         | 58 |

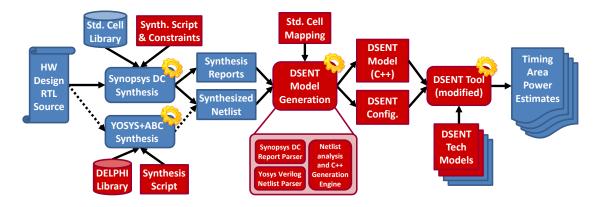

| 4.4 | The DELPHI Flow (parts shown in red were developed or modified in support of |    |

|     | the DELPHI flow, or produced by the DELPHI flow).                            | 59 |

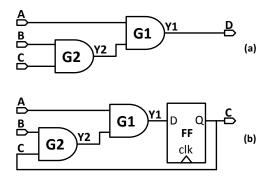

| 4.5 | Probability Propagation Example Circuits.                                    | 64 |

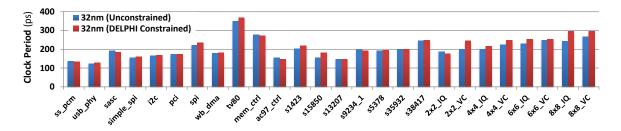

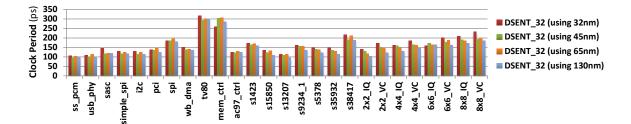

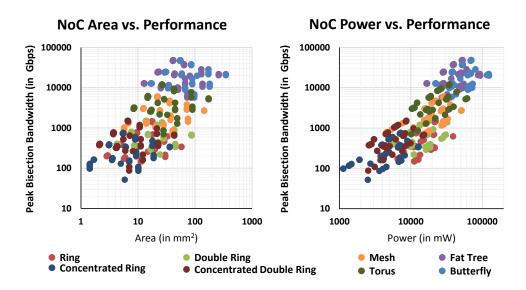

| 4.6  | Timing Estimates of Regular vs. DELPHI-Constrained Synthesis.              | 71 |

|------|----------------------------------------------------------------------------|----|

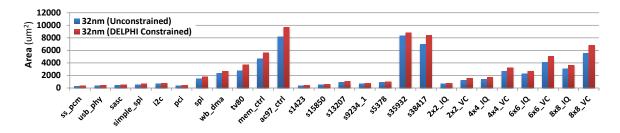

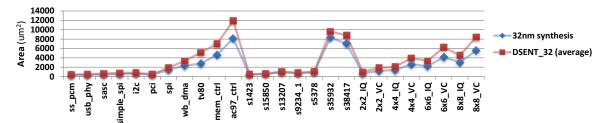

| 4.7  | Area Estimates of Regular vs. DELPHI-Constrained Synthesis                 | 71 |

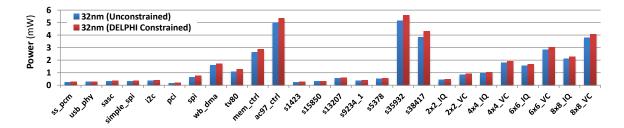

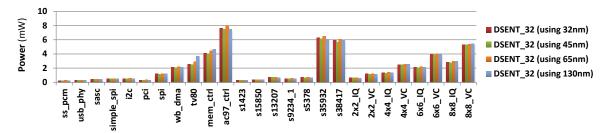

| 4.8  | Power Estimates of Regular vs. DELPHI-Constrained Synthesis                | 71 |

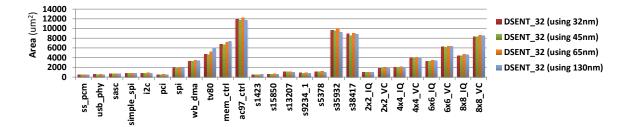

| 4.9  | Timing Estimates of Four DSENT Design Models All Targeting DSENT_32, But   |    |

|      | Generated Using Different Intermediate Synthesis Results.                  | 71 |

| 4.10 | Area Estimates of Four DSENT Design Models All Targeting DSENT_32, But     |    |

|      | Generated Using Different Intermediate Synthesis Results                   | 72 |

| 4.11 | Power Estimates of Four DSENT Design Models All Targeting DSENT_32, But    |    |

|      | Generated Using Different Intermediate Synthesis Results                   | 72 |

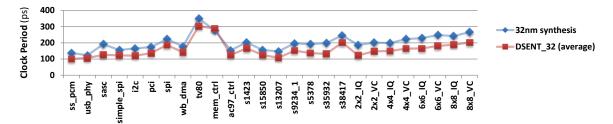

| 4.12 | Comparing Trends Between the Average Timing Estimates of Four DSENT Models |    |

|      | Targeting DSENT_32 vs. 32nm Synthesis Results                              | 72 |

| 4.13 | Comparing Trends Between the Average Area Estimates of Four DSENT Models   |    |

|      | Targeting DSENT_32 vs. 32nm Synthesis Results                              | 72 |

| 4.14 | Comparing Trends Between the Average Power Estimates of Four DSENT Models  |    |

|      | Targeting DSENT_32 vs. 32nm Synthesis Results                              | 73 |

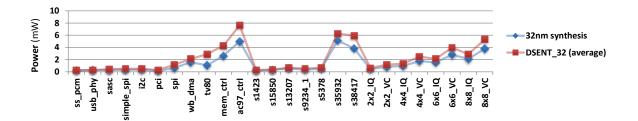

| 5.1  | LUT Usage and Maximum Frequency for Approximately 30,000 Router Design     |    |

|      | Points Based on FPGA Synthesis Results.                                    | 79 |

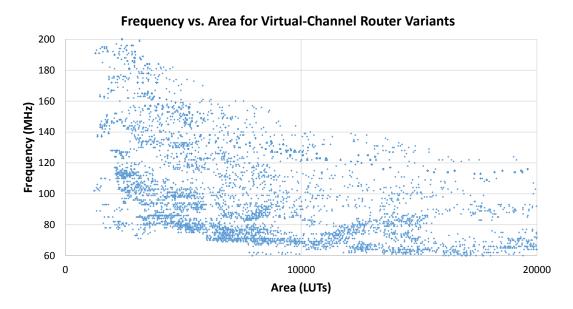

| 5.2  | Area, Power, and Performance for Various 64-Endpoint CONNECT NoCs Target-  |    |

|      | ing a Commercial 65nm ASIC Technology Node.                                | 80 |

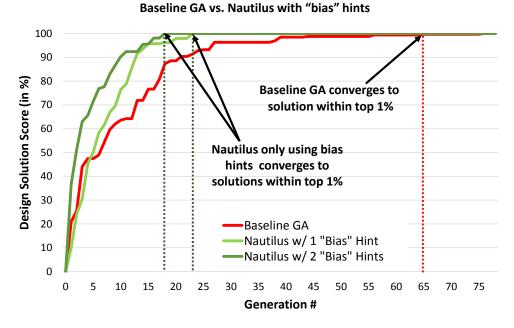

| 5.3  | Baseline GA vs. Nautilus Only Using 1 or 2 "Bias" Hints                    | 85 |

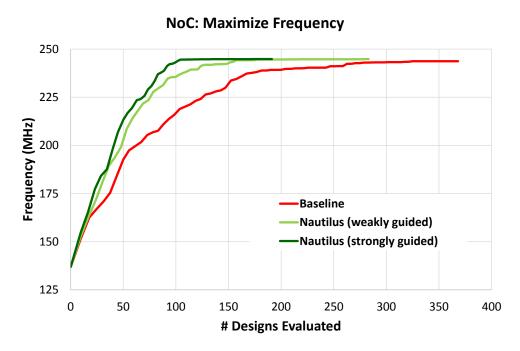

| 5.4  | Maximizing Frequency in the NoC Design Space.                              | 90 |

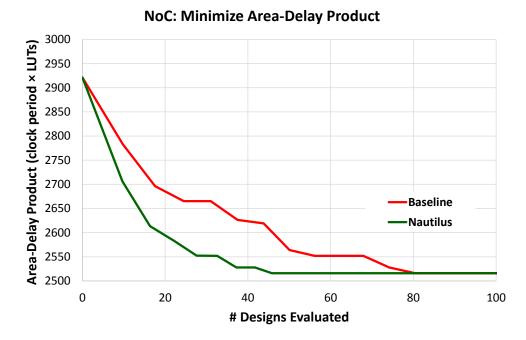

| 5.5  | Minimizing the Area-Delay Product in the NoC Design Space.                 | 91 |

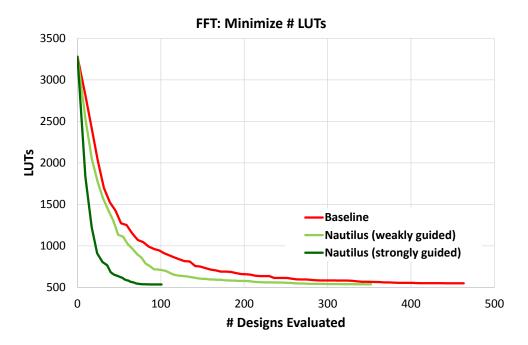

| 5.6  | Minimizing the Number of LUTs in the FFT Design Space                      | 92 |

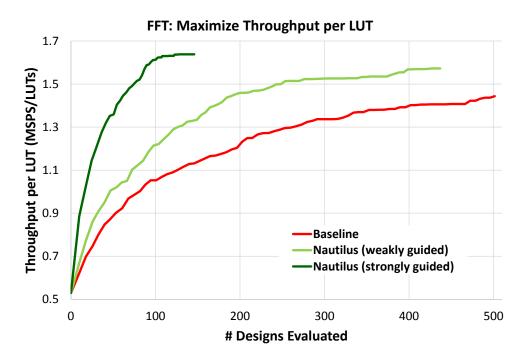

| 5.7  | Maximizing Throughput per LUT in the FFT Design Space.                     | 93 |

| 6.1 | IRIS Usage Flow                                                                |

|-----|--------------------------------------------------------------------------------|

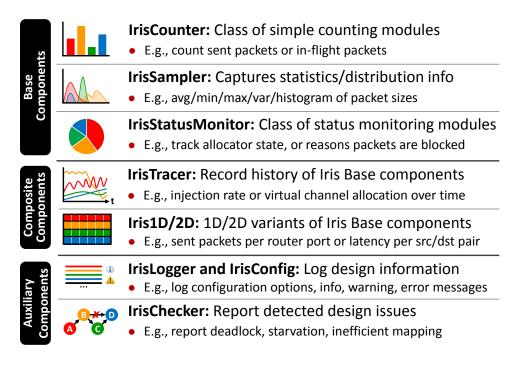

| 6.2 | Overview of IRIS Components                                                    |

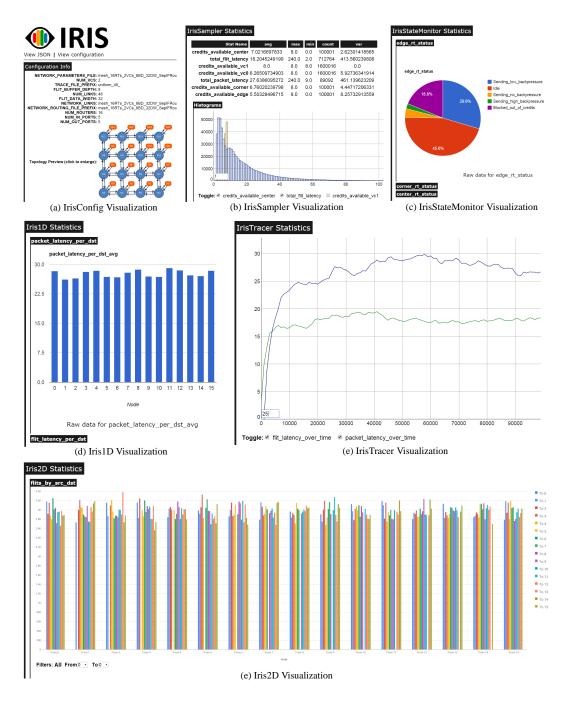

| 6.3 | Examples of How Different IRIS Components are Presented by the IRIS Visual-    |

|     | ization Engine (IVE)                                                           |

| 7.1 | Example Snapshots of the DELPHI-Powered Interface, which Provides Real-Time    |

|     | Hardware Implementation and Performance Estimates for CONNECT Network          |

|     | Configurations                                                                 |

| 7.2 | Example Snapshots of the Nautilus-Powered CONNECT Configuration Interface      |

|     | Highlighting the Area vs. Bandwidth Trade-Off Slider Subinterface              |

| 7.3 | Example Snapshots of the Nautilus-Powered CONNECT Configuration Interface      |

|     | Highlighting the Constraint-Driven Single-Metric Optimization Subinterface 120 |

| 7.4 | Snapshot Showing the Various IRIS-Powered CONNECT Instrumentation Options. 121 |

# **List of Tables**

| 2.1 | Sample CONNECT NoC Implementation Results for a 32nm ASIC Commercial     |

|-----|--------------------------------------------------------------------------|

|     | Standard Cell Library and a Xilinx LX760T FPGA                           |

| 4.1 | State Probabilities Over Successive Iterations                           |

| 4.2 | Sample NoC Power Study Using the DELPHI Flow                             |

|     |                                                                          |

| 6.1 | Common IRIS Component Parameters                                         |

| 6.2 | IrisCounter Parameters, Features, and Methods                            |

| 6.3 | IrisSampler Parameters, Features, and Methods                            |

| 6.4 | IrisStateMonitor Parameters, Features, and Methods                       |

| 6.5 | FPGA Synthesis Estimates for Various IrisCounter Configurations          |

| 6.6 | FPGA Synthesis Estimates for Various IrisSampler Configurations          |

| 6.7 | FPGA Synthesis Estimates for Various IrisStateMonitor Configurations 109 |

### Chapter 1

### Introduction

We are currently witnessing fundamental and disruptive changes in the semiconductor industry. On the one hand, rapidly growing transistor counts driven by Moore's Law [74], coupled with recent technology advances and trends, such as die stacking and the increased presence of on-die reconfigurable logic, are enabling the development of massive, diverse Systems-on-Chip (SoCs) comprising of tens or even hundreds of interacting Intellectual Property (IP) blocks with unique and demanding communication requirements. On the other hand, our inability to further scale supply voltage is leading to the breakdown of classical CMOS scaling as described by Dennard [36]. As a result, after decades of continuous growth, transistor efficiency, which has been the primary driving force behind performance improvements in general-purpose computing, has now reached a stalemate [41, 106].

In an effort to continue increasing performance in the power-constrained setting of the post-Dennard era, there is a growing interest in hardware specialization [89]. While hardware specialization is key to power-efficient computing, hardware development today is notoriously hard. As a result, even though there is great demand for mapping applications to specialized hardware to

Figure 1.1: Chip Development Cost by Process Node.

achieve higher performance and power efficiency, and despite the availability of an ever-growing number of rich Intellectual Property (IP) block catalogs, hardware development today is not only limited to experts, but takes more time, requires larger design teams, and is more expensive than ever (Figure 1.1).

### 1.1 The Rise of Hardware Complexity

An alarming trend of increasing complexity in hardware design was first recognized about fifteen years ago and was labeled the "design productivity gap" (Figure 1.2), which pertains to the difference between the transistors available on a single die and the number of transistors a designer is able to effectively design for. Efforts to bridge this gap sparked research efforts in multiple aspects of hardware design, including high-level synthesis techniques [44, 65], validation tools, more powerful hardware description languages [20, 102] and frameworks [95] that enable the development of flexible IP generators and new hardware design methodologies, such as platform-based design [53].

Of particular interest to this work is the increased use of IP blocks (which refer to pre-made, pre-validated, reusable packaged units of hardware design). With IP reuse, instead of designing every component in a chip from scratch, designers build entire chips or portions thereof by leveraging existing IP blocks, often developed by third parties. This practice greatly reduces the development

Figure 1.2: The Design Productivity Gap and IP Complexity Wall.

time and cost of individual submodules within a larger chip. Sure enough, IP reuse is ubiquitous today and has become an indispensable part of modern chip design. Over the years, IP blocks, which started as simple design instances, have now evolved to sophisticated, highly-parameterized and complex domain-specific IP generators responsible for multi-million-transistor blocks in a chip.

The IP Complexity Wall. Despite an enormous rise in scale, complexity, and specialization, the way IP blocks are developed and used has not fundamentally changed since the introduction of modern Hardware Description Languages (HDLs) and the proliferation of ASIC-based design flows more than two decades ago. The result is a "complexity explosion" as designers build chips as "fragile" collections of many complex IP blocks, each with its own set of cryptic (for the non-domain-expert) low-level knobs, which can often be traced back to a crude hardware schematic or specification document. Today, we are facing a new encounter with the "design productivity gap" at a different scale—not at the level of the transistor, but instead at the level of the IP block. Current hardware design methodologies are struggling to keep up with the complexity involved in configuring, tuning, integrating, and validating the multiple interacting IP blocks within a modern chip. Consequently, the complexity and the associated development time, cost, and manpower required to build a chip today continue to increase prohibitively.

### **1.2 Pandora: Facilitating IP Development for Hardware Specializa**tion

The focus of this thesis is on a novel knowledge-encapsulating IP development paradigm, called Pandora<sup>1</sup>, that is aligned with existing efforts to tackle design complexity and aims at retaining the benefits of highly parameterized IP design and generation to facilitate hardware specialization, while at the same time addressing the associated complexity explosion. The Pandora paradigm is motivated by the highly specialized nature of modern IP blocks and argues for tailoring them with supporting functionalities according to their specific application domain. Pandora's ultimate goal is to lower the barrier-to-entry for building specialized hardware accelerators and allowing application-experts to more easily and efficiently realize their ideas in hardware.

In Pandora, IP blocks not only capture the microarchitectural or low-level structural view of a design, but also encapsulate domain-specific infrastructure and additional dimensions of knowledge that the IP author has to offer. The Pandora paradigm marks a departure from the current status quo in hardware design by combining a set of key ideas and principles that empower IP authors and enhance how users interact with hardware IPs. The three defining aspects of the Pandora IP paradigm can be summarized as:

- Facilitate fast detailed IP design space characterization to help the user understand the effects of parameter choices and allow for obtaining quick estimates with respect to hardware implementation and IP-specific metrics.

- Provide application-level goal-oriented domain-specific optimization interfaces that are mean-

<sup>&</sup>lt;sup>1</sup>The name Pandora is inspired from Greek mythology and has a dual meaning. The first meaning relates to how Pandora was created through unique gifts from each god, which resembles how the proposed design paradigm encapsulates rich domain-expert ("gods") knowledge to support complexity-reducing interfaces, mechanisms, and tools ("gifts"). The second meaning pertains to Pandora's box, which kept sealed all of the evils of the world, similar to how the proposed hardware design paradigm tries to hide or restrain complexity within the IP and avoid exposing the user to the "evils" or complexities of hardware design.

ingful to the IP user and automatically set low-level structural parameters to achieve the desired design optimizations.

• Support purpose-built domain-aware simulation-time and run-time instrumentation and introspection mechanisms that gather, present, and analyze the gathered data to identify or even diagnose higher-order correctness and performance issues.

In addition to keeping complexity under control and boosting productivity, Pandora also dramatically reduces the combined total effort because work that would otherwise be repeated by each IP user, is now only performed once by the authors of the IP.

As part of my work on Pandora, I have developed CONNECT, DELPHI, Nautilus, and IRIS. CONNECT [68, 81, 82] is a flexible Network-on-Chip (NoC) IP generator I developed and publicly released, that is actively used by hundreds of researchers around the world, and has both served as an inspiration as well as demonstration vehicle for Pandora. DELPHI [84] is a framework for performing fast and efficient IP characterization (power, area, frequency) across multiple technology nodes. Nautilus [83] is a high-level goal-oriented IP optimization engine that uses modified genetic algorithms that incorporate IP author knowledge to perform fast guided design space search. IRIS is an IP instrumentation framework that facilitates system-level debugging, monitoring, and analysis. In the context of this thesis, the CONNECT NoC IP generator highlights the benefits of specialization and serves as a driving example for Pandora, while DELPHI, IRIS, and Nautilus serve as demonstration vehicles for Pandora's key principles.

### **1.3 Thesis Contributions**

This thesis makes the following contributions:

• Proposes the Pandora IP development paradigm and demonstrate many of its key principles

through the development of CONNECT, DELPHI, Nautilus, and IRIS.

- Presents the CONNECT Network-on-Chip IP Generator, which is actively used by hundreds of researchers around the world.

- Demonstrates the benefits of hardware specialization through an investigation of interconnect specialization and tuning in the context of FPGAs and CoRAM applications.

- Presents DELPHI, a framework for fast, easy, efficient RTL-based characterization of IP designs.

- Presents Nautilus, which demonstrates how IP author knowledge can be used to vastly accelerate hardware IP optimization and design space search using guided genetic algorithms.

- Proposes and develops IRIS, a flexible systematic instrumentation framework that allows incorporating IP author knowledge for efficient hardware debugging and system-level monitoring.

- Demonstrates how Pandora can drastically enhance how IP users interact with IP generation frameworks by developing and showcasing a proof-of-concept Pandora-powered version of the CONNECT Network-on-Chip IP generator that incorporates the key ideas and research artifacts presented in this thesis.

### **1.4 Thesis Organization**

The remainder of this thesis is organized as follows. Chapter 2 describes the CONNECT Network-on-Chip IP generator that was developed and extended in support of this thesis, and demonstrates how CONNECT allows specializing the generated NoC IP instances for the underlying hardware, as well as the traffic characteristics of a given application. Chapter 3 presents the Pandora IP development paradigm and elaborates on the Pandora principles, which are demonstrated through the frameworks described in the next three chapters. In particular, Chapter 4 presents the DELPHI framework for fast IP characterization. Chapter 5 presents the Nautilus IP optimization framework and Chapter 6 presents the IRIS instrumentation and introspection framework. Chapter 7 describes how the CONNECT Network-on-Chip IP generator was extended to incorporate and demonstrate many of the Pandora key ideas and research artifacts presented in this thesis. Finally, Chapter 8 concludes and discusses potential future directions.

### Chapter 2

# The CONNECT Network-on-Chip IP Generator

### 2.1 Introduction

Today's integrated circuits contain billions of transistors organized as tens to hundreds of interacting modules as a System-on-Chip (SoC). As the scale and complexity of modern SoCs grow, building the on-chip interconnect to enable this vast number of modules to communicate is an increasingly important and challenging task. As a result, the interconnect has become a central element in modern chip designs. Previously, the communication needs of smaller, simpler chip designs with just a handful of major modules could be met by ad-hoc point-to-point wires or a shared bus. Such approaches do not scale to handle the more complex and demanding communication requirements of the interacting modules in today's SoCs. This realization led to a push towards more sophisticated and scalable systematic interconnect schemes, like Networks-on-Chip (NoCs), which, as the name implies, implement a dedicated network of links and routers to act as the communication substrate of a chip [33].

The proliferation of NoCs has been followed by a surge in NoC-related research that spans all the way from low-level hardware implementation issues, such as efficient allocator designs, to higher level issues that affect the application, such as providing traffic isolation or Qualityof-Service guarantees. As a result, NoC designs today form a broad and very diverse landscape that mirrors the equally diverse communication needs and requirements of the various applications running on modern SoCs. Despite this vast design space and the fact that there is no "one-size-fitsall" solution to the interconnect problem, deployable NoC IPs currently available to the research community are limited to fixed NoC instances or target only localized portions of the NoC design space.

**CONNECT.** In an effort to support my work on Pandora and significantly expand the NoC options available to academic and other research communities, we developed and released CON-NECT, a flexible NoC IP generation engine that produces high quality synthesizable<sup>1</sup> Verilog RTL NoC implementations. CONNECT, evolved from a tool originally created to support our own FPGA-specialized NoC design exploration research [27, 29, 81, 82] and was publicly released in 2012 in the form of a web-based NoC generation service (http://www.ece.cmu.edu/calcm/connect). CONNECT allows quickly navigating the NoC design space and generating fast lightweight NoC IPs. To satisfy the diverse communication needs and design constraints of different applications, CONNECT offers a high degree of parameterization to support a very wide range of NoC design variants. By adhering to a set of common interfaces, CONNECT allows for quickly switching between different NoC alternatives, thus enabling rapid experimentation and prototyping.

<sup>&</sup>lt;sup>1</sup>Synthesizable designs are those described at a sufficient level of detail for Electronic Design Automation (EDA) tools to implement them or "synthesize" them in hardware, e.g., using FPGA or ASIC design flows.

Figure 2.1: CONNECT Network Generation Statistics.

Since its release in 2012, CONNECT has been used by a growing number of users around the world. As of this writing, the CONNECT website has seen more than 15,000 hits and 10,000 unique visitors. The CONNECT service has generated more than 3,500 networks for more than 800 users in more than 50 countries. There have been multiple third-party research papers that use CONNECT to generate NoCs for design space research or for direct use as production IP in design projects. Figure 2.1 shows collected network generation statistics, such as topology breakdown and network size, to give a sense of the types and scale of networks that CONNECT users have requested. More detailed statistics and usage information are available on the CONNECT website [68].

### 2.2 Background: NoC Terminology

This section offers a brief review of key NoC terminology and concepts relevant to this chapter. For a more comprehensive introduction please see [31]. Readers already familiar with NoCs may continue directly to Section 2.3.

**Topology.** The topology of a network specifies how routers and endpoints are arranged and connected.

**Packets.** A packet is the basic logical unit of transfer within the network and can consist of multiple flits (see below).

**Flits.** When traversing a network, packets are often broken into flits (flow control digits), which are the basic unit of resource allocation and flow control within the network. Some NoCs require special additional "header" or "tail" flits to carry control information and to mark the beginning and end of a packet.

**Head-of-line Blocking.** Head-of-line blocking [63] refers to a situation where the first packet in a queue is blocking all the remaining packets waiting in the queue, when they could otherwise be making progress (if not for the first "stuck" packet). Head-of-line blocking can severely limit network performance.

**Virtual Channels.** A channel corresponds to a path between two points in a network. NoCs often employ a technique called virtual channels (VCs) to provide the abstraction of multiple logical channels over a physical underlying channel. Routers implement VCs by having non-interfering flit buffers for different VCs and time-multiplexed sharing of the switches and links. Thus, the number of implemented VCs has a large impact on the buffer requirements of an NoC. Employing VCs can help in the implementation of protocols that require traffic isolation between different message classes (e.g., to prevent deadlock [32]), but can also increase network performance by reducing the effects of head-of-line blocking.

**Deadlock.** Deadlock refers to a situation where there is a cyclic dependency involving multiple network resources (e.g., buffer space), which is preventing the network from making any progress.

**Quality-of-Service (QoS).** QoS refers to a network's capability of providing guarantees (e.g., with respect to latency or bandwidth) or prioritizing specific types of traffic over others.

**Flow Control.** In lossless networks a router can only send a flit to a downstream receiving router if it is known that the downstream router's buffer has space to receive the flit. "Flow control" refers to the protocol for managing and negotiating the available buffer space between routers. Due to physical separation and the speed of router operation, it is not always possible for the sending router to have immediate, up-to-date knowledge of the buffer status at the receiving router. In credit-based flow-control, the sending router tracks credits from its downstream receiving routers. At any moment, the number of accumulated credits indicates the guaranteed available buffer space (equal to or less than what is actually available due to delay in receiving credits) at the downstream router's buffer. Flow control is typically performed on a per-VC basis.

Input-Output Allocation. Allocation refers to the process or algorithm of matching a router's

input requests with the available router outputs. Different allocators offer different trade-offs in terms of hardware cost, speed and matching efficiency. Separable allocators [31] form a class of allocators that are commonly used in NoCs. They perform matching in two independent steps, which sacrifices matching efficiency for speed and low hardware cost.

**NoC Performance Characterization.** The most common way of characterizing an NoC is through load-delay curves, which are obtained by measuring packet delay under varying degrees of load for a set of traffic patterns. A common metric for load is the average number of injected flits per cycle per network input port. Packet delay represents the elapsed time from the cycle the first flit of a packet is injected into the network until the cycle its last flit is delivered. For a given clock frequency, load and delay are often reported in absolute terms, e.g., Gbits/s and ns.

### 2.3 NoC Design Parameterization

Besides CONNECT, there are several other freely available synthesizable NoC IPs (e.g., [12, 43, 92, 98]; additional examples and discussion in Section 2.7). These IPs typically come in the form of structural RTL design modules. As such, their parameterization is limited by the expressiveness of current hardware description languages, such as Verilog or VHDL. The static nature of these design modules limits their configurability (e.g., usually restricted to a single or a limited set of topology configurations). IP users trying to use such NoC IPs also have to deal with low-level details, such as editing RTL design files to set parameters or configure individual routers and writing additional RTL code to arrange routers in a desired topology and populate routing tables.

Figure 2.2: The Web-Based CONNECT NoC Generator (a) and Network Editor (b) along with Samples of Pre-Selected and Custom Topologies (c).

CONNECT embodies many of the Pandora key principles discussed in Chapter 3. One of CON-NECT's main goals is to drastically reduce the complexity involved in configuring and generating working NoC designs. To this end, CONNECT offers a "push-button" solution for generating a very wide range of NoC configurations. To support a high degree of parameterization, which spans multiple key NoC design choices (e.g., topology, router architecture, flow control, allocation algorithms, pipelining options, buffer sizing, etc.), the CONNECT NoC generation engine dynamically generates the requested NoC designs on-demand. The rich design space of CONNECT NoC IPs is presented to the user through a web-based front-end interface, which consists of multiple highlevel user-friendly configuration interfaces that are dynamically updated to guide users while they interact with the generator. Figure 2.2 shows screenshots of CONNECT's web interface along with sample network topologies. CONNECT's main interface offers support for a wide range of common network topologies and displays a dynamically-generated visual preview of the router and endpoint arrangement for each candidate network. Below we highlight CONNECT's most prominent configuration options with emphasis on network topology and router design options.

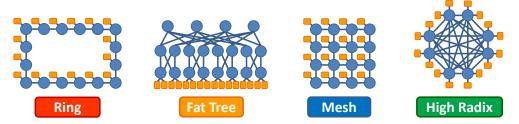

#### 2.3.1 Network Topologies

CONNECT offers direct support for a wide range of pre-selected common unidirectional and bidirectional topologies (single switch, ring, double ring, star, mesh, torus, fat tree, fully connected, butterfly, distribution/aggregation tree). Each supported topology family includes its own extensive set of scaling and configuration parameters. CONNECT also populates the routing tables in each network using a default routing scheme according to the selected topology variant (which the user is free to override). This wide range of topology and configuration options allows a meaningful degree of customization to satisfy the connectivity needs of many common applications with a very low barrier-to-entry and this is already an important capability over other available NoC IP alternatives,

Figure 2.3: High-Level Architectural Diagram of a CONNECT Router.

which typically only target a single fixed topology and often require significant knowledge and manual effort to configure.

In addition to the pre-selected set of topologies described above, the CONNECT NoC generator also supports the creation of custom arbitrary-topology NoCs through the use of a visual network editor (Figure 2.2 (b)) or by using a custom network specification language. These advanced interfaces allow for instantiating routers of different radix, mixing unidirectional and bidirectional links, and attaching multiple (or no) endpoints to each router in the generated network. This high degree of customization allows expert users to build networks that precisely match the connectivity and communication characteristics of their application. Figure 2.2 (c) shows samples of some of CONNECT's pre-selected topologies, as well as some instances of custom topologies.

#### 2.3.2 Router Architectures

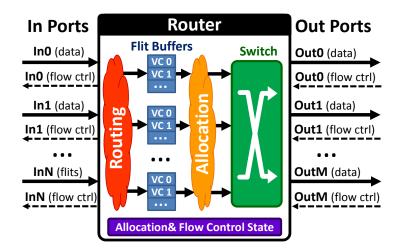

Figure 2.3 shows an abstracted block diagram of the basic structure of a CONNECT router. Communication with other routers happens through input and output port interfaces, which can vary in number depending on the router configuration. Each input (or output) port interface consists of two channels; one channel for receiving (or sending) data and one side channel running in the opposite direction for flow control. Input and output interfaces are either connected to network endpoints or are used to form links with other routers in the network. Optional auxiliary signaling is available to query each router's unique ID and to dynamically update routing information.

To tailor to a wide variety of diverse application communication requirements and to meet different design objectives, CONNECT routers are available in three major variants: "Virtual Channel", "Virtual Output Queued", and "Input Queued".

- Virtual Channel (VC): The VC router supports a variable number of VCs and organizes incoming traffic at each input into separate buffers based on VC information carried by packets. Employing VCs can help in the implementation of protocols that require enforcing Qualityof-Service (QoS) guarantees, such as traffic isolation and prioritization between different message classes (e.g., prioritize responses over requests to prevent deadlock [32]), but can also be used to increase network performance by mitigating the effects of head-of-line blocking [63].

- Virtual Output Queued (VOQ): The VOQ router can offer the highest performance out of the three supported architectures. For each input it steers incoming traffic into per-output dedicated buffers, eliminating the effects of head-of-line blocking and offering very high levels of performance that can approach that of an ideal (but impractical) output-queued router architecture [31]. VOQ routers are well suited for demanding applications with heavy communication requirements and less structured traffic patterns that would still suffer from head-of-line blocking using a conventional VC-based router.

- Simple Input Queued (IQ): The IQ router employs a single buffer per router input and is often well suited as a baseline design. It is useful for building simple bare-bones NoCs for applications that require basic connectivity at low hardware cost. NoCs built around IQ

routers are a good match for applications with non-critical or simple communication needs that do not require the isolation, prioritization, or higher performance offered by the VC and VOQ router architectures.

For each of the variants above, CONNECT allows configuring an extensive set of low-level details, including different pipelining options, multiple allocator alternatives, and flexible usereditable routing, to enable implementation-level trade-offs with respect to performance, area, frequency, as well as to meet specific traffic prioritization and fairness goals. CONNECT also offers support for two interfacing options that implement different flow control protocols ("credit-based" and "peek" [81]) to better match the communication assumptions and requirements of a given application.

# 2.4 Generated NoCs

NoCs are typically used or studied as part of larger designs with multiple interacting modules that exhibit diverse communication characteristics and often impose stringent hardware resource constraints. Thus, in addition to providing a wide range of design options to meet the communication demands of a given design, it is also important for CONNECT to produce high-quality NoC implementations that map well to the available hardware resources. To this end, all NoC IPs generated by CONNECT, including any debug and instrumentation structures, comprise of fully synthesizable Verilog descriptions that map efficiently to both Field Programmable Gate Arrays (FPGAs) and Application Specific Integrated Circuits (ASICs). Moreover, to ensure that CONNECT NoCs can coexist in harmony and share resources with other hardware-resident components in FPGA environments with tight resource constraints, CONNECT is capable of generating very lightweight NoCs by taking special consideration of unique FPGA implementation characteristics.

|                         | Network Details |         |          |          | FPGA Implementation (LX760T) |           |                | ASIC Implementation (32nm) |           |                |

|-------------------------|-----------------|---------|----------|----------|------------------------------|-----------|----------------|----------------------------|-----------|----------------|

| Network                 | Link            | Ports / | #Routers | #Virtual | Area                         | Max Freq. | Peak Bisection | Area                       | Max Freq. | Peak Bisection |

| (# indicates endpoints) | Width           | Router  | (Arch.)  | Channels | (% LUTs)                     | (MHz)     | BW (in Gbps)   | (um <sup>2</sup> )         | (GHz)     | BW (in Gbps)   |

| Ring_128                | 128             | 2       | 128 (IQ) | N/A      | 9.0                          | 312       | 80             | 566406                     | 5.0       | 1278           |

| Ring_64                 | 64              | 2       | 64 (VC)  | 2        | 3.3                          | 250       | 32             | 294455                     | 4.2       | 538            |

| DoubleRing_16           | 48              | 3       | 16 (VC)  | 4        | 1.8                          | 160       | 31             | 102095                     | 1.8       | 342            |

| DoubleRing_32           | 64              | 3       | 32 (VC)  | 2        | 2.8                          | 177       | 45             | 144086                     | 4.0       | 1014           |

| FatTree_16              | 32              | 4       | 20 (VOQ) | N/A      | 2.0                          | 138       | 71             | 22208                      | 4.0       | 2067           |

| Mesh_16 (4x4)           | 32              | 4       | 16 (VC)  | 4        | 2.9                          | 116       | 30             | 78458                      | 3.5       | 907            |

| Mesh_48 (6x8)           | 24              | 4       | 48 (VC)  | 2        | 3.0                          | 124       | 24             | 49862                      | 4.3       | 821            |

| Torus_20 (4x5)          | 64              | 5       | 16 (VOQ) | N/A      | 5.7                          | 128       | 131            | 49230                      | 4.7       | 4768           |

| FullyConnected_8        | 32              | 8       | 8 (VC)   | 2        | 3.2                          | 85        | 22             | 19817                      | 4.2       | 1079           |

| HighRadixCustom_16      | 48              | 9       | 8 (IQ)   | N/A      | 4.3                          | 78        | 30             | 31259                      | 5.1       | 1960           |

Table 2.1: Sample CONNECT NoC Implementation Results for a 32nm ASIC Commercial Standard Cell Library and a Xilinx LX760T FPGA.

To provide a broad indication of CONNECT NoC quality on FPGAs and ASICs, Table 2.1 shows implementation results for select realistic CONNECT NoC configurations. The presented network configurations capture a representative sample of CONNECT networks that vary in the number of endpoints, link width, number and architecture of routers, and number of virtual channels (when using VC routers). Results include maximum frequency, area, and peak bisection bandwidth based on synthesis estimates for FPGA and ASIC implementations. FPGA logic area is reported as a percentage of total FPGA LUT capacity (LX760T); it is worth noting that all of these sample networks fit well within 10% of a moderately-sized Xilinx LX760T FPGA.

#### 2.4.1 Specializaing for the FPGA Substrate

What is not apparent in Table 2.1 is that the detailed parameter settings leading to optimal results on FPGAs vs. ASICs can be drastically different because the two implementation environments are very different with respect to the relative speed and cost of logic, wires, and memory primitives. CONNECT takes into account the unique mapping and operating characteristics of FPGAs, such as their dense configurable routing substrate, on-chip storage peculiarities, and frequency limitations, to produce specialized NoCs that make very efficient use of FPGA resources.

We focus on these FPGA characteristics that influence fundamental CONNECT NOC design decisions: (1) the relative abundance of wires compared to logic and memory; (2) the scarcity of on-die storage resources in the form of a large number of modest-sized buffers; (3) the rapidly diminishing return on performance from deep pipelining; and (4) the field reconfigurability that allows for an extreme degree of application-specific fine-tuning.

**Abundance of Wires.** As previously also noted by other work [60], FPGAs are provisioned, even over-provisioned, with a highly and densely connected wiring substrate. As a result, wires are plentiful, or even "free", especially relative to the availability of other resources like configurable

logic blocks and on-chip storage. In CONNECT we make the datapaths and channels between routers as wide as possible to consume the largest possible fraction of the available (otherwise unused) wires. In addition, we also adapt the format of network packets; information that would otherwise be carried in a separate header flit is carried through additional dedicated control wires that run along the data wires. Finally, we also adapt flow control mechanisms to occupy fewer storage resources by using wider interfaces [81].

**Storage Shortage.** Modern FPGAs provide storage in two forms: (1) Block RAMs with tens of kilo-bits of capacity, and (2) small tens-of-bits Distributed RAMs built using logic Look-Up Tables (LUTs). Both of these monolithic memory macros can not be subdivided, which can lead to inefficiencies. This sets up a situation where NoCs on FPGAs pay a disproportionately high premium for storage because NoCs typically require a large number of buffers whose capacities are each much bigger than Distributed RAMs but much smaller than Block RAMs. To make the most efficient use of storage resources, CONNECT only uses Distributed RAM and implements multiple logical flit buffers in each physically allocated buffer on the FPGA. CONNECT does not use any Block RAMs, which are typically in high demand from the rest of the FPGA-resident user logic.

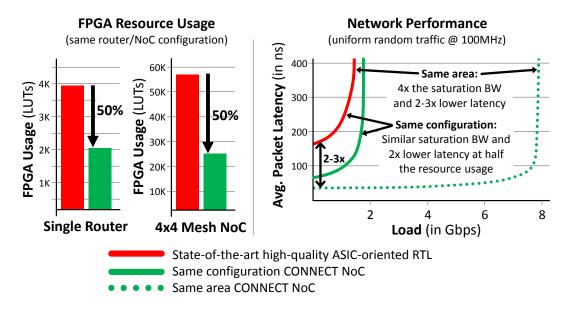

Low Clock Frequency. FPGA designs tend to operate at significantly lower clock frequencies compared to ASIC designs, which was one of the gaps studied in [58]. This frequency gap can be attributed to the use of LUTs and long interconnect wires and results in rapidly diminishing returns when attempting to deeply pipeline a FPGA design to improve its frequency. To minimize FPGA resource usage and network latency, CONNECT routers are based on a shallow single-cycle pipeline architecture. As we will see later, the single-stage router used in CONNECT reaches lower but still comparable frequency as an ASIC-tuned 3-stage-pipelined router. The FPGA's performance penalty from running at a lower frequency can be much more efficiently made up by

Figure 2.4: FPGA Efficiency and Network Performance Comparison of CONNECT-Generated RTL Against High-Quality ASIC-Oriented RTL [98] for a 4x4 Mesh Network.

increasing the width of the datapath and links or even switching to an entirely different topology.

**Reconfigurabilitiy.** Given the flexibility of FPGAs stemming from their reconfigurable nature, an effective NoC design is likely to be called to match up against a diverse range of applications. To cover the needs of such a diverse and rapidly changing set of applications, the CONNECT NoC generator is fully parameterized and more importantly topology-agnostic, which means that individual routers can be composed to form arbitrary custom network topologies. Moreover, to minimize changes in the user logic, all CONNECT networks adhere to the same simple standard common interface. From the user's perspective the NoC appears to be a plug-and-play black box device that receives and delivers packets. Rapid prototyping and design space exploration become effortless as any CONNECT network can be seamlessly swapped for another CONNECT network that has the same number of endpoints.

Figure 2.4 showcases an example of the efficiency benefits of CONNECT-generated NoCs

(a) Four sample CONNECT networks, all interchangeable from user perspective.

(a) Performance of four networks under "uniform random" and "90% neighbor" traffic.

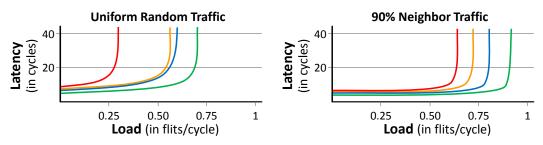

Figure 2.5: Performance of Four Sample CONNECT Networks Under "Uniform Random" and "Unbalanced" Traffic.

specially tuned for FPGAs [81]. When compared against a high-quality publicly available ASICoriented 4x4 mesh NoC [98], equivalent CONNECT-generated NoC instances can offer comparable network performance at one-half the FPGA resource cost; or alternatively, three to four times higher network performance at approximately the same FPGA resource cost.

#### 2.4.2 Specializing for the Application

In addition to specializing an IP's implementation for the hardware substrate, it is also important to specialize an IP for the specific usage scenario or application. As an example in the context of NoCs, consider the four NoCs shown in Figure 2.5 (a). All of these networks support 16 endpoints, and as such would be interchangeable from an application perspective. Figure 2.5 (b) shows the load-delay results for these four networks under two different traffic patterns, "uniform random", where the destination for each packet is randomly selected, and "unbalanced", where

90% of the generated packets are local and are sent to neighboring nodes. These two example traffic patterns can be thought of as corresponding to two different classes of applications, each with different degrees of local communication. The fact that the relative performance of each network drastically changes depending on the specific traffic pattern points to the importance of application-specific specialization of the NoC.

**Shrinkwrap.** In the Shrinkwrap work [27] we experimented with compiler-guided development of application-specific Networks-on-Chip within the CoRAM FPGA memory abstraction [28]. For this work, we extended CONNECT to support a class of tree-based topologies that were a good fit for the traffic patterns exercised by various CoRAM applications. Compared to using a baseline generic NoC, across a number of CoRAM application instances, the customized NoCs generated through CONNECT reduced FPGA resource usage (for the interconnect) by almost an order of magnitude, while retaining the same application performance levels as a baseline generic NoC [29]. As an example, the overall efficiency (throughput/area) gains for two FPGAbased applications (Dense Matrix Multiply and Black Scholes) from switching from a baseline generic mesh interconnect to a custom application-tuned tree-based interconnect ranged from 37% to 48%.

# 2.5 CONNECT Principles

Our motivation for developing and releasing the CONNECT NoC generation framework was to create a powerful and user-friendly research tool that would be useful to the broader research community. To achieve this goal we adhered to a set of design principles that span all aspects of CONNECT from front-end user interface to back-end hardware generation engine. Below we highlight some key design elements that we conscientiously engineered into CONNECT to enhance its usability as a NoC research tool. Matching Interfaces to User Expertise Level. CONNECT offers a variety of user interfaces for configuring and generating NoCs. These interfaces can take different forms and are tailored to the expertise of the specific IP user. They include a basic web-based front-end that offers a set of preconfigured common topologies and settings, a more advanced visual custom topology network editor coupled with a custom specification language that eliminates the need for low-level bug-prone RTL coding. To further aid IP users, CONNECT's interfaces also guard against erroneous configurations—which are a common problem when dealing with complex highly-parameterized IP blocks—by, for example, dynamically updating the available options as the user is making selections and automatically populating routing tables. In addition, the interface guides the user through visual cues (e.g., preview of topology and endpoint arrangement) and feedback (e.g., tips on how different options affect hardware implementation). Separately, for expert users who wish to drive CONNECT through the command-line or by automated scripts, we also provide a non-GUI command-line front-end (summarized in Appendix A) that generates NoC instances by remotely connecting to the CONNECT framework.

**Rapid Prototyping and Exploration.** The CONNECT NoC architecture is designed around a simple set of link-level interfaces that are common among all CONNECT-generated NoCs as to allow easy integration within a design project. From a user perspective, the NoC appears to be a plug-and-play black box module that receives and delivers packets. This simplifies rapid prototyping and design space exploration as all CONNECT NoCs with the same number of endpoints are interface-compatible at the network boundary. Moreover, CONNECT supports dynamic runtime updating of routing tables, which not only opens up interesting research directions, such as experimenting with adaptive routing techniques, but can also drastically reduce experiment turn-around time. Regarding the latter, a user can build a system around a dense highly-connected topology and then modify the routing scheme on the fly to emulate other topologies (e.g., overlay a ring or mesh on top of a torus), without having to repeat the time-consuming synthesis process, which can take many hours.

**Easy Integration.** In addition to the plug-and-play nature of the generated networks, CON-NECT also offers features specifically targeted at easing endpoint implementation. For example, "peek" flow control allows endpoints to directly observe buffer occupancy of routers (in lieu of credit-based protocols), and "virtual links" guarantee contiguous transmission and delivery of multi-flit packets eliminating the need for reassembly logic and buffering at the receiving endpoints. Features like these push complexity, which would otherwise be handled by the network endpoints, back into the network. Last but not the least, each generated NoC is accompanied by a host of supporting material, such as documentation, testbenches, scripts, as well as user-editable routing and topology files, all custom-generated to match the specific NoC configuration.

**CONNECT as a Service.** Behind the scenes, CONNECT is a sophisticated tool comprising of many components developed using several different tools. Releasing CONNECT to users as a self-maintained package would be quite challenging both in terms of initial installation (e.g., installing tools and libraries, setting up a proper environment, acquiring licenses, etc.) and continuing up-keep. To this end, we decided to release CONNECT in the form of a web-based IP generation service. This approach to IP dissemination reduces complexity for the user and greatly lowers the barrier to entry; the only requirement for generating CONNECT NoC designs is an internet connection. As an added benefit, having a single point of distribution allows quick and transparent delivery of bug fixes or improvements.

## 2.6 Pandora Motivation

Our experience with building and releasing CONNECT has provided us with invaluable insight into multiple aspects of IP development, dissemination, and usage. For NoC design experts, CONNECT is a very powerful tool in saving them the time and effort to code—not to mention debug—the Verilog design of the NoC; they only have to dial-in exactly the configuration they are looking for. However, user feedback has revealed that a large portion of CONNECT users are not NoC experts. This class of users do not know what configuration to ask for and many times do not understand all of the low-level NoC parameters that CONNECT offers.

We see in our generation statistics that most CONNECT users only configure very few highlevel parameters (and often suboptimally), such as topology or datapath width, and typically leave most other options, such as router architecture or allocator type, untouched, despite their significant impact on cost, performance, and correctness. This problem continues after non-NoC-expert users integrate a CONNECT NoC into their design, as they are likely to also be unable to properly diagnose performance and correctness issues (e.g., degraded performance or deadlock due to suboptimal router architecture or allocator choice). Despite the ease of use promised by IP generators like CONNECT, there can still exist a wide "knowledge gap" between "domain-experts" who develop the IP and "non-domain-experts" who use the IP. This gap is becoming evident in general as IPs encapsulate greater complexity and support higher degrees of detailed parameterizations. This observation was the original inspiration to start work on the Pandora IP development paradigm to help close this knowledge gap.

### 2.7 Related Work

The rapid growth in both research interest and commercial applications of Networks-on-Chip has led to the development of several NoC-related tools and frameworks. In particular, academic and research-oriented efforts have yielded a variety of NoC-related public releases over the past few years. The Stanford Open-Source Router RTL [98] provides a flexible state-of-the-art Virtual-Channel router implementation in synthesizable Verilog. Netmaker [92] consists of a library of various synthesizable NoC components, along with supporting material and scripts to run simulations under different traffic patterns. Atlas [88] is a mesh and torus NoC generation and evaluation framework. Bluetiles and Bluetree, both part of Blueshell [91], are mesh and tree NoC implementations in Bluespec System Verilog for connecting processor cores to each other and with memory. NoCBench [37] provides a set of hardware and software models and tools to help evaluate NoC designs. Finally, the FPGA NoC Designer tool [73] offers implementation estimates for hard and soft NoCs targeting FPGA devices.

In the commercial space, several companies offer interconnect solutions, which however are typically not publicly available for academic or research use. This includes SoC-oriented solutions, such as the Spidergon STNoC, Arteris' FlexNoC, ARM's AMBA, Sonics' NoCs products, as well as interconnect architectures that are commonly also used in FPGA environments, such as ARM's AXI, found in modern Xilinx FPGAs, or Altera's Qsys. Academic and research solutions, such as the ones mentioned above, or CONNECT, which is presented in this article, can often synergistically coexist with commercial interconnects to cover the diverse communication needs of FPGA-based research and emerging SoCs.

# **Chapter 3**

# **The Pandora IP Development Paradigm**

This chapter describes the key ideas and principles of the Pandora IP development paradigm that aims at reining in the growing complexity of modern highly-parameterized IP generators. To achieve this goal, in Pandora, IP blocks not only capture the microarchitectural and structural view of a design but also encapsulate additional dimensions of knowledge that the IP author has to offer, which can come in the form of: (1) detailed IP design space characterization to help the user understand the effects of parameter choices with respect to hardware implementation and IP-specific metrics, (2) application-level goal-oriented parameterization that is meaningful to the IP user and automatically sets low-level structural parameters to achieve the desired design optimizations, and (3) purpose-built domain-aware simulation-time and run-time monitoring mechanisms to assist functional and performance debugging. In addition to reducing complexity and boosting productivity, the Pandora approach also dramatically reduces the combined total effort, because work that would potentially otherwise be repeated by each IP user, is now only performed once and can be leveraged by others.

Pandora marks a departure from the current status quo in hardware design by combining a set

of key ideas and principles that aim at empowering both IP developers and users. In addition to encompassing the low-level crude hardware description of a design, the IP is enriched with domainexpert knowledge and includes supporting mechanisms, tools, and a diverse set of interface layers to match the expertise of the IP user. Combined, these features give the IP a sense of "smartness" or "self awareness" that enhance how the user interacts with it and can simplify and accelerate the integration, tuning, and validation phases of the design cycle.

The rest of this chapter is organized as follows. Section 3.1 provides background on the rise of hardware design complexity and motivates the need for Pandora. Section 3.2 describes the salient ideas and principles underlying Pandora. Section 3.3 touches on existing efforts that, like Pandora, also try to tackle various aspects of the hardware design complexity problem. Section 3.4 introduces and gives an overview of projects described later in this thesis that demonstrate the Pandora principles. While this chapter presents Pandora at the conceptual level and focuses on the broader guidelines underlying Pandora, Chapters 4, 5, and 6 present more tangible research artifacts that embody the principles described in this chapter and demonstrate key aspects of the Pandora IP development paradigm.

# 3.1 Background: The Rise of Design Complexity

Over the last few decades technology scaling has closely tracked Moore's Law [74], which refers to the empirical observation that the number of transistors in a chip doubles approximately every 18 months. This exponential growth in transistor counts, which has surprisingly persisted until today, along with Dennard scaling [36], which predicted that power density remains constant as transistors get smaller, have served as major drivers in the semiconductor industry for multiple decades. As a result, by the 1990s integrated circuits already contained tens of millions of transistors while power consumption still remained a second-order concern.

The Productivity Gap. As chip density continued its exponential growth, hardware designers struggled to keep up. This discrepancy between the number of transistors available on a single chip and the ability of designers to efficiently use these transistors was identified about fifteen years ago and was labeled the "design productivity gap", which is illustrated in Figure 1.2 of Chapter 1. This worrying trend sparked research in multiple aspects of hardware design, including high-level synthesis techniques [44, 65], validation tools, more powerful hardware description languages [20, 102] and frameworks [95] that enable the development of flexible IP generators and new hardware design methodologies, such as platform-based design [53].

In particular, the increased (re)use of Intellectual Property (IP) blocks, which refer to premade, pre-validated, reusable packaged units of hardware, has been recognized as a very promising approach to alleviate the productivity gap. Instead of designing every component in a chip from scratch, designers can build entire chips or portions thereof by leveraging third-party prepackaged IP blocks, which can greatly reduce the development time and cost of individual submodules within a larger chip. Compared to other approaches trying to tackle the growing productivity concerns, IP reuse faired as a simpler, more tangible and immediate solution, that can be quickly adopted by the semiconductor industry, because it does not require significant changes to the design process. Sure enough, the proliferation of an ever-growing number of rich IP catalogs came as a much-needed productivity boost that would bridge the productivity gap to some extent through modular design and heavy IP reuse.

The Power-Constrained Era. Since this design productivity gap was identified in the 1990s, transistor counts have continued to rapidly increase driven both by Moore's Law, as well as recent technological advances in Integrated Circuit (IC) fabrication, such as the use of silicon interposers or other forms of 3D stacking technologies. However, the inability to further scale supply voltage (due to leakage concerns) has led to the breakdown of classical CMOS scaling as described

by Dennard [36]. This, in turn, has cast power dissipation as a first-order concern in hardware design affecting all facets of computing, from embedded systems and smart phones to datacenter servers or even high-performance computing. In an effort to continue increasing performance in the power-constrained setting of the post-Dennard era, designers are turning to increased use of application-specific special-purpose hardware. Hardware specialization is a promising path towards more energy-efficient computing because it can lower the energy required to perform a task.

The confluence of these trends—namely the ever-growing availability of transistors, which are now in the billions, and the increased need for power-efficient special-purpose hardware within a chip—is leading to the development of massive chips, that include tens or hundreds of interacting modules, organized in intricate multi-level hierarchies. Yet, despite the clear power efficiency benefits of special-purpose hardware and our ability to fabricate denser chips with billions of transistors, current design methodologies have not evolved at the same pace to handle the complexity associated with such massive, diverse designs. As a result, designing a chip today requires large skilled hardware design teams and costs more than ever, even without considering manufacturing costs.

The IP Complexity Wall. Despite an enormous rise in scale, complexity, and specialization, the way IP blocks are developed and used has not fundamentally changed since the introduction of modern Hardware Description Languages (HDLs) and the proliferation of ASIC-based design flows more than two decades ago. The result is a "complexity explosion" as designers build chips as "fragile" collections of complex IP blocks, each with its own set of cryptic (for the non-domain-expert) low-level knobs, which can often be traced back to a crude hardware schematic or specification document. Today, we are facing a new encounter with the "design productivity gap" at a different scale—not at the level of the transistor, but instead at the level of the IP block. Current hardware design methodologies are struggling to keep up with the complexity involved in config-

uring, tuning, integrating, and validating the multiple interacting IP blocks within a modern chip. Consequently, the complexity and the associated development time, cost, and manpower required to build a chip today continue to increase prohibitively.

# **3.2 Pandora Principles**

The overarching goal of this work is to tackle the problem of increasing complexity in hardware design and make "reusable" IPs more "usable" through the Pandora IP development paradigm. To achieve this goal, Pandora raises the level of abstraction to allow non-domain-experts to easily and efficiently navigate and identify sweet spots within the design space, and use and debug highly parameterized IPs, without having to deal with the low-level and often cryptic details of modern IP design. The rest of this section delves into the salient principles of Pandora, which all share the common goal of overcoming the "Complexity Wall" in hardware design.

#### 3.2.1 Detailed IP Characterization

In addition to capturing the microarchitectural and structural view of a design, Pandora IPs also carry qualitative and quantitative meta-data. This information captures how the various knobs and parameter settings affect the IP design space with respect to hardware implementation and higherlevel domain-specific properties and performance characteristics. This embedded knowledge provides the foundations for a Pandora IP to provide an elevated design abstraction and supporting functionalities for the IP users.

Hardware Implementation Characterization. This refers to capturing how the IP parameters affect implementation characteristics of the design, such as area, critical path, and power dissipation. In its simplest form this can be a database or characterization library that is attached to and maintained along with the IP. Alternatively, this can also be complemented or take the form of predictive tools or analytical formulas that approximate implementation trends, such as DELPHI, presented in Chapter 4. Implementation information can be maintained at different degrees of fidelity, ranging from classes of hardware devices (e.g., FPGAs or ASICs), specific device families (e.g., Altera Stratix V), or instances (e.g., Virtex-6 XC6VLX760), or technology libraries (e.g., TSMC 32nm). Moreover, additional information can be maintained depending on the specific IP and implementation target. For instance, in an FPGA environment, area can be broken down into LookUp Tables (LUTs), BlockRAMs, DSPs, etc., or similarly in a design with multiple clock domains, critical path information can be kept on a per-clock basis.

**Domain-Specific Metrics and Properties.** Besides hardware implementation details, which are typically common across all different types of IP, Pandora also argues for capturing how the various IP parameters affect higher-level metrics that are specific to the domain at hand. These are also typically the metrics that the IP end-users are interested in and try to adjust to meet application-specific goals. For instance, in the case of a processor core, such a metric could be IPC (Instructions Per Cycle), or in the case of a NoC IP, such metrics could be the saturation bandwidth and idle latency of the network. This characterization can also include high-level properties, e.g., in the case of a NoC IP, capture how IP parameters affect packet delivery and ordering guarantees, traffic isolation or Quality-of-Service properties.

These characterization libraries are meant to aid the design process and do not necessarily need to be exhaustive or perfectly accurate. As we show in Chapter 5 with Nautilus, exploring even a small subset of the design space is often sufficient to vastly accelerate the IP design space search and optimization process. Depending on the degree of parameterization and complexity of the IP, the characterization of the IP design space can be done in many ways and varying degrees of detail: e.g., (1) collectively for the entire IP (i.e., sweeping over externally-exposed parameters), (2) per submodule (i.e., considering the internal parameters of each submodule in the hierarchy), (3) through selective sampling of the design space (driven by domain-expert knowledge), or (4) through the derivation of analytical formulas that predict implementation and performance results based on expert knowledge or experience.

Even in its raw form, whether it is detailed characterization libraries based on experimental data (e.g., synthesis runs or simulations) or coarser grain predictive data based on analytical formulas and designer experience, this extra knowledge that is coupled with the IP is already very useful to the IP user. Not only does it facilitate faster and more informed navigation of the design space, but can also help drastically prune the design space by identifying parameter combinations that do not constitute interesting or feasible design points. To demonstrate this aspect of Pandora, the CONNECT Network-on-Chip generator has been extended as part of this thesis to provide FPGA and ASIC estimates through the DELPHI framework, which is described in Chapter 4.

#### 3.2.2 Automated IP Optimization