## Redesigning Database Systems in Light of CPU Cache Prefetching

#### Shimin Chen

CMU-CS-05-192

December 2005

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

#### Thesis Committee:

Anastassia Ailamaki, Co-Chair Todd C. Mowry, Co-Chair Christos Faloutsos Phillip B. Gibbons David J. DeWitt, University of Wisconsin at Madison

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

#### Copyright © 2005 Shimin Chen

This research was sponsored by the National Science Foundation (NSF) under grant nos. CCR-0205544 and CCR-0085938, the National Aeronautics and Space Administration (NASA) under grant no. NAG2-1230, and the Microsoft Corporation through a generous fellowship. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

**Keywords:** Cache Prefetching, Database Systems, CPU Cache Performance, Data Locality Optimizations, B<sup>+</sup>-Trees, Hash Joins.

To my parents Guanhu and Aili, my wife Qin, and my daughter Ada.

## Abstract

Computer systems have enjoyed an exponential growth in processor speed for the past 20 years, while main memory speed has improved only moderately. Today a cache miss to main memory takes hundreds of processor cycles. Recent studies have demonstrated that on commercial databases, about 50% or more of execution time in memory is often wasted due to cache misses. In light of this problem, a number of recent studies focused on reducing the *number* of cache misses of database algorithms. In this thesis, we investigate a different approach: reducing the *impact* of cache misses through a technique called *cache prefetching*. Since prefetching for sequential array accesses has been well studied, we are interested in studying non-contiguous access patterns found in two classes of database algorithms: the B<sup>+</sup>-Tree index algorithm and the hash join algorithm. We re-examine their designs with cache prefetching in mind, and combine prefetching and data locality optimizations to achieve good cache performance.

For B<sup>+</sup>-Trees, we first propose and evaluate a novel main memory index structure, Prefetching B<sup>+</sup>-Trees, which uses prefetching to accelerate two major access patterns of B<sup>+</sup>-Tree indices: searches and range scans. We then apply our findings in the development of a novel index structure, Fractal Prefetching B<sup>+</sup>-Trees, that optimizes index operations both for CPU cache performance and for disk performance in commercial database systems by intelligently embedding cache-optimized trees into disk pages.

For hash joins, we first exploit cache prefetching separately for the I/O partition phase and the join phase of the algorithm. We propose and evaluate two techniques, Group Prefetching and Software-Pipelined Prefetching, that exploit inter-tuple parallelism to overlap cache misses across the processing of multiple tuples. Then we present a novel algorithm, Inspector Joins, that exploits the free information obtained from one pass of the hash join algorithm to improve the performance of a later pass. This new algorithm addresses the memory bandwidth sharing problem in shared-bus multiprocessor systems.

We compare our techniques against state-of-the-art cache-friendly algorithms for  $B^+$ -Trees and hash joins through both simulation studies and real machine experiments. Our experimental results demonstrate dramatic performance benefits of our cache prefetching enabled techniques.

## Acknowledgments

I must thank my advisors, Todd Mowry and Anastassia Ailamaki, for the tremendous time, energy, and wisdom they invested in my Ph.D. education. Todd and Natassa taught me everything from choosing research topics, to performing high-quality studies, to writing papers and giving talks. Their guidance and support throughout the years are invaluable.

I am indebted to Phillip Gibbons for collaborating on my entire thesis research, for participating in our weekly discussions, and for contributing his knowledge, sharpness, and efforts to all the four publications that form the basis of this thesis.

I would like to thank the other members of my Ph.D. thesis committee, David DeWitt and Christos Faloutsos, for their thoughtful comments and invaluable suggestions that have improved the quality of the experimental results and the completeness of this thesis.

I thank Gary Valentin for collaborating on the  $fpB^+$ -Tree paper. Gary implemented jump pointer array prefetching in IBM DB2 and collected DB2 results on  $B^+$ -Tree range scan I/O performance for the paper. I am grateful to Bruce Lindsay for giving a CMU DB Seminar talk on the DB2 hash join implementation, which inspired my hash join work. My thesis work also benefitted from insightful discussions with David Lomet and Per-Åke Larson.

I would like to acknowledge Angela Brown, Kun Gao, John Griffin, Stratos Papadomanolakis, Jiri Schindler, Steve Schlosser, and Minglong Shao, for helping me set up machines for running real-machine experiments in my publications and in this thesis; Chris Colohan and Gregory Steffan, for helping me understand the internals of the "cello" simulator for my simulation studies; members of the CMU database group and STAMPede group, for giving comments on my practice talks; staff of CMU SCS facilities,

for allowing me to reboot machines in the machine room after working hours; and Sharon Burks, for her administrative helps in arranging my thesis proposal and defense talks.

My summer internships expanded my research experience. I would like to thank David Lomet and Phillip Gibbons for mentoring me during my internships. I also want to thank all the people in IBM Toronto Lab, Microsoft Research Redmond, and Intel Research Pittsburgh, for making my summers productive and enjoyable.

I thank my friends in Pittsburgh, Toronto, and Seattle for their helps in my CMU graduate life and in my summer internships, and for adding a lot of funs to my life.

Finally, I must express my deepest gratitude to my family. I owe a great deal to my parents, Guanhu and Aili, who gave a life, endless love, and persistent encouragement to me. My sister, Yan, and brotherin-law, Gang, are always helping and supportive. I am deeply indebted to my dear wife, Qin, for sharing every moment of the CMU graduate life with me. Without her love, patience, encouragement, and support, it is impossible for me to complete this six and half years of long journey. Last but not least, my one-year-old daughter, Ada, motivated me to finish my thesis with her sweet voice of "baba".

# Contents

| Ał | ostrac              | et            |                                                                         | V   |  |

|----|---------------------|---------------|-------------------------------------------------------------------------|-----|--|

| Ac | Acknowledgments vii |               |                                                                         |     |  |

| Co | ontent              | ts            |                                                                         | ix  |  |

| Li | st of I             | Figures       |                                                                         | XV  |  |

| Li | st of ]             | <b>Fables</b> |                                                                         | xxi |  |

| 1  | Intr                | oductio       | n                                                                       | 1   |  |

|    | 1.1                 | Can W         | e Simply Adapt Memory-to-Disk Techniques?                               | 2   |  |

|    | 1.2                 | Cache         | Optimization Strategies                                                 | 5   |  |

|    |                     | 1.2.1         | Reducing the <i>Number</i> of Cache Misses                              | 5   |  |

|    |                     | 1.2.2         | Reducing the Impact of Cache Misses                                     | 6   |  |

|    | 1.3                 | Our Aj        | oproach: Redesigning Database Systems in Light of CPU Cache Prefetching | 9   |  |

|    | 1.4                 | Relate        | d Work                                                                  | 10  |  |

|    |                     | 1.4.1         | Related Work on $B^+$ -Trees                                            | 11  |  |

|    |                     | 1.4.2         | Related Work on Hash Joins                                              | 12  |  |

|    | 1.5                 | Contri        | outions                                                                 | 13  |  |

|    | 1.6                 | Thesis        | Organization                                                            | 15  |  |

| 2  | Exp                 | loiting (     | Cache Prefetching for Main Memory B <sup>+</sup> -Trees                 | 17  |  |

| 2.1 | Introdu | ction                                                                                      | 17 |

|-----|---------|--------------------------------------------------------------------------------------------|----|

|     | 2.1.1   | Previous Work on Improving the Cache Performance of Indices                                | 18 |

|     | 2.1.2   | Our Approach: Prefetching B <sup>+</sup> -Trees                                            | 19 |

| 2.2 | Index S | Searches: Using Prefetching to Create Wider Nodes                                          | 20 |

|     | 2.2.1   | Modifications to the $B^+$ -Tree Algorithm                                                 | 22 |

|     | 2.2.2   | Qualitative Analysis                                                                       | 24 |

| 2.3 | Index S | Scans: Prefetching Ahead Using Jump-Pointer Arrays                                         | 27 |

|     | 2.3.1   | Solving the Pointer-Chasing Problem                                                        | 28 |

|     | 2.3.2   | Implementing Jump-Pointer Arrays to Support Efficient Updates                              | 30 |

|     | 2.3.3   | Prefetching Algorithm                                                                      | 32 |

|     | 2.3.4   | Qualitative Analysis                                                                       | 33 |

|     | 2.3.5   | Internal Jump-Pointer Arrays                                                               | 35 |

| 2.4 | Experi  | mental Results                                                                             | 36 |

|     | 2.4.1   | Itanium 2 Machine Configuration                                                            | 37 |

|     | 2.4.2   | Simulation Machine Model                                                                   | 39 |

|     | 2.4.3   | B <sup>+</sup> -Trees Studied and Implementation Details                                   | 41 |

|     | 2.4.4   | A Simple Cache Prefetching Experiment: Measuring Memory Bandwidth on the Itanium 2 Machine | 43 |

|     | 2.4.5   | Search Performance                                                                         | 45 |

|     | 2.4.6   | Range Scan Performance                                                                     | 53 |

|     | 2.4.7   | Update Performance                                                                         | 55 |

|     | 2.4.8   | Operations on Mature Trees                                                                 | 61 |

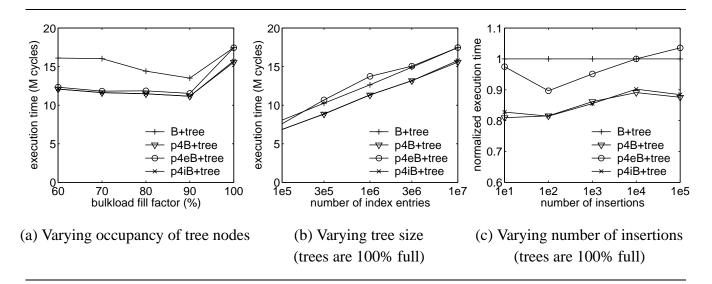

|     | 2.4.9   | Sensitivity Analysis                                                                       | 63 |

|     | 2.4.10  | Cache Performance Breakdowns                                                               | 64 |

|     | 2.4.11  | Impact of Larger Memory Latency                                                            | 66 |

| 2.5 | Discus  | sion and Related Work                                                                      | 67 |

| 2.6 | Chapte  | r Summary                                                                                  | 69 |

| 3 | Opt | imizing | Both Cache and Disk Performance for B <sup>+</sup> -Trees                            | 71  |

|---|-----|---------|--------------------------------------------------------------------------------------|-----|

|   | 3.1 | Introdu | uction                                                                               | 71  |

|   |     | 3.1.1   | Our Approach: Fractal Prefetching B <sup>+</sup> -Trees                              | 72  |

|   | 3.2 | Optim   | izing I/O Performance                                                                | 74  |

|   |     | 3.2.1   | Searches: Prefetching and Node Sizes                                                 | 75  |

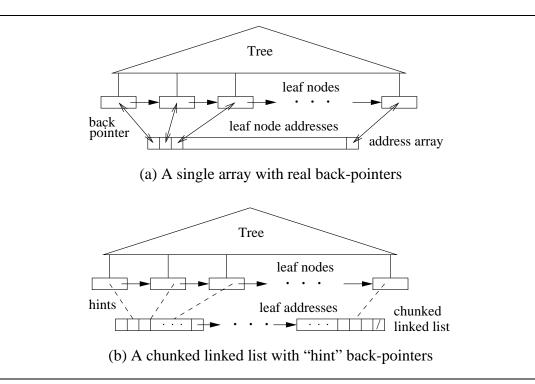

|   |     | 3.2.2   | Range Scans: Prefetching via Jump-Pointer Arrays                                     | 76  |

|   | 3.3 | Optim   | izing CPU Cache Performance                                                          | 77  |

|   |     | 3.3.1   | Why Traditional B <sup>+</sup> -Trees Suffer from Poor Cache Performance? $\ldots$ . | 77  |

|   |     | 3.3.2   | Previous Approach to Improving $B^+$ -Tree Cache Performance $\ldots \ldots \ldots$  | 80  |

|   |     | 3.3.3   | Disk-First fpB <sup>+</sup> -Trees                                                   | 81  |

|   |     | 3.3.4   | Cache-First fpB <sup>+</sup> -Trees                                                  | 85  |

|   |     | 3.3.5   | Improving Range Scan Cache Performance                                               | 88  |

|   | 3.4 | Cache   | Performance through Simulations                                                      | 89  |

|   |     | 3.4.1   | Experimental Setup                                                                   | 90  |

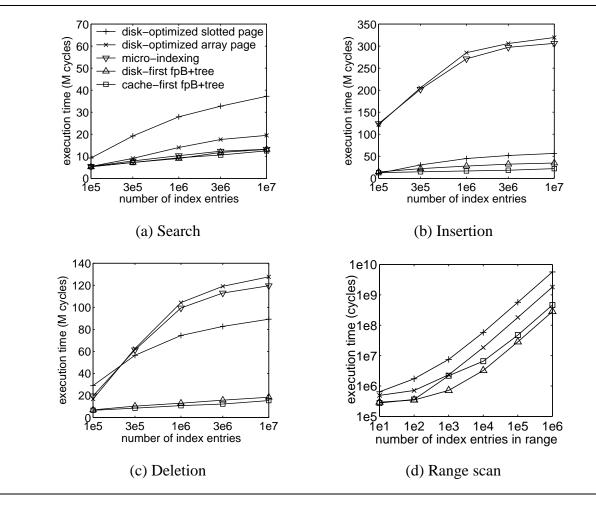

|   |     | 3.4.2   | Search Cache Performance through Simulations                                         | 92  |

|   |     | 3.4.3   | Insertion Cache Performance through Simulations                                      | 95  |

|   |     | 3.4.4   | Deletion Cache Performance through Simulations                                       | 97  |

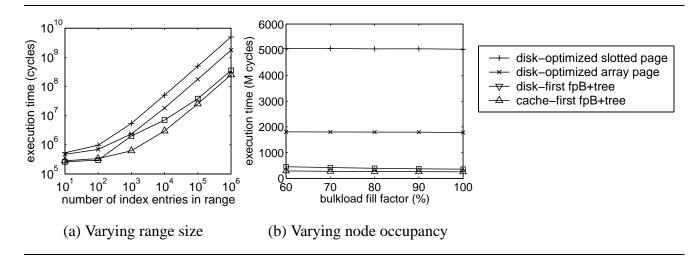

|   |     | 3.4.5   | Range Scan Cache Performance through Simulations                                     | 98  |

|   |     | 3.4.6   | Mature Tree Cache Performance                                                        | 99  |

|   |     | 3.4.7   | Results with Larger Key Size                                                         | 100 |

|   | 3.5 | Cache   | Performance on an Itanium 2 Machine                                                  | 101 |

|   |     | 3.5.1   | Experimental Setup                                                                   | 102 |

|   |     | 3.5.2   | Search Performance on Itanium 2                                                      | 104 |

|   |     | 3.5.3   | Insertion Performance on Itanium 2                                                   | 104 |

|   |     | 3.5.4   | Deletion Performance on Itanium 2                                                    | 106 |

|   |     | 3.5.5   | Range Scan Performance on Itanium 2                                                  | 106 |

|   |     | 3.5.6   | Operations on Mature Trees                                                           | 107 |

|   |     | 3.5.7   | Comparing Simulation and Itanium 2 Results                | . 108 |

|---|-----|---------|-----------------------------------------------------------|-------|

|   | 3.6 | I/O Pe  | rformance and Space Overhead                              | . 109 |

|   |     | 3.6.1   | Space Overhead                                            | . 109 |

|   |     | 3.6.2   | Search Disk Performance                                   | . 110 |

|   |     | 3.6.3   | Range Scan Disk Performance                               | . 111 |

|   |     | 3.6.4   | Range Scan Disk Performance on a Commercial DBMS          | . 114 |

|   | 3.7 | Relate  | d Work                                                    | . 115 |

|   | 3.8 | Discus  | ssion                                                     | . 116 |

|   | 3.9 | Chapte  | er Summary                                                | . 118 |

|   | Ŧ   | •       |                                                           | 110   |

| 4 | -   | U       | Hash Join Performance through Prefetching                 | 119   |

|   | 4.1 | Introdu | uction                                                    | . 119 |

|   |     | 4.1.1   | Hash Joins Suffer from CPU Cache Stalls                   | . 120 |

|   |     | 4.1.2   | Our Approach: Cache Prefetching                           | . 121 |

|   | 4.2 | Relate  | d Work                                                    | . 123 |

|   | 4.3 | Depen   | dencies in the Join Phase                                 | . 124 |

|   | 4.4 | Group   | Prefetching                                               | . 125 |

|   |     | 4.4.1   | Group Prefetching for a Simplified Probing Algorithm      | . 126 |

|   |     | 4.4.2   | Understanding Group Prefetching                           | . 126 |

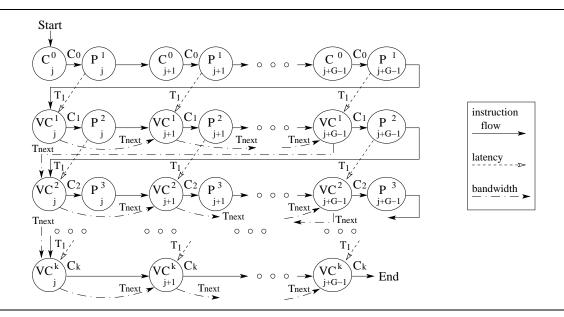

|   |     | 4.4.3   | Critical Path Analysis for Group Prefetching              | . 129 |

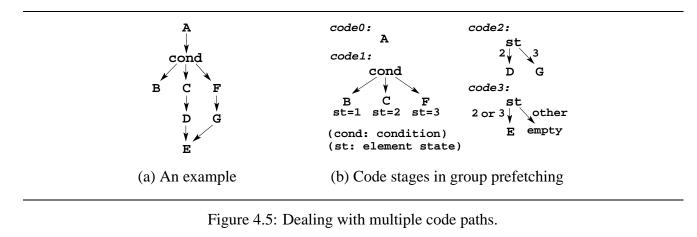

|   |     | 4.4.4   | Dealing with Complexities                                 | . 132 |

|   | 4.5 | Softwa  | are-Pipelined Prefetching                                 | . 134 |

|   |     | 4.5.1   | Understanding Software-pipelined Prefetching              | . 135 |

|   |     | 4.5.2   | Critical Path Analysis for Software-pipelined Prefetching | . 136 |

|   |     | 4.5.3   | Dealing with Complexities                                 | . 137 |

|   |     | 4.5.4   | Group vs. Software-pipelined Prefetching                  | . 138 |

|   | 4.6 | Prefeto | ching for the Partition Phase                             | . 138 |

|   | 4.7 | Experi  | mental Results                                            | . 139 |

|   |      | 4.7.1   | Experimental Setup                                      |

|---|------|---------|---------------------------------------------------------|

|   |      | 4.7.2   | Is Hash Join I/O-Bound or CPU-Bound?                    |

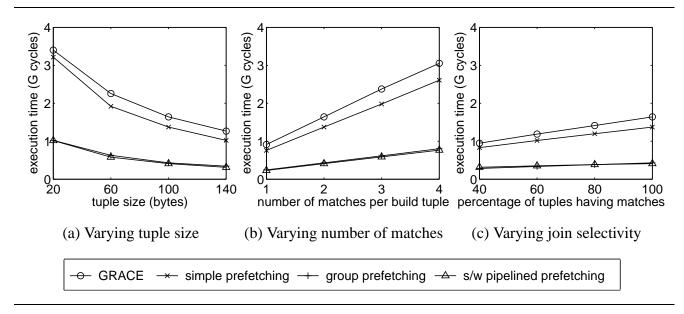

|   |      | 4.7.3   | Join Phase Performance through Simulations              |

|   |      | 4.7.4   | Partition Phase Performance through Simulations         |

|   |      | 4.7.5   | Comparison with Cache Partitioning                      |

|   |      | 4.7.6   | User Mode CPU Cache Performance on an Itanium 2 Machine |

|   |      | 4.7.7   | Execution Times on the Itanium 2 Machine with Disk I/Os |

|   | 4.8  | Chapte  | er Summary                                              |

| 5 | Insp | ector J | oins 161                                                |

|   | 5.1  | Introdu | uction                                                  |

|   |      | 5.1.1   | Previous Cache-Friendly Approaches                      |

|   |      | 5.1.2   | The Inspector Join Approach                             |

|   | 5.2  | Relate  | d Work                                                  |

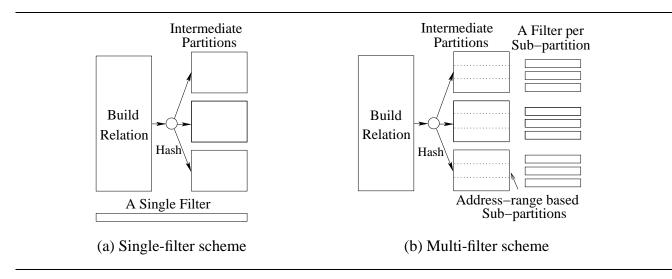

|   | 5.3  | Inspec  | tor Joins: Overview                                     |

|   |      | 5.3.1   | Inspecting the Data: Multi-Filters                      |

|   |      | 5.3.2   | Improving Locality for Stationary Tuples                |

|   |      | 5.3.3   | Exploiting Cache Prefetching                            |

|   |      | 5.3.4   | Choosing the Best Join Phase Algorithm                  |

|   | 5.4  | I/O Pa  | rtition and Inspection Phase                            |

|   |      | 5.4.1   | Bloom Filters: Background                               |

|   |      | 5.4.2   | Memory Space Requirement                                |

|   |      | 5.4.3   | Minimizing the Number of Cache Misses                   |

|   |      | 5.4.4   | Partition and Inspection Phase Algorithm                |

|   | 5.5  | Cache   | -Stationary Join Phase                                  |

|   |      | 5.5.1   | Counting Sort                                           |

|   |      | 5.5.2   | Exploiting Prefetching in the Join Step                 |

|   | 5.6  | Experi  | mental Results                                          |

| Bi | bliography 197 |          |                                        |       |

|----|----------------|----------|----------------------------------------|-------|

| 6  | Con            | clusions |                                        | 193   |

|    | 5.7            | Chapte   | r Summary                              | . 191 |

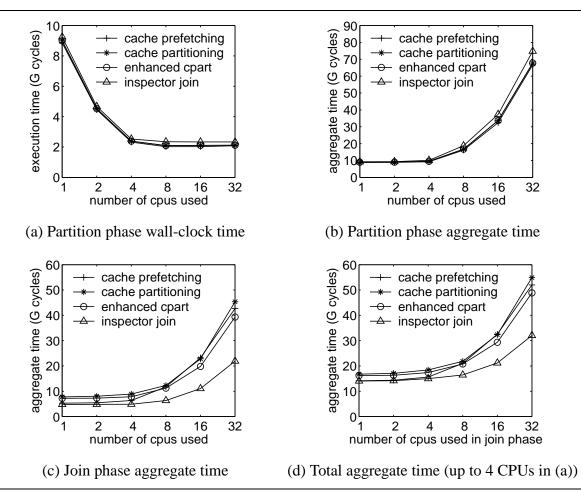

|    |                | 5.6.5    | Choosing the Best Join Phase Algorithm | . 190 |

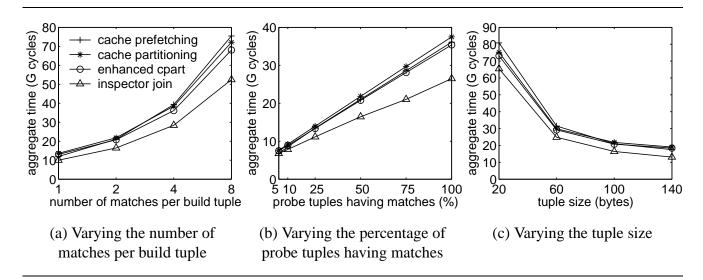

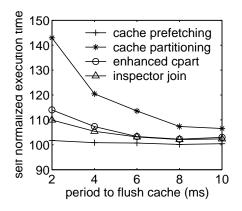

|    |                | 5.6.4    | Robustness of the Algorithms           | . 189 |

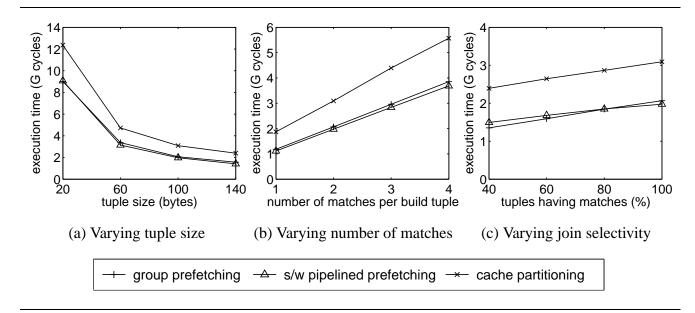

|    |                | 5.6.3    | Varying Other Parameters               | . 187 |

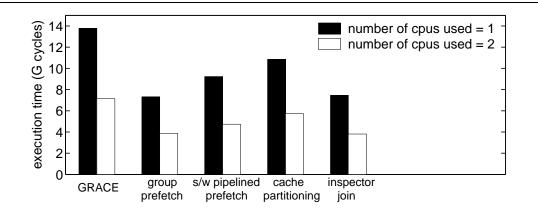

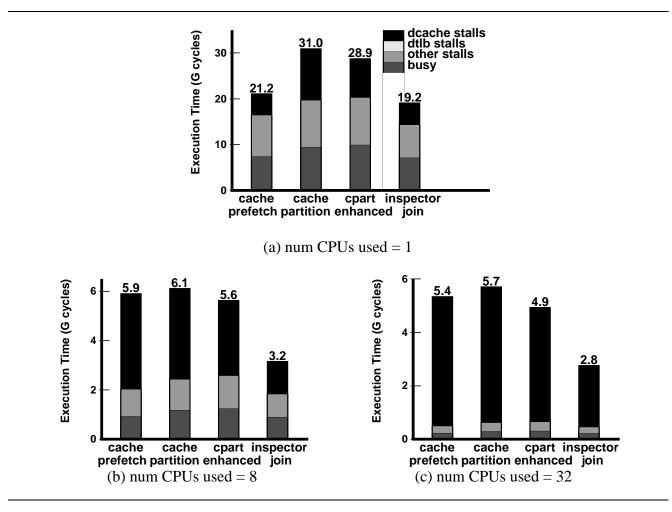

|    |                | 5.6.2    | Varying the Number of CPUs             | . 184 |

|    |                | 5.6.1    | Experimental Setup                     | . 181 |

# **List of Figures**

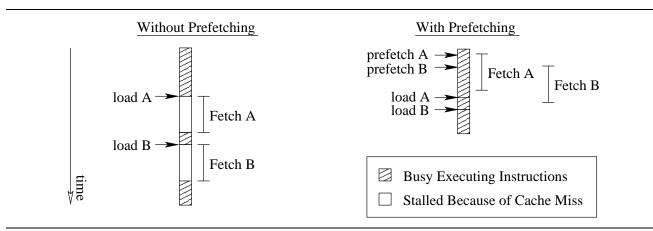

| 1.1  | Illustration of the use of prefetch instructions to hide cache miss latencies                                                                                                         | 7  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

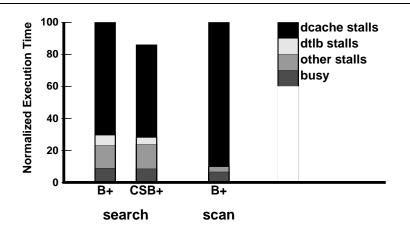

| 2.1  | Execution time breakdown for index operations ( $\mathbf{B}$ + = $\mathbf{B}^+$ -Trees, $\mathbf{CSB}$ + = $\mathbf{CSB}^+$ -Trees).                                                  | 18 |

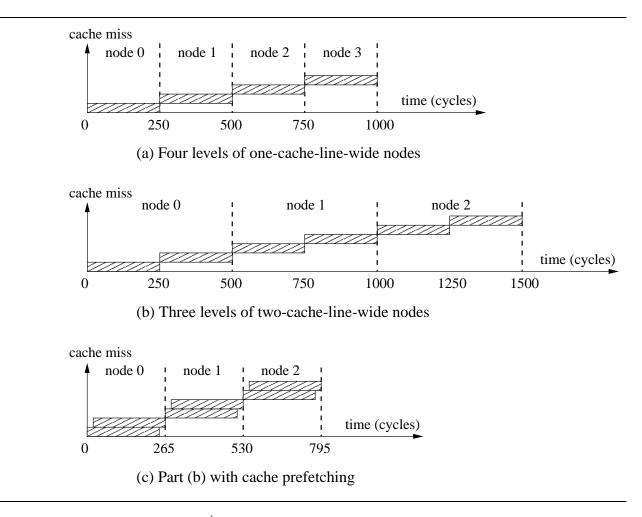

| 2.2  | Performance of various $B^+$ -Tree searches where a cache miss to memory takes 250 cycles, and a subsequent access can begin 15 cycles later (assuming no TLB misses for simplicity). | 21 |

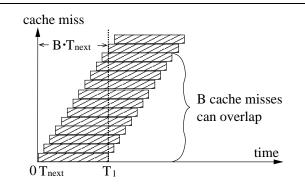

| 2.3  | Computing the number of cache misses that can be served in parallel in the memory                                                                                                     |    |

|      | system                                                                                                                                                                                | 25 |

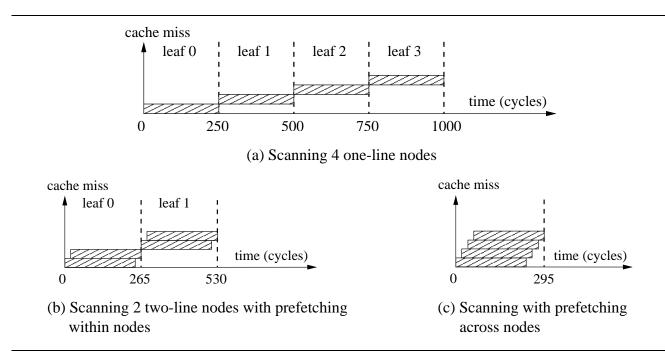

| 2.4  | Cache behaviors of index range scans (assuming no TLB misses for simplicity)                                                                                                          | 28 |

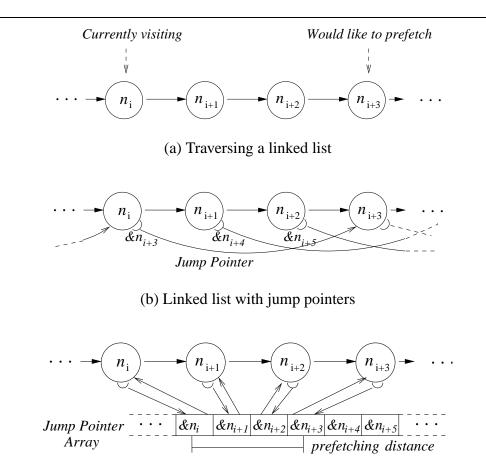

| 2.5  | Addressing the pointer-chasing problem                                                                                                                                                | 29 |

| 2.6  | External jump-pointer arrays.                                                                                                                                                         | 31 |

| 2.7  | Internal jump-pointer arrays.                                                                                                                                                         | 35 |

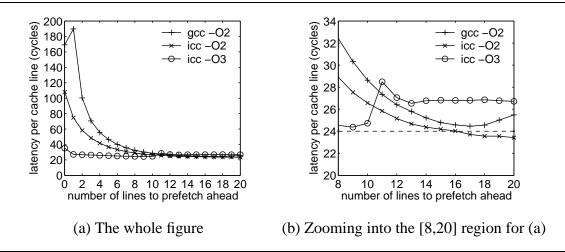

| 2.8  | Measuring the latency of loading an additional independent cache line $(T_{next})$ on the Itanium 2 machine by using cache prefetching.                                               | 43 |

| 2.9  | Optimal performance of the B <sup>+</sup> -Tree and the $p^wB^+$ -Tree ( $w = 1,, 20$ ) on Itanium 2 while compiled with different compilers and optimization flags.                  | 45 |

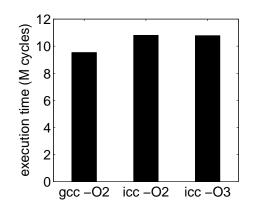

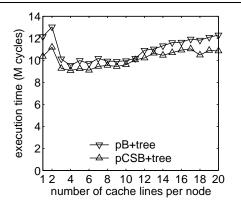

| 2.10 | Determining the optimal node size on the Itanium 2 machine (one-cache-line points correspond to the $B^+$ -Tree and the $CSB^+$ -Tree)                                                | 46 |

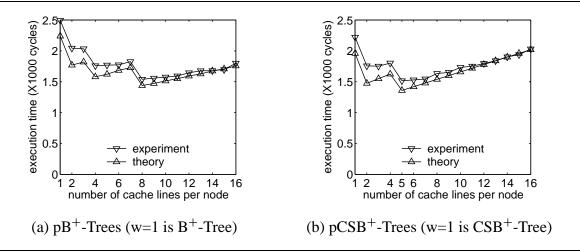

| 2.11 | Comparing experimental results through simulations with theoretical costs for cold searches in trees bulkloaded 100% full with 10 million keys.                                       | 47 |

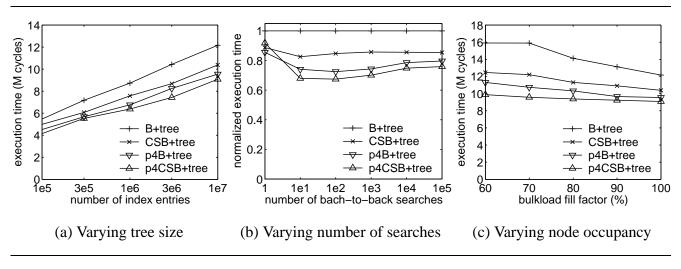

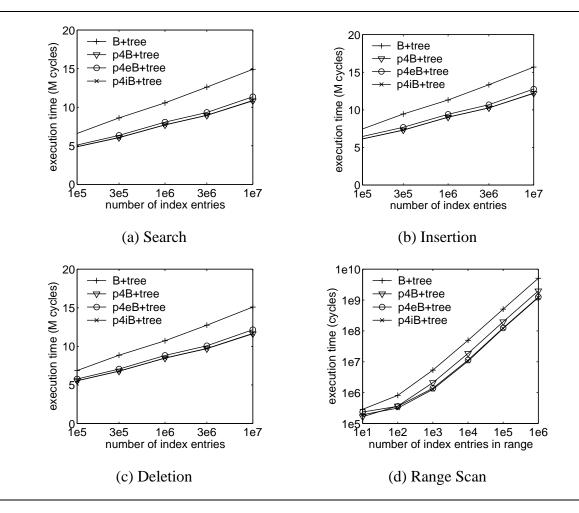

| 2.12 | Search performance on Itanium 2 (warm cache)                                                                                                                                          | 48 |

| 2.13 | Search performance through simulations.                                                                                                                                               | 49 |

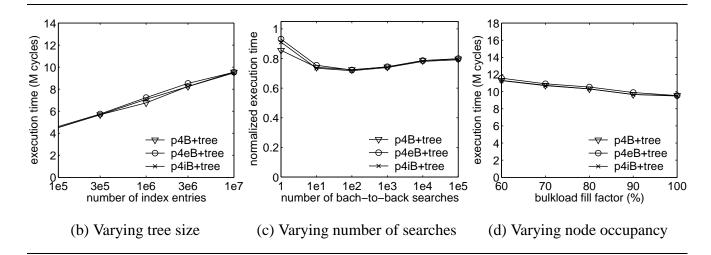

| 2.14 | Comparing the search performance of $p^4B^+$ -Trees, $p_e^4B^+$ -Trees, and $p_i^4B^+$ -Trees on the Itanium 2 machine.                                                              | 51 |

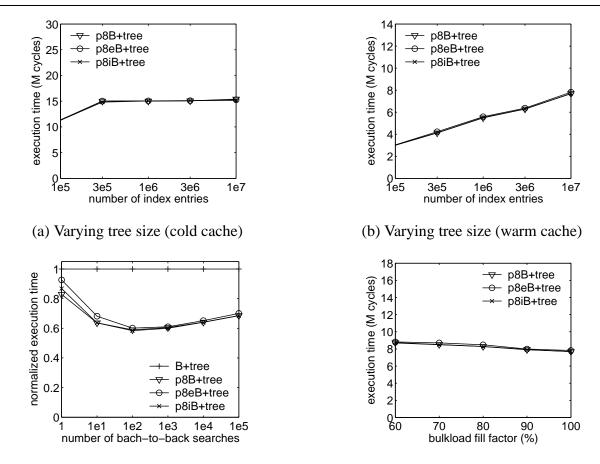

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.15 | Comparing the search performance of $p^8B^+$ -Trees, $p_e^8B^+$ -Trees, and $p_i^8B^+$ -Trees on the simulation platform.                                                            | 52 |

| 2.16 | Range scan performance on the Itanium 2 machine.                                                                                                                                     | 53 |

| 2.17 | Range scan performance through simulations.                                                                                                                                          | 54 |

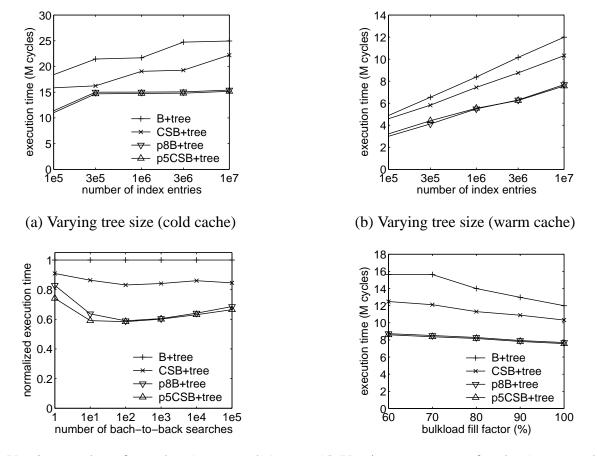

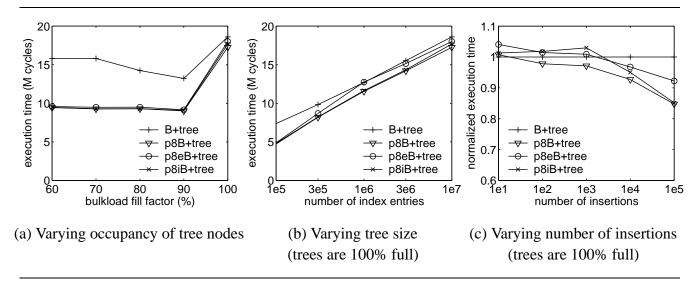

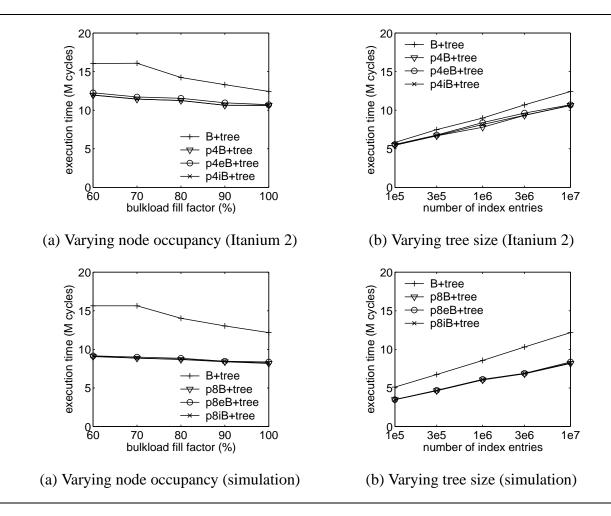

| 2.18 | Insertion performance on the Itanium 2 machine (warm cache)                                                                                                                          | 56 |

| 2.19 | Insertion performance through simulations (warm cache)                                                                                                                               | 56 |

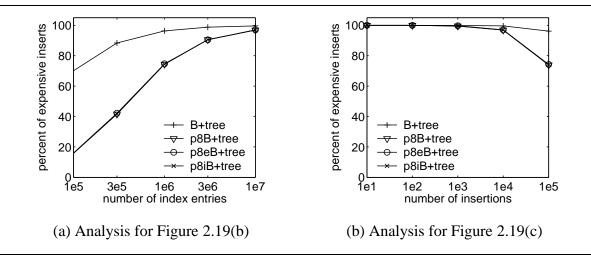

| 2.20 | Analyzing percentage of insertions causing node splits to understand the performance of inserting into 100% full trees.                                                              | 58 |

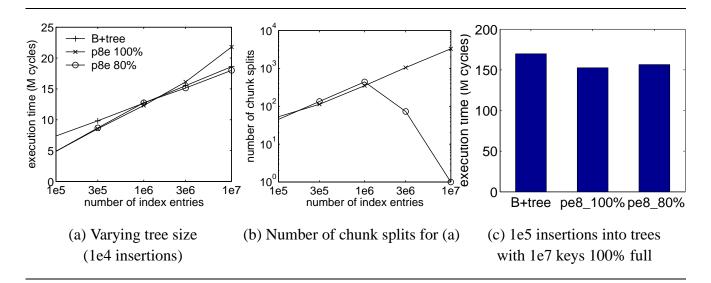

| 2.21 | Insertions to $p_e^8 B^+$ -Trees with 80% full chunks and 100% full chunks (warm cache)                                                                                              | 58 |

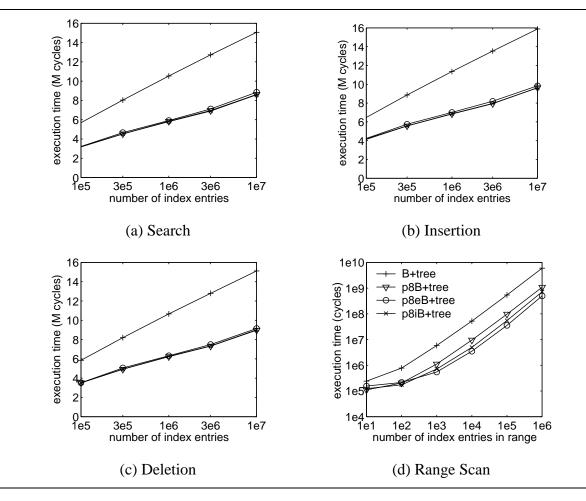

| 2.22 | Deletion performance on the Itanium 2 machine and through simulations (warm cache)                                                                                                   | 60 |

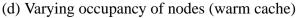

| 2.23 | Operations on mature trees on the Itanium 2 machine (warm cache)                                                                                                                     | 61 |

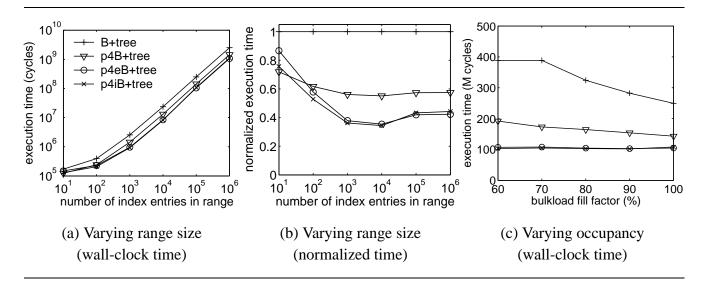

| 2.24 | Operations on mature trees through simulations (warm cache).                                                                                                                         | 62 |

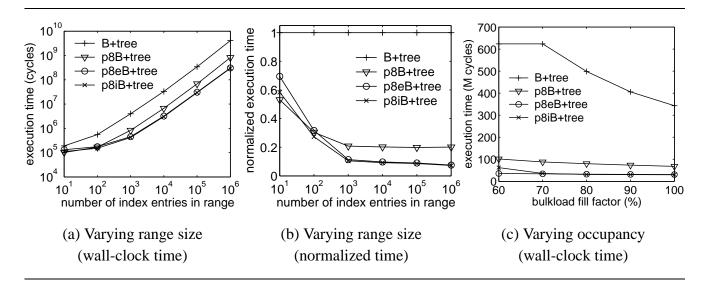

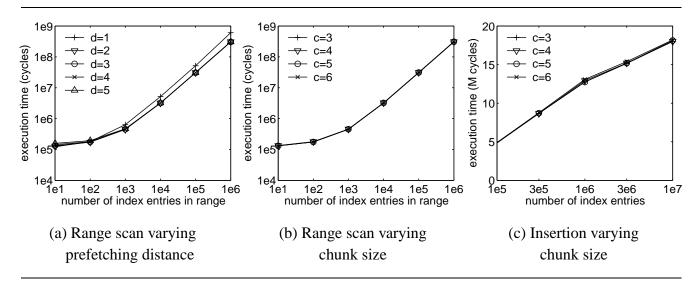

| 2.25 | Sensitivity analysis.                                                                                                                                                                | 63 |

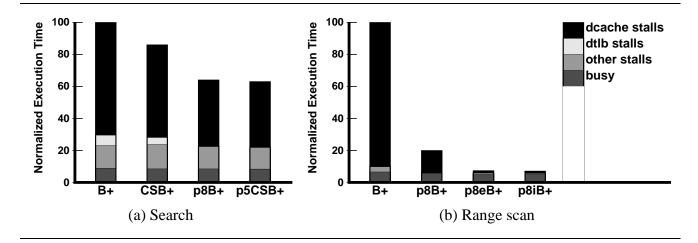

| 2.26 | Impact of various $\ensuremath{pB^+}\xspace$ -Trees on the cache performance of index search and range scan                                                                          | 65 |

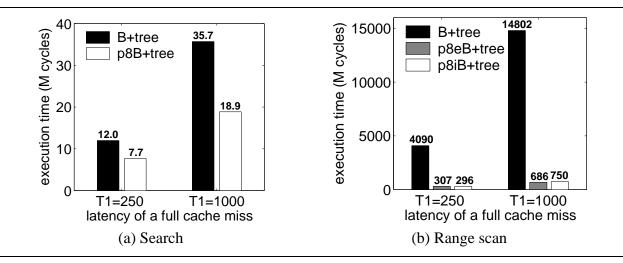

| 2.27 | Impact of increased memory latency on the performance of index search and range scan.                                                                                                | 66 |

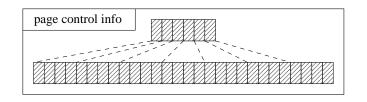

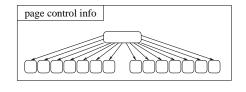

| 3.1  | Self-similar "tree within a tree" structure.                                                                                                                                         | 72 |

| 3.2  | Internal jump-pointer array.                                                                                                                                                         | 76 |

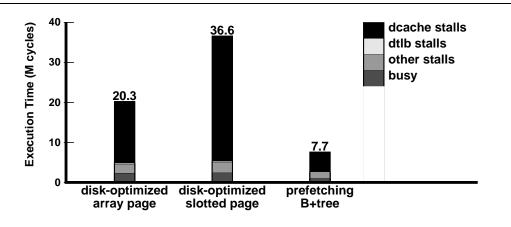

| 3.3  | Disk-Optimized $B^+$ -Tree page organizations. (An index entry is a pair of key and tu-<br>pleID for leaf pages, and a pair of key and pageID for non-leaf pages.)                   | 78 |

| 3.4  | Comparing search cache performance of disk-optimized $B^+$ -Trees with index entry arrays, disk-optimized $B^+$ -Trees with slotted pages, and prefetching $B^+$ -Trees (with eight- |    |

|      | line-wide nodes).                                                                                                                                                                    | 79 |

| 3.5  | Illustration of micro-indexing.                                                                                                                                                      | 80 |

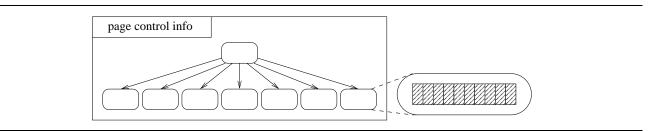

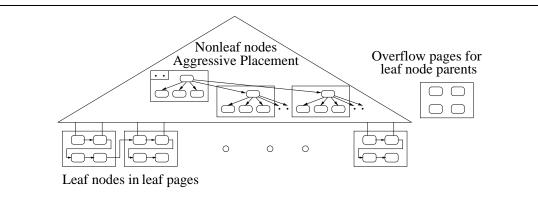

| 3.6  | Disk-First fp $B^+$ -Tree: a cache-optimized tree inside each page                                                                                                                   | 81 |

| 3.7  | The node size mismatch problem.                                                                                                                                                      | 82 |

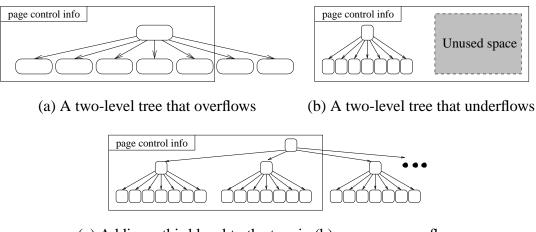

| 3.8  | Fitting cache-optimized trees in a page.                                                                                                                                             | 83 |

| 3.9  | Cache-First fpB <sup>+</sup> -Tree design                                                                                                                                                                 |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

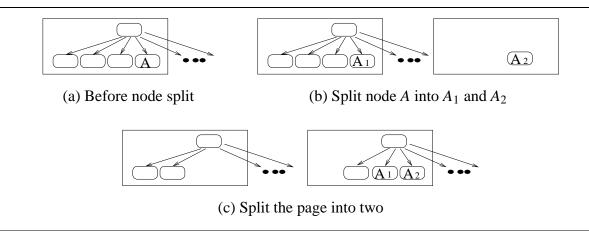

| 3.10 | Non-leaf node splits                                                                                                                                                                                      |

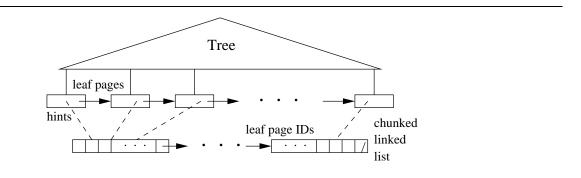

| 3.11 | External jump-pointer array                                                                                                                                                                               |

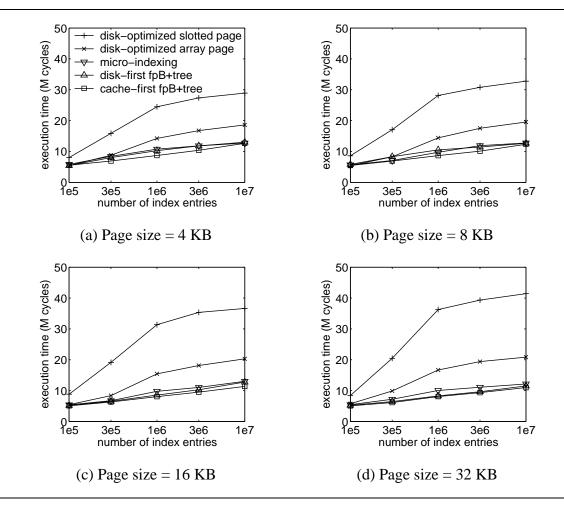

| 3.12 | 10,000 random searches in trees that are 100% full                                                                                                                                                        |

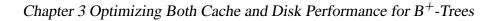

| 3.13 | Optimal width selection when page size is 16 KB. (" <b>min</b> ": the width achieving the minimal execution time; " <b>opt</b> ": the selected optimal width given the optimal criterion.) . 94           |

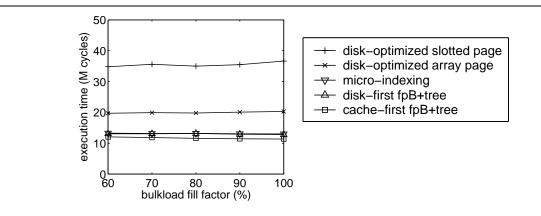

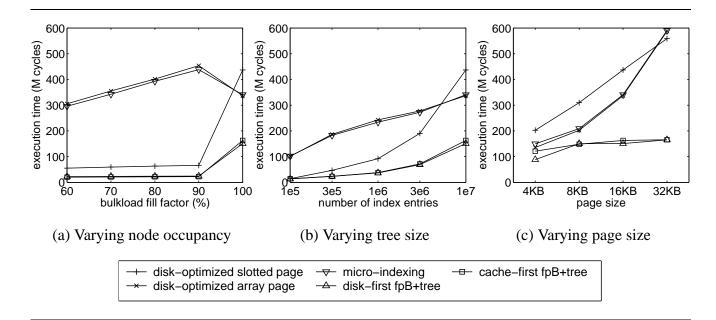

| 3.14 | Search varying node occupancy (10 million keys, 16KB pages, 10,000 searches) 94                                                                                                                           |

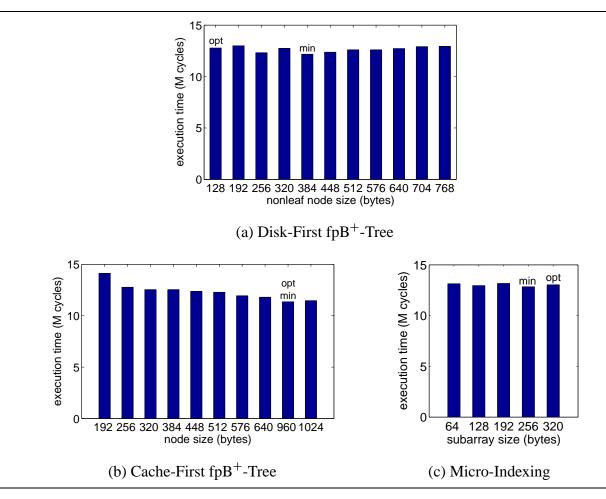

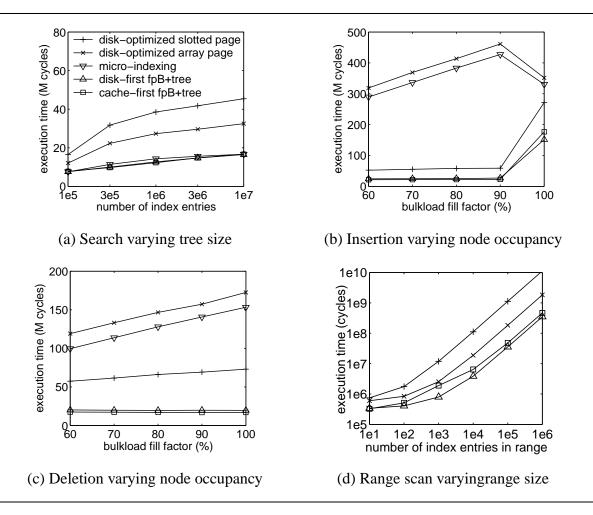

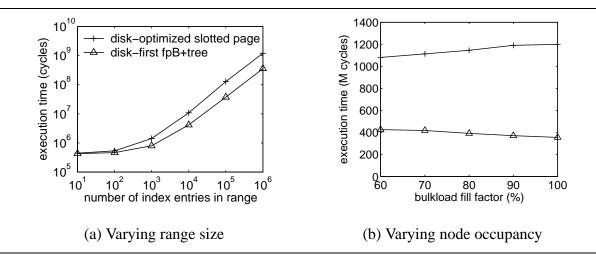

| 3.15 | Insertion cache performance (default parameters: 10 million keys, 100% full, 16 KB pages, 10,000 insertions)                                                                                              |

| 3.16 | Deletion cache performance (default parameters: 10 million keys, 100% full, 16 KB pages, 10,000 deletions)                                                                                                |

| 3.17 | Range scan performance (default parameters: 10 million keys in trees, 100% full, 16 KBpages, scanning 1 million keys).99                                                                                  |

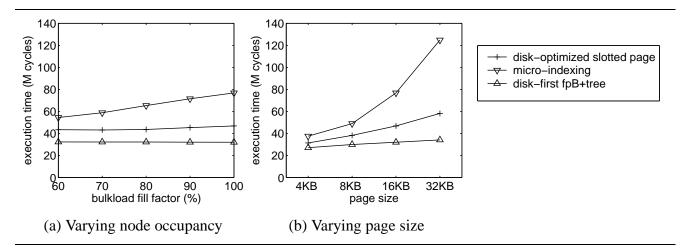

| 3.18 | Mature tree cache performance                                                                                                                                                                             |

| 3.19 | Operations with 20B keys and 16KB pages. (Disk-First fpB <sup>+</sup> -Tree: non-leaf node=64B, leaf node=384B; Cache-First fpB <sup>+</sup> -Tree: node size=576B; Micro-Indexing: subarray size = 128B) |

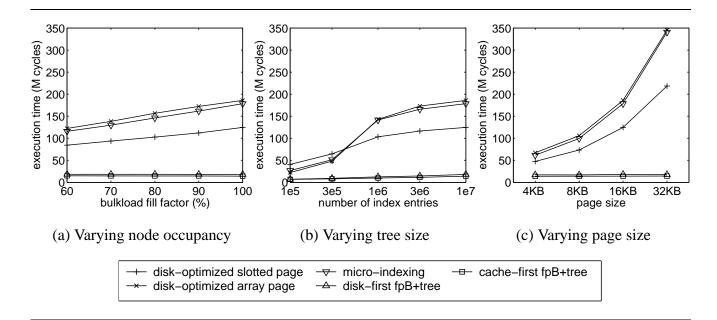

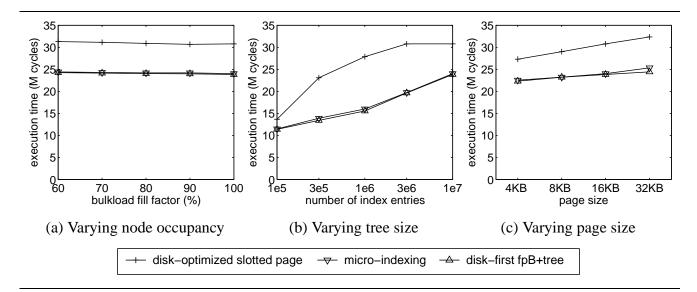

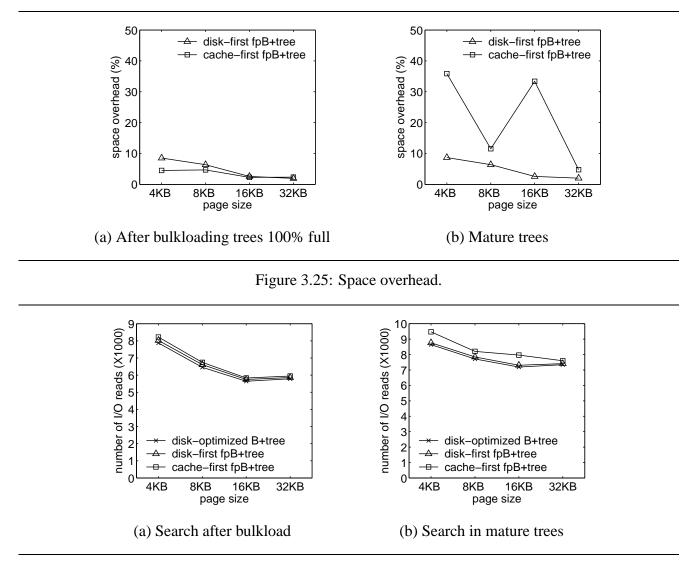

| 3.20 | Search cache performance on the Itanium 2 machine (default parameters: 10 million keys, 100% full, 16 KB pages, 10,000 searches)                                                                          |

| 3.21 | Insertion cache performance on the Itanium 2 machine (default parameters: 10 million keys, 100% full, 16 KB pages, 10,000 insertions)                                                                     |

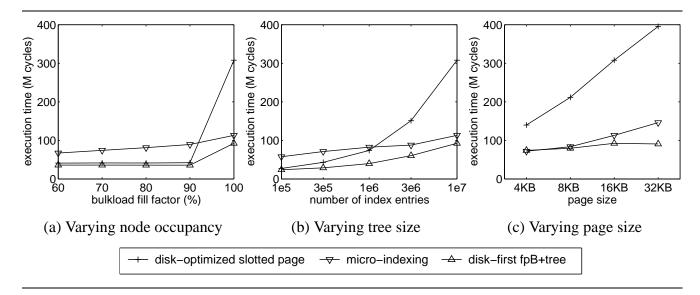

| 3.22 | Deletion cache performance on the Itanium 2 machine (default parameters: 10 million keys, 100% full, 16 KB pages, 10,000 deletions)                                                                       |

| 3.23 | Range scan cache performance on the Itanium 2 machine (default parameters: 10 million keys in trees, 100% full, 16 KB pages, scanning 1 million keys).                                                    |

| 3.24 | Operations on mature trees on the Itanium 2 machine (default parameters: 10 million keys in trees and 16 KB pages)                                                                                        |

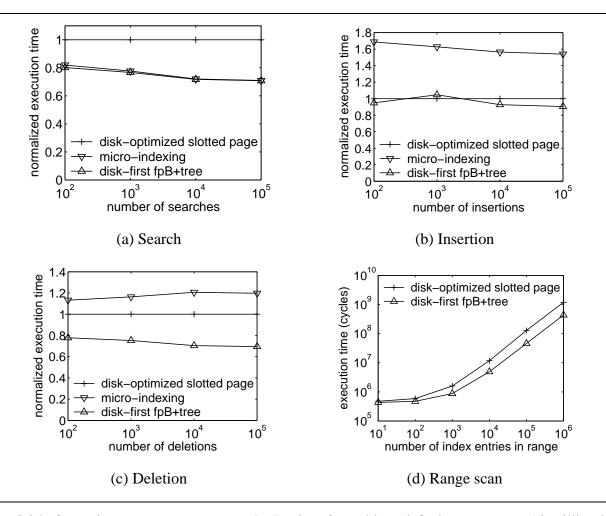

| 3.25 | Space overhead                                                                                                                                                                                            |

| 3.26 | Number of disk accesses for searches                                                                                                                                                                      |

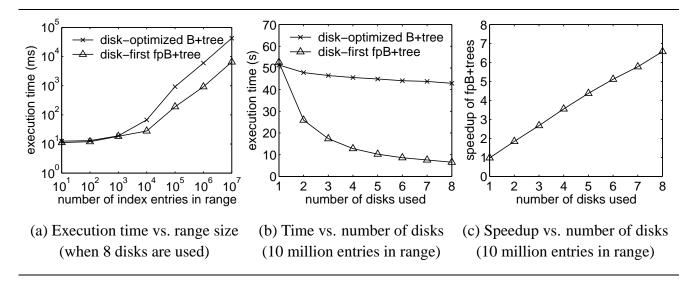

| 3.27 | Range scan disk performance                                                                                                                                                                               |

| 3.28 | Impact of jump-pointer array prefetching on the range scan performance of DB2 114                                                                                             |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.29 | Extracting key prefixes into an offset array                                                                                                                                  |

| 3.30 | fpB <sup>+</sup> -Trees for variable length keys                                                                                                                              |

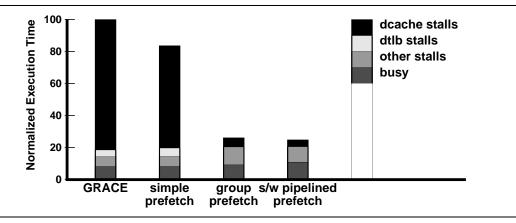

| 4.1  | User-mode execution time breakdown for hash join                                                                                                                              |

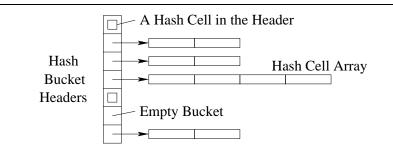

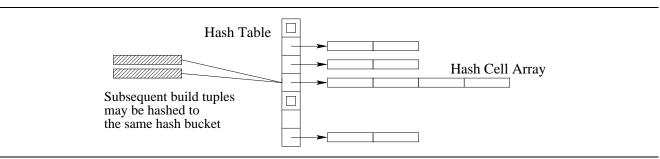

| 4.2  | An in-memory hash table structure                                                                                                                                             |

| 4.3  | Group prefetching                                                                                                                                                             |

| 4.4  | Critical path analysis for an iteration of the outer loop body in Figure 4.3(d) 131                                                                                           |

| 4.5  | Dealing with multiple code paths                                                                                                                                              |

| 4.6  | A read-write conflict                                                                                                                                                         |

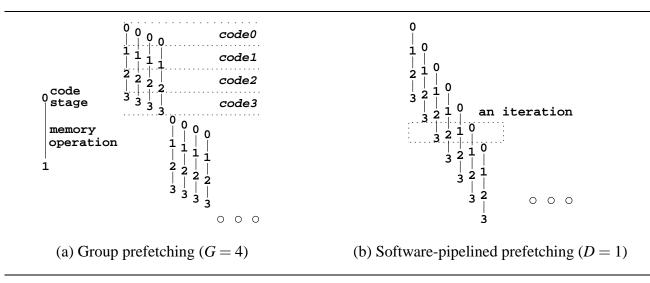

| 4.7  | Intuitive pictures of the prefetching schemes                                                                                                                                 |

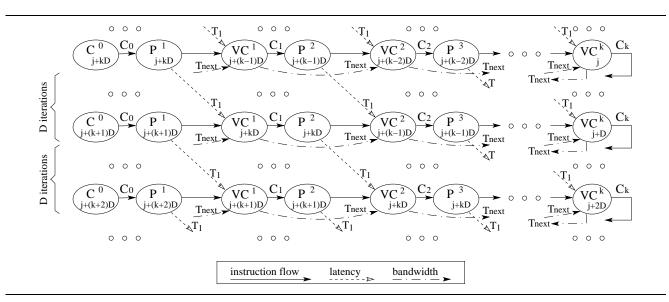

| 4.8  | Software-pipelined prefetching                                                                                                                                                |

| 4.9  | Critical path analysis for software-pipelined prefetching (steady state)                                                                                                      |

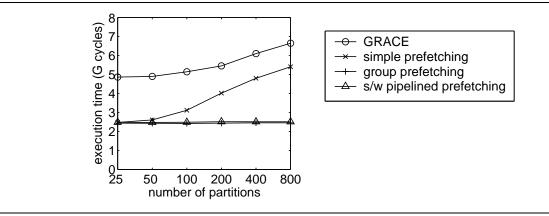

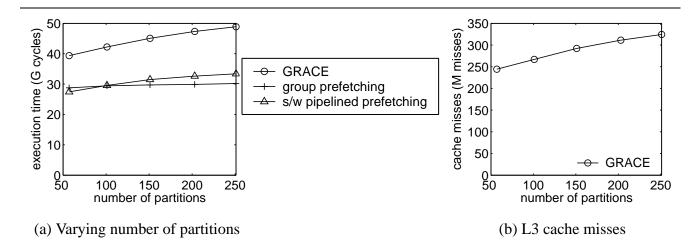

| 4.10 | Hash join is CPU-bound with reasonable I/O bandwidth                                                                                                                          |

| 4.11 | Join phase performance                                                                                                                                                        |

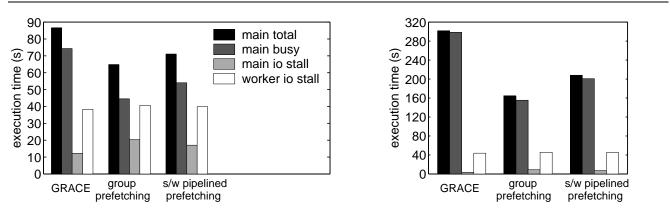

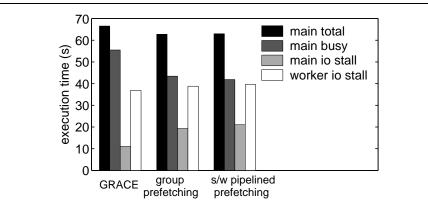

| 4.12 | Execution time breakdown for join phase performance (Figure 4.11(a), 100B tuples) 146                                                                                         |

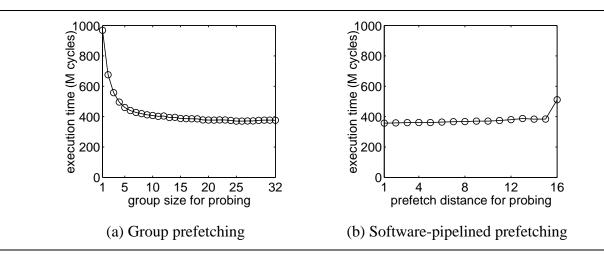

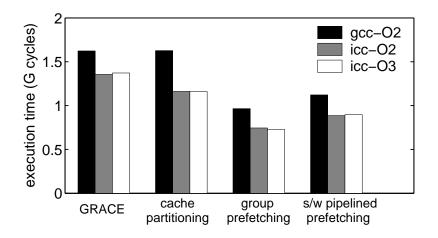

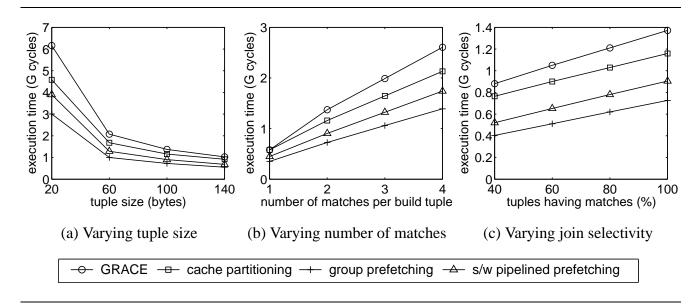

| 4.13 | Tuning parameters of cache prefetching schemes for hash table probing in the join phase. 147                                                                                  |

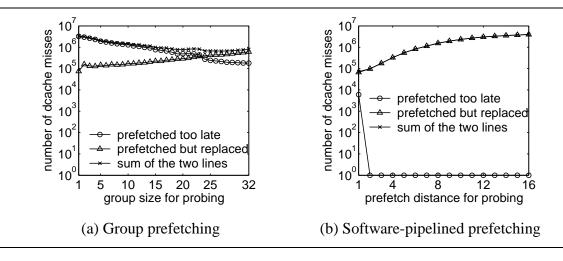

| 4.14 | Analyzing prefetched memory references that still incur data cache misses to understand the tuning curves of the join phase                                                   |

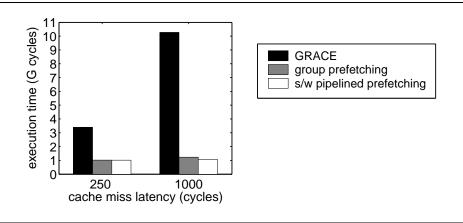

| 4.15 | Join phase performance varying memory latency                                                                                                                                 |

| 4.16 | Partition phase performance                                                                                                                                                   |

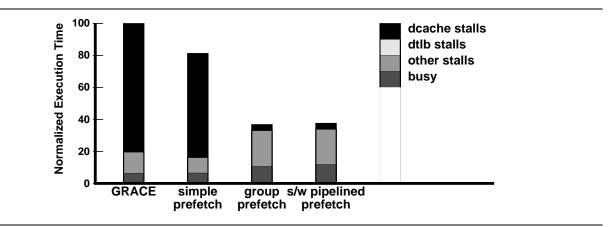

| 4.17 | Execution time breakdown for Figure 4.16 with 800 partitions                                                                                                                  |

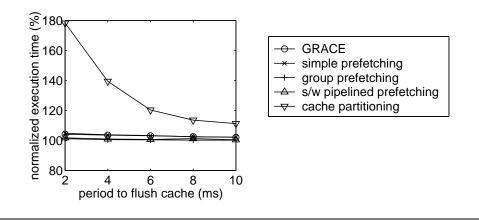

| 4.18 | Impact of cache flushing on the different techniques                                                                                                                          |

| 4.19 | Re-partitioning cost of cache partitioning. (Default parameters: 200 MB build relation, 400 MB probe relation, 100 B tuples, every build tuple matches two probe tuples.) 151 |

| 4.20 | Choosing the compiler and optimization levels for hash join cache performance study on the Itanium 2 machine                                                                  |

| 4.21 | Join phase cache performance on Itanium 2                                                                                                                                     |

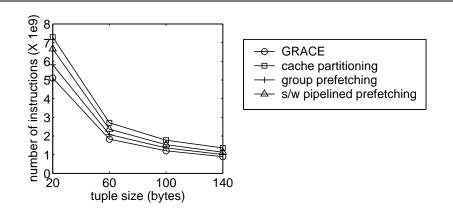

| 4.22 | Number of retired IA64 instructions for Figure 4.21(a)                                                                                                                        |

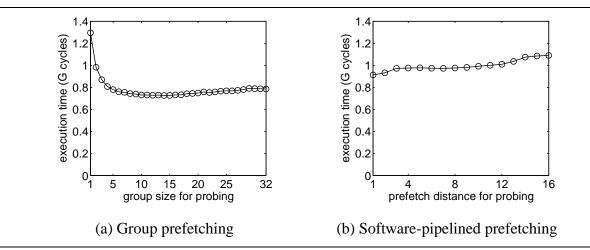

| 4.23 | Tuning parameters of group and software-pipelined prefetching for hash table probing<br>in the join phase on the Itanium 2 machine |

|------|------------------------------------------------------------------------------------------------------------------------------------|

| 4.24 | Partition phase performance on the Itanium 2 machine                                                                               |

| 4.25 | Join phase performance with I/Os when output tuples are consumed in main memory 157                                                |

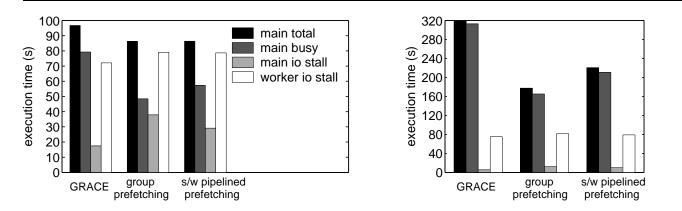

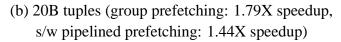

| 4.26 | Join phase performance with I/Os when output tuples are written to disk                                                            |

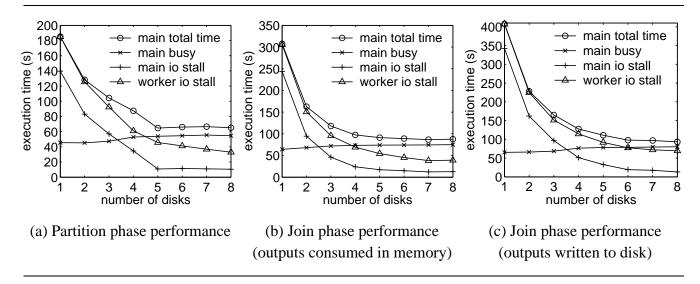

| 4.27 | I/O partitioning phase performance with I/Os                                                                                       |

| 5.1  | Impact of memory bandwidth sharing on join phase performance in an SMP system 163                                                  |

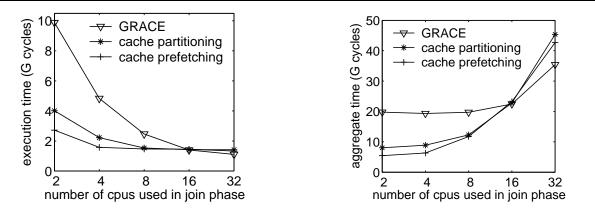

| 5.2  | Using multiple filters to inspect the data                                                                                         |

| 5.3  | Comparing the cache behaviors of different join phase algorithms                                                                   |

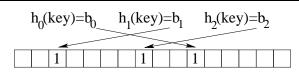

| 5.4  | A Bloom filter with three hash functions                                                                                           |

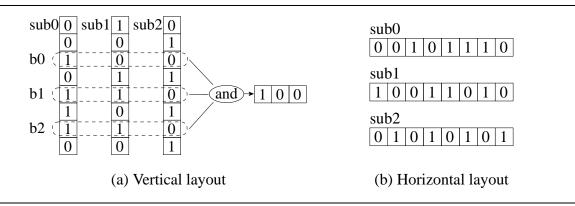

| 5.5  | Layouts of multiple Bloom filters                                                                                                  |

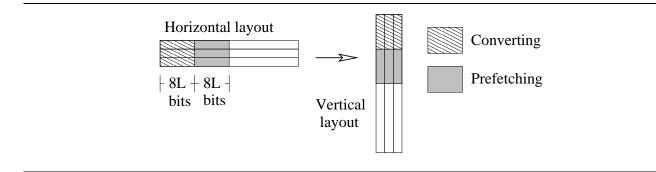

| 5.6  | Horizontal to vertical layout conversion                                                                                           |

| 5.7  | I/O partition and inspection phase algorithm                                                                                       |

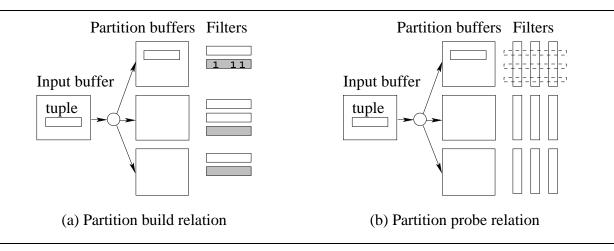

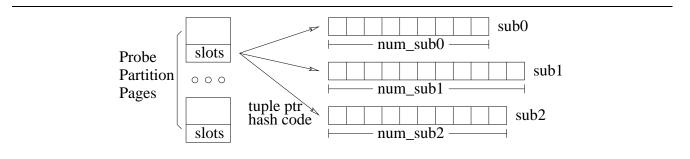

| 5.8  | Extracting probe tuple information for every sub-partition using counting sort                                                     |

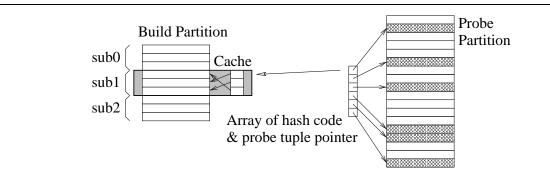

| 5.9  | Joining a pair of build and probe sub-partitions                                                                                   |

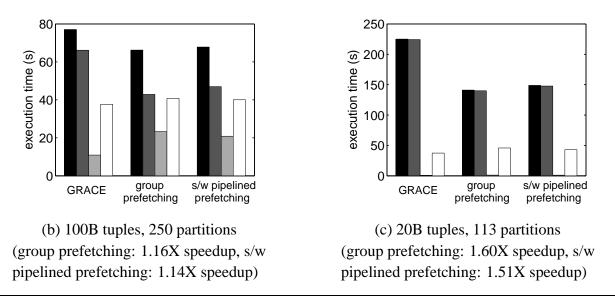

| 5.10 | Join phase user-mode time varying the number of CPUs used on the Itanium 2 machine. 184                                            |

| 5.11 | Varying the number of CPUs used through simulations                                                                                |

| 5.12 | Join phase CPU time breakdowns for CPU 0                                                                                           |

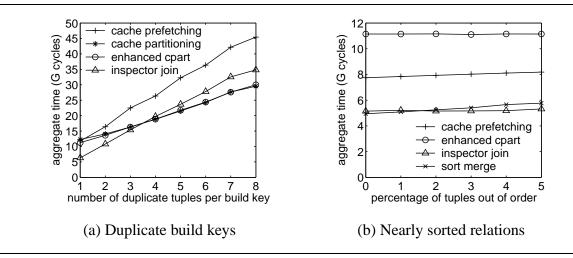

| 5.13 | Aggregate execution time varying three parameters when 8 CPUs are used in the join phase                                           |

| 5.14 | Robustness against cache interference (join phase performance self-normalized to the                                               |

|      | performance of the same algorithm without cache flushing, num CPUs used=1) 189                                                     |

| 5.15 | Exploiting the inspection mechanism                                                                                                |

# **List of Tables**

| 1.1        | Comparing the Cache-to-Memory Gap and the Memory-to-Disk Gap                         |

|------------|--------------------------------------------------------------------------------------|

| 2.1        | Terminology used throughout Chapter 2                                                |

| 2.2        | Itanium 2 machine configuration                                                      |

| 2.3        | Simulation parameters                                                                |

| 2.4        | The number of levels in trees with different node widths                             |

| 2.5        | The number of levels in trees for Figure 2.13(a) and (b)                             |

| 3.1<br>3.2 | Optimal width selections (4 byte keys, $T_1 = 250$ , $T_{next} = 15$ )               |

| 4.1        | Terminology used throughout Chapter 4                                                |

| 5.1        | Terminology used throughout Chapter 5                                                |

| 5.2        | Number of Bloom filter bits per key ( $d = 3$ )                                      |

| 5.3        | Total filter size varying tuple size (1 GB build relation, $fpr = 0.05$ , $S = 50$ ) |

## Chapter 1

## Introduction

Computer systems have enjoyed an exponential growth in processor speed for the past 20 years, while DRAM main memory speed has improved only moderately [39]. Today a cache miss to main memory takes hundreds of processor cycles (e.g., about 200 cycles on Itanium 2); considering the wide issue rate (e.g., up to six instructions on Itanium 2 [44]) of modern processors, this represents a loss of about a thousand or more instructions. Unfortunately, the CPU cache hierarchy provides only a partial solution to this problem. It works effectively when the working set of a program fits in the CPU cache, as evidenced by many of the SPEC benchmark results [80]. However, for programs working on large data sets with poor data locality, the *cache-to-memory latency gap* can be a major performance bottleneck. Recent database performance studies have demonstrated that, on commercial database systems, about 50% or more of the execution time in memory is wasted due to cache misses [2, 5, 51].

In light of this problem, a number of recent research studies focused on improving the CPU cache performance of database systems [1, 13, 14, 15, 28, 31, 36, 37, 38, 53, 62, 66, 67, 75, 78, 83, 84, 90, 102, 103]. Most of these studies aimed to improve the data locality of database algorithms for reducing the *number* of cache misses. In this thesis, we investigate a different approach: reducing the *impact* of cache misses by overlapping cache miss latencies with useful computations through a technique called *cache prefetching*. Combined with data locality optimizations, this technique enables larger freedom in redesigning core database structures and algorithms, leading to better CPU cache performance.

#### Chapter 1 Introduction

Let us begin by understanding the challenges of optimizing CPU cache performance. At first glance, this new cache-to-memory gap may look similar to the familiar memory-to-disk gap. Main memory is used as a buffer cache for disk, while hardware SRAM caches are used as caches for DRAM main memory. Data is transferred in units of a certain size: a disk page for the memory-to-disk gap, and a cache line for the cache-to-memory gap. When SRAM caches or DRAM main memory are full and new data is requested, some cache line or memory page has to be replaced to make room for the new data. Because of this similarity, a question immediately arises: Can we simply adapt disk optimization techniques to the cache-to-memory gap and solve the entire problem?

## 1.1 Can We Simply Adapt Memory-to-Disk Techniques?

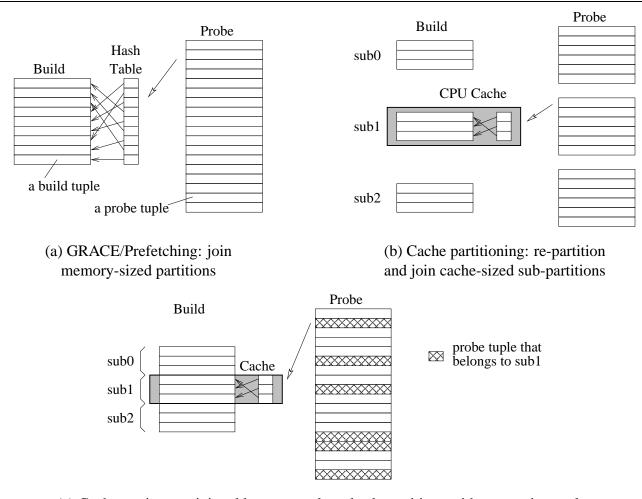

Because of the similarity between the two gaps, some disk optimization techniques indeed can be applied to the cache-to-memory gap. An example is the partitioning technique for the database hash join algorithm. In order to avoid expensive random disk accesses, the hash join algorithm divides its working set into pieces (a.k.a. partitions) that fit into main memory using an I/O partitioning technique [54, 59, 74, 89, 101]. Similarly, it is also a good idea to fit the working set of a program into the CPU cache, and therefore the cache-to-memory counterpart to the I/O partitioning technique can effectively avoid random memory accesses for good hash join cache performance [14, 66, 90].

However, a close examination reveals a lot of differences between the two gaps as shown in Table 1.1, several of which have fundamental impacts on the designs of optimization techniques. Moreover, the optimization targets are more complex. We cannot simply optimize for a single gap (the cache-to-memory gap) because both the cache-to-memory gap and the memory-to-disk gap are important for commercial database systems. Therefore, adapting memory-to-disk techniques does not provide a *full* solution to the cache-to-memory problem. We discuss the two reasons at length in the following.

• The differences between the two gaps present new challenges and opportunities. Although database systems have full control of the main memory buffer pool, CPU caches are typically managed by hardware. This is because CPU caches are performance critical from the viewpoint

| Feature            | Largest SRAM Cache          | DRAM Main Memory       |

|--------------------|-----------------------------|------------------------|

| Capacity           | 1-10 MB                     | 1 GB - 1 TB            |

| Transfer Unit Size | 32-128B                     | 4-64 KB                |

| Miss Latency       | $10^2 - 10^3$ cycles        | $10^{6}-10^{7}$ cycles |

| Associativity      | 4-16 way set associative    | fully associative      |

| Replacement Policy | variants of LRU in each set | variants of LRU        |

| Management         | hardware                    | software               |

Table 1.1: Comparing the Cache-to-Memory Gap and the Memory-to-Disk Gap.

Note: Data sources include processor manuals and textbooks [39, 44, 46, 50, 81, 91, 96].

of processors; even the largest cache is designed to be very close to the processor (e.g., a 12-cycle access latency on Itanium 2 [44]). Therefore, CPU caches cannot afford to support sophisticated software strategies such as previous proposals of data replacement techniques for main memory buffer pools [21, 48, 76].

Given the hardware replacement policy (typically some variants of LRU within a set [39]), whether a data item is in the cache is determined *implicitly* by the memory accesses seen at the cache. Although we may expect some useful data items to stay in the cache when designing an algorithm, they may well be evicted from the cache because of cache pollution, e.g., from streaming through a large amount of read-once data, or because the processor performs activities other than the target algorithm, such as executing other procedures for the same database query or running different threads for other queries. Therefore, robustness to such cache interference is a desirable property of an optimization technique.

Apart from the difference in cache management, another major difference between the cacheto-memory and the memory-to-disk gap is the extremely different transfer unit sizes: 32-128B cache lines vs. 4-64 KB disk pages. Naively, one might regard the transfer unit size simply as an adjustable parameter to optimization techniques. However, it has more profound impacts because of its relative size to the data stored. For example, if index node size is chosen to be the transfer unit size for good performance (as in  $B^+$ -Trees [81, 84, 91]), the resulting structures at the cache granularity have much smaller node fanouts and much higher trees. Realizing that accessing every level of a tree index incurs an expensive cache miss, researchers proposed various techniques to increase the fanout of index nodes for better cache performance [13, 53, 83, 84].

Moreover, the relationship between database records and transfer units changes. Note that database records can be 100 bytes or larger (as evidenced by the TPC benchmark setups [98]). Therefore, records can no longer be stored *inside* a transfer unit at the CPU cache granularity, but rather *span* one or a few transfer units. From our experience, understanding this subtlety is often important in designing a good solution and in analyzing the cache behavior of a program.

• Commercial database systems require both good cache and good disk performance. There are two primary types of relational database systems: traditional database systems and main memory database systems. The latter assume the entire database resides in main memory, which has been an important research topic [25, 57, 58] and led to commercial products such as TimesTen [97], and research systems such as Dalí [47] and Monet [71]. However, the leading commercial database systems including Oracle [77], IBM DB2 [41], and Microsoft SQL Server [70], all follow the structure of traditional database systems [3, 95]: Data is stored on disk and loaded into the main memory buffer pool before being processed. In such a database system, both the cache-to-memory gap and the memory-to-disk gap may become the performance bottleneck depending on system configurations and database workloads. Therefore, it is important to optimize for both good CPU cache performance and good disk performance. Achieving this goal often presents more challenges than putting together disk and cache optimization techniques, as evidenced by the studies that optimize data page layout for better CPU cache performance [1, 36, 82],

Summarizing the above discussions, we point out that optimizing the cache-to-memory gap is not as simple as an exercise of applying the memory-to-disk techniques. New challenges and new opportunities arise in optimizing the CPU cache performance for database systems.

## **1.2 Cache Optimization Strategies**

After analyzing the challenges in optimizing CPU cache performance, we describe the general optimization strategies in this section. Our purpose is to provide a framework to clarify the position of our approach in the entire schemes towards bridging the cache-to-memory gap.

There are two general optimization strategies for improving CPU cache performance of a program: reducing the *number* of cache misses and reducing the *impact* of cache misses by overlapping cache misses with computations and other misses.

### **1.2.1** Reducing the *Number* of Cache Misses

The first general strategy is to remove cache misses of a program by improving data reference locality of the program. The idea is to fit the working set of the program into the CPU cache, thus reducing the need to load data from main memory. One way to achieve this goal is to change the order in which data items are visited in the program so that references to the same data item occur closely in time (*temporal locality*) and references to multiple data items from the same cache line occur closely in time (*spatial locality*) without incurring any additional cache misses. A well-known example is blocked matrix multiplication, which works on sub-blocks of matrices for good cache performance [39]. An alternative way to improve data reference spatial locality is to modify the placement of data items in a program by packing into the same cache lines data items that are used closely in time. This may require changes ranging from reordering fields in data structure definitions, to introducing preprocessing steps such as the partitioning step for hash joins [14, 66, 90], as discussed previously in Section 1.1. Moreover, compression techniques [13, 31, 53, 104, 83, 84] trade off the processor's processing power for more compact data representations, thus helping reduce the working set of a program.

In terms of the types of cache misses, the above discussion focuses on reducing *capacity* misses, i.e. cache misses because of a program's working set exceeding cache capacity. This is often a major cause for poor cache performance (as in matrix multiplication and hash joins). Cache misses can also result from accessing data for the first time (*cold* misses) and from the limited set associativities of CPU

caches  $(conflict \text{ misses})^1$ . Conflict misses are usually less of a problem when the set associativities are 8 or higher [39], which is common for high-end processors [50, 44], and the trend is to support higher associativities. However, cold misses cannot be easily removed by definition (except that compression techniques might help).

### 1.2.2 Reducing the *Impact* of Cache Misses

The second general strategy for optimizing CPU cache performance is to make cache misses less expensive by exploiting memory system parallelism. Modern processors allow multiple outstanding cache misses to be in flight simultaneously within the memory hierarchy. For example, the Itanium 2 system bus control logic has an 18-entry out of order queue, which allows for a maximum of 19 memory requests to be outstanding from a single Itanium 2 processor [44]. Modern processors support several mechanisms that exploit this parallelism:

- **Instruction Speculation**. In many modern processors, the hardware attempts to overlap cache misses by speculating ahead in the instruction stream. While this mechanism is useful for hiding the latency of primary data cache misses that hit in the secondary cache, the number of instructions a processor can look ahead (a.k.a. instruction window size)<sup>2</sup> is far too small to fully hide the latency of cache misses to main memory [26].

- Hardware-Based Cache Prefetching. Modern processors (e.g., Intel Pentium 4 [46] and Itanium 2 [44]) can automatically load instructions and/or data from main memory before use, thus overlapping cache miss latencies with useful computations. However, hardware-based data prefetching techniques [4] rely upon recognizing regular and predictable (e.g., strided) patterns in the data ad-

<sup>&</sup>lt;sup>1</sup>Data sharing (true sharing or false sharing) between multiple threads running on different processors in a multiprocessor system may cause *coherence* cache misses. In this thesis, we mainly focus on cache misses incurred by a single thread of execution.

<sup>&</sup>lt;sup>2</sup>Intel Pentium 4 [12] has an 126-instruction reorder buffer. Intel Itanium 2 [44] has an eight-stage core pipeline with a 24-instruction buffer between stage 2 and 3. Since its issue rate is up to six instructions per cycle, there can be up to 72 instructions running in the pipeline simultaneously in Itanium 2. Note that the instruction window size is roughly one order of magnitude smaller than the instruction opportunities wasted per cache miss.

Figure 1.1: Illustration of the use of prefetch instructions to hide cache miss latencies.

dress stream, while many important database algorithms (e.g., searching a  $B^+$ -Tree index and visiting a hash table in hash joins) have less regular or rather random access patterns.

• Software Cache Prefetching. Modern processors (e.g., Intel Itanium 2 [44] and Pentium 4 [46]) provide *prefetch* instructions that allow software to influence the timing of cache misses. Figure 1.1 illustrates the use of prefetch instructions to hide cache miss latencies. As shown on the left, without prefetching, the processor stalls when it attempts to load two locations that are not present in the cache. As shown on the right, if we know the memory addresses of the loads early enough, we can issue prefetch instructions to read the data into the cache before the execution of the actual load instructions. In this way, the cache miss latencies can be overlapped with the execution of other useful instructions. Moreover, the first cache miss latency can be overlapped with the second. This is because the memory system can serve multiple cache misses simultaneously.

Prefetch instructions can be regarded as light-weight, non-blocking memory load operations without register destinations. Such memory operations are performed in the background, and do not block the foreground executions. Software has the flexibility to decide what and when to prefetch. Therefore, software cache prefetching is potentially helpful for reducing the impact of any types of cache misses, including both capacity misses and cold misses, for handling different kinds of memory access patterns, and for improving all kinds of programs.

A processor can support many different flavors of prefetch instructions. For example, both Itanium

#### Chapter 1 Introduction

2 and Pentium 4 support prefetch instructions to load data into different levels of caches [45, 43]. They also support special streaming prefetch instructions, which indicate that the prefetched data will be used only once and therefore should be loaded in a special way to reduce cache pollution. Moreover, Itanium 2 supports both faulting and non-faulting prefetches [45]. Non-faulting prefetches will be dropped if the virtual page table entry is missing from the TLB or if other exceptional conditions may result from executing the prefetches. In contrast, a faulting prefetch behaves more like a common load instruction; upon a TLB miss, it will load the page entry into the TLB table and continue. Therefore, faulting prefetches are specially useful if TLB misses are likely, e.g., when prefetching for random memory accesses.

• Multiple Hardware Threads. More and more processors support multiple hardware threads through simultaneous multithreading (SMT) [99] or single chip multiprocessors (CMP) [6, 34, 35] or a combination of the two (e.g., Intel Pentium 4 [44], IBM Power 5 [50], and Sun UltraSPARC IV [96]). When one hardware thread blocks because of a cache miss, the other hardware threads can be still running on the processor. However, it is a non-trivial task to break down a sequential program into multiple parallel threads in order to reduce the elapsed time of a single program, as evidenced by a recent study to utilize a multi-threaded and multi-core network processor for query processing [28]. Even if assuming hardware support for speculating threads [92] so that correctness is guaranteed, it still requires significant efforts to minimize data sharing across threads in order to achieve good performance [22]. Without these efforts, simply running a program on an SMT or CMP processor does not necessarily speed up the program, rather the program tends to slow down because of cache interference from other threads running on the same processor.

The two general optimization strategies described above are complementary. The first strategy is important because it reduces memory bandwidth requirement. The second strategy is important because a significant number of misses (e.g., cold misses) often still exist after applying the first strategy. The two strategies constitute a framework for bridging the cache-to-memory gap: reducing as many cache misses as possible with the first strategy, then reducing the impact of the remaining cache misses with the second strategy.

## 1.3 Our Approach: Redesigning Database Systems in Light of CPU Cache Prefetching

With the general optimization strategies in mind, we see that cache prefetching (software cache prefetching<sup>3</sup>) is a promising technique for reducing the impact of cache misses. Cache prefetching has been shown to be effective for both array-based and pointer-based codes in scientific and engineering applications [64, 65, 72, 73]. However, it has not been systematically studied for database systems before. Therefore, in this thesis, we investigate cache prefetching for improving the CPU cache performance of database systems. Unlike most previous studies (as will be described in Section 1.4), we target traditional disk-oriented database systems, which are supported by all the leading database vendors and are widely used, rather than main memory databases. We redesign core database structures and algorithms by using novel techniques enabled and inspired by cache prefetching.

Since prefetching for sequential array accesses has been well studied before and is often supported by hardware-based prefetching [4], we are interested in studying non-contiguous access patterns in database systems. Such patterns are abundant in algorithms involving tree structures and hash tables. Therefore, we focus specially on the  $B^+$ -Tree index [7, 8] as a representative tree implementation, and the hash join algorithm [54, 89] as a representative algorithm using hash tables. We re-examine their designs with cache prefetching in mind, and combine cache prefetching and data locality optimizations to achieve good cache performance. In the following, we describe our approaches to improving the  $B^+$ -Tree index and the hash join algorithm in more detail.

B<sup>+</sup>-Trees. B<sup>+</sup>-Trees [7, 8] are used extensively for fast associative lookups throughout database systems. Compared to a binary tree, a B<sup>+</sup>-Tree is a multi-way search tree. Our goal for studying B<sup>+</sup>-Trees is to improve the performance of B<sup>+</sup>-Trees in commercial database systems in light of prefetching. We achieve this goal in two steps. In the first step, we focus purely on the CPU cache performance of B<sup>+</sup>-Trees within a main memory database environment. With the understandings obtained from the first step, we then optimize B<sup>+</sup>-Trees in a traditional database system with disk

<sup>&</sup>lt;sup>3</sup>Throughout the thesis, we use cache prefetching or prefetching as short terms for software cache prefetching unless otherwise noted.

#### Chapter 1 Introduction

I/Os in the picture. Our goal in the second step is to achieve good cache performance when most of the  $B^+$ -Tree is in the main memory buffer pool, and still maintain good disk performance when the  $B^+$ -Tree is mainly on disk. Moreover, it is interesting to analyze whether the techniques developed in the first step for the cache-to-memory gap are also applicable to the memory-to-disk gap, which will provide a deeper understanding of the differences between the two gaps.

• *Hash Joins*. Commercial hash join algorithms consist of two phases: the I/O partitioning phase and the join phase [54, 59, 74, 89, 101]. The I/O partitioning phase divides the input relations into memory-sized partitions to avoid random disk accesses because of hashing. Our goal for studying hash joins is to improve the performance of both partitioning and join phases of the hash join algorithm in commercial database systems. We also take two steps in this study. Our first step is to exploit cache prefetching for the two phases *separately*. The major challenge is to effectively issue prefetch instructions despite the random access patterns of hash table visits. Our second step is to take advantage of the two-phase structure of the hash join algorithm for further optimizing its performance. Moreover, because multiple processors can join multiple memory-sized partitions simultaneously, hash join is a good workload for studying the impact of multiple processors on the performance of prefetching algorithms.

We implement our optimization algorithms and measure the actual performance of working codes both on an Itanium 2 machine and on a simulation platform to better understand the cache behaviors of the algorithms.

## 1.4 Related Work

In this section, we present related work to  $B^+$ -Tree cache performance and hash join cache performance. Please note that some of the studies we discuss appeared after our original publications [16, 17, 18, 19] in the completion of this thesis. In the following, we mainly describe the high-level ideas. We will perform more detailed experimental comparisons between previous techniques and our proposals in Chapter 2-5.

## **1.4.1** Related Work on B<sup>+</sup>-Trees

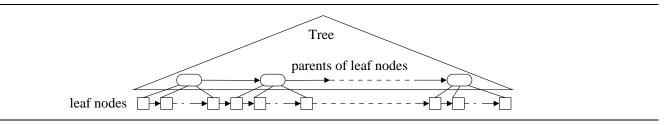

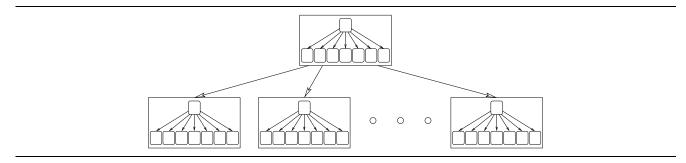

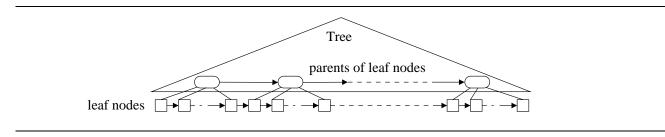

A B<sup>+</sup>-Tree [7, 8] is a multi-way search tree, where each leaf node contains multiple index entries, and each non-leaf node has multiple children. A B<sup>+</sup>-Tree is a balanced tree structure; all the leaf nodes occur at the same level. Leaf nodes are connected through sibling links into key order to facilitate the retrieval of a range of index entries. A B<sup>+</sup>-Tree is also a *dynamic* index structure; it supports insertions and deletions efficiently without the need to re-build the tree periodically.

**Main Memory B<sup>+</sup>-Trees.** Chilimbi, Hill, and Larus demonstrated that B<sup>+</sup>-Trees with cache line sized nodes can outperform binary trees for memory-resident data on modern processors [20]. Likewise, B<sup>+</sup>-Trees outperform index structures specially designed for main memory databases (in the first thrust of main memory database research assuming uniformly fast memory accesses), *i.e.* T-trees [57], on today's processors [83].

Main memory B<sup>+</sup>-Trees have cache-line-sized nodes with small fanouts (typically 8 compared to several hundred for disk-oriented B<sup>+</sup>-Trees with disk-page-sized nodes). Therefore, the trees are very high (e.g., 8 levels when there are 10 million 4-byte keys in trees with 64-byte nodes). Realizing that the number of expensive cache misses in a search is roughly proportional to the height of the tree, researchers aimed to improve the fanout of cache-line-sized nodes to reduce the tree levels, thus reducing the *number* of expensive misses. Rao and Ross proposed "Cache-Sensitive Search Trees" (CSS-Trees) [83] and "Cache-Sensitive B<sup>+</sup>-Trees" (CSB<sup>+</sup>-Trees) [84] that restrict the data layout of sibling nodes so that all (or nearly all) of the child pointers can be eliminated from the parent. This saves space in non-leaf nodes for more index entries. Bohannon, McIlroy, and Rastogi proposed partial-key trees that store compressed keys in indices for larger fanouts [13].

Beyond improving the performance of a single search operation, researchers have studied how to improve the throughput of a large number of back-to-back searches. Zhou and Ross proposed to buffer accesses at every non-root tree node so that multiple accesses may share the cache miss of visiting a node [102]. Moreover, Cha *et al.* [15] proposed an optimistic scheme for B<sup>+</sup>-Tree concurrency control in main memory.

#### Chapter 1 Introduction

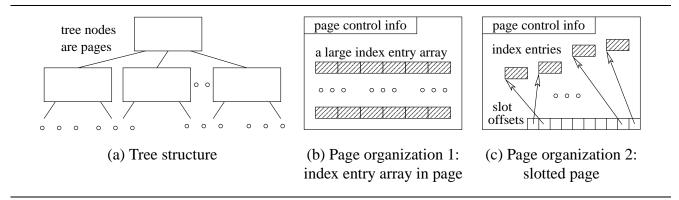

**CPU Cache Performance of Disk-Oriented B<sup>+</sup>-Trees.** In commercial database systems, B<sup>+</sup>-Tree nodes are disk pages, typically 4-64KB large. Binary searches in such a large node can have very poor spatial locality; the first several probes in a binary search always access a single key out of an entire cache line, then discard the rest of the line. To reduce the *number* of cache misses of searches, Lomet described an idea, intra-node micro-indexing, in his survey of B<sup>+</sup>-Tree page organization techniques [62]. It places a small array in a few cache lines of the page that indexes the remaining keys in the page. This small micro-index replaces the first several probes in a binary search, thus improving the spatial locality of a search. However, this scheme suffers from poor update performance. As part of future directions, Lomet [62] has advocated breaking up B<sup>+</sup>-Tree disk pages into cache-friendly units, pointing out the challenges of finding an organization that strikes a good balance between search and insertion performance, storage utilization, and simplicity. Bender, Demaine, and Farach-Colton presented a recursive B<sup>+</sup>-Tree structure that is *asymptotically* optimal, regardless of the cache line sizes and disk page sizes, but assuming no prefetching [9].

### **1.4.2 Related Work on Hash Joins**

*Hash join* [54, 59, 74, 89, 101] has been studied extensively over the past two decades. It is commonly used in today's commercial database systems to implement equijoins efficiently. In its simplest form, the algorithm first builds a hash table on the smaller (*build*) relation, and then probes this hash table using records of the larger (*probe*) relation to find matches. However, the random access patterns inherent in the hashing operation have little spatial or temporal locality. When the main memory available to a hash join is too small to hold the build relation and the hash table, the simplistic algorithm suffers excessive random disk accesses. To avoid this problem, the *GRACE* hash join algorithm [54] begins by dividing the two joining relations into smaller intermediate partitions such that each build partition and its hash table can fit within main memory; pairs of memory-sized build and probe partitions are then joined separately as in the simple algorithm. This *I/O partitioning* technique limits the random accesses to objects that fit within main memory and results in nice predictable I/Os for both source relations and intermediate partitions.

A technique similar to I/O partitioning, called cache partitioning was proposed to avoid random memory accesses, thus reducing the *number* of cache misses. *Cache partitioning*, in which the joining relations are partitioned such that each build partition and its hash table can fit within the (largest) CPU cache, has been shown to be effective in improving performance in *memory-resident and main-memory* databases [14, 66, 90]. Shatdal, Kant, and Naughton showed that cache partitioning achieves 6-10% improvement for joining memory-resident relations with 100B tuples [90]. Boncz, Manegold, and Kersten proposed using multiple passes in cache partitioning to avoid cache and TLB thrashing when joining vertically-partitioned relations (essentially joining two 8B columns) in the Monet main memory database environment [14, 66]. The generated join results are actually a join index [100] containing pointers to matching pairs of records stored in vertical partitions. In order to efficiently extract the matching records, Manegold *et al.* proposed a cache conscious algorithm, called Radix-Decluster Projection that performs sophisticated locality optimizations [67].

In summary, most related work on CPU cache performance of  $B^+$ -Trees and hash joins focused on reducing the *number* of cache misses in *main memory* database environments. Very few studies tried to address their CPU cache performance in disk-oriented databases, and those that do exist did not provide extensive experimental evaluations of the proposed ideas. In contrast, we investigate cache prefetching to reduce the *impact* of cache misses, we target traditional disk-oriented database systems, which are supported by all the leading database vendors, and we present detailed performance studies of all our proposed techniques.

### 1.5 Contributions

The primary contributions of this thesis are the following:

• The first study that reduces the *impact* of cache misses for B<sup>+</sup>-Trees and hash joins by exploiting cache prefetching. In addition to inserting prefetches, we redesign algorithms and data structures to make prefetching effective. Unlike most previous studies on B<sup>+</sup>-Tree and hash join cache per-

formance, we target traditional *disk-oriented* database systems rather than *main memory* databases because traditional disk-oriented databases are widely supported and used. For B<sup>+</sup>-Trees, we address both the cache-to-memory gap and the memory-to-disk gap in the disk-oriented environment. For hash joins, we demonstrate that disk-oriented hash joins are CPU-bound with reasonable I/O bandwidth. Therefore, we mainly focus on bridging the cache-to-memory gap.

- The proposal and evaluation of a novel main memory index structure, *Prefetching B<sup>+</sup>-Trees*, which uses cache prefetching to accelerate two major access patterns of B<sup>+</sup>-Tree indices in the pure main memory environment: searches and range scans. Our solution has better search performance, better range scan performance, and comparable or better update performance over B<sup>+</sup>-Trees with one-cache-line nodes. Moreover, we achieve better performance than CSB<sup>+</sup>-Trees [84], and we show that CSB<sup>+</sup>-Trees and our prefetching scheme are complementary.

- The proposal and evaluation of a novel index structure, *Fractal Prefetching B*<sup>+</sup>-*Trees*, that optimizes index operations both for cache performance and for disk performance. We propose two different implementations of this index structure, a disk-first implementation and a cache-first implementation. Experimental results show that the disk-first implementation achieves the goals while the cache-first implementation may incur large disk overhead. We also study the effects of employing the prefetching techniques proposed in pure main memory environments for optimizing disk performance.

- The proposal and evaluation of two prefetching techniques, *Group Prefetching and Software-Pipelined Prefetching*, that exploit inter-tuple parallelism for overlapping cache misses incurred in processing a tuple across the processing of multiple tuples. Experimental results show that our techniques achieve dramatically better performance over cache partitioning and original hash joins. Moreover, our techniques are more robust than cache partitioning when there are concurrent activities in the computer system.

- The proposal and evaluation of a novel hash join algorithm, *Inspector Joins*, that exploits the free information obtained from one pass of the hash join algorithm to improve the performance of a later pass. We propose a specialized index that addresses the memory bandwidth sharing problem,

and can take advantage of nearly-sorted relations. Moreover, we utilize cache prefetching to improve the robustness of Inspector Joins in the face of cache interference. Furthermore, we present an illustrative example of how Inspector Joins can use its collected statistics to select between two join phase algorithms for the given query and data. Finally, our experiments demonstrate significant performance improvement of Inspector Joins over previous state-of-the-art cache prefetching and cache partitioning algorithms.

### 1.6 Thesis Organization

Chapter 2 investigates cache prefetching techniques for improving  $B^+$ -Trees in main memory environments. This is the first step in our  $B^+$ -Tree study. We describe our solution for improving two major access patterns of  $B^+$ -Trees: searches and range scans. For searches, we present a novel scheme to avoid predicting and prefetching child nodes. For range scans, we solve the pointer chasing problem. We compare the performance of our solution against CSB<sup>+</sup>-Trees [84]. We also combine our prefetching techniques with CSB<sup>+</sup>-Trees to understand the interactions of the two schemes.

Chapter 3 describes our design of a single index structure, Fractal prefetching B+-Trees, that achieves both good cache performance and good disk performance. The basic idea is to embed  $B^+$ -Trees optimized purely for cache performance into  $B^+$ -Trees optimized purely for disk performance. Our cacheoptimized  $B^+$ -Trees are based on the study in Chapter 2. This embedding process usually leads to large overflow or large underflow of disk pages. We describe two schemes, a disk-first scheme and a cachefirst scheme, to solve this problem. We evaluate the performance of our solutions against  $B^+$ -Trees and micro-indexing. Moreover, we discuss the implications of applying the same prefetching techniques from Chapter 2 for improving memory-to-disk performance.

Chapter 4 exploits cache prefetching for improving hash join performance. This is the first step in our hash join study. The major difficulty in employing prefetching is that it is impossible to generate addresses for hash table accesses early enough for effective prefetching. We solve this problem by taking advantage of the large number of records to be joined and exploiting the inter-tuple parallelism.

#### Chapter 1 Introduction

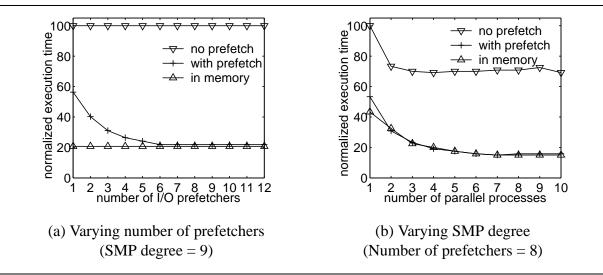

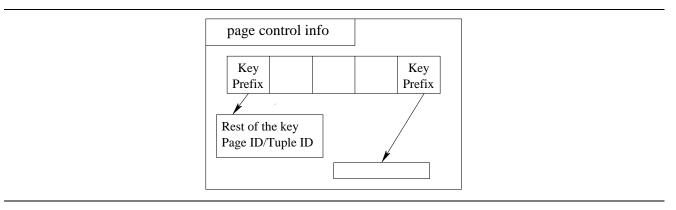

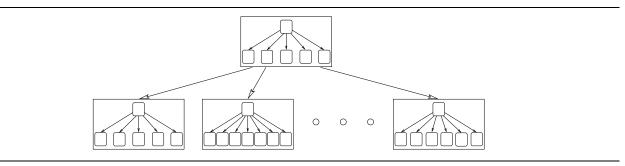

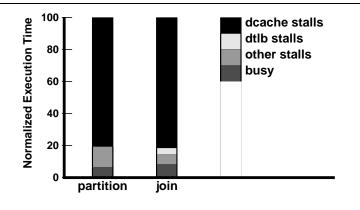

We describe two techniques, group prefetching and software-pipelined prefetching, for improving the I/O partitioning phase and the join phase performance. Our experimental results first show that hash joins are CPU bound in a balanced server system. We then compare the performance of our solution against cache partitioning and original hash joins.