### Explicit Compiler-based Memory Management for Out-of-core Applications

Angela Demke Brown May 2005 CMU-CS-05-140

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Thesis Committee: Todd Mowry, Chair M. Satyanarayanan Garth Gibson Monica Lam, Stanford University

Copyright © 2005 Angela Demke Brown

This research was sponsored by the National Aeronautics and Space Administration (NASA) under grant no. NAG2-1230 and the National Science Foundation (NSF) under grant nos. CCR-0085938 and EEC-8907068. The views and conclusions contained herein are those of the author and should not be interpreted as necessarily representing the official policies or endorsements, either expressed or implied, of any sponsoring party or the U.S. Government.

**Keywords:** I/O prefetching, compiler analysis, virtual memory management, software pipelining, outof-core applications, dynamic adaptation.

## Abstract

For a large class of scientific computing applications, the continuing growth in physical memory capacity cannot be expected to eliminate the need to perform I/O throughout their executions. For these *out-of-core* applications, the large and widening gap between processor performance and disk latency is a major concern. Current operating systems deliver poor performance when an application's working set does not fit in main memory. As a result, programmers who wish to solve these out-of-core problems efficiently are typically faced with the onerous task of rewriting their application to use explicit I/O operations (e.g., read/write). In many cases, the end result is that the size of physical memory determines the size of problem that can be solved.

In this dissertation, we propose and evaluate a fully-automatic technique which liberates the programmer from this task, provides high performance, and requires only minimal changes to current operating systems. In our scheme, the compiler provides the crucial information on future access patterns without burdening the programmer, the operating system supports non-binding *prefetch* and *release* hints for managing I/O in a virtual memory system, and the operating system cooperates with a run-time layer to accelerate performance by adapting to dynamic behavior and minimizing prefetch overhead. This approach maintains the abstraction of unlimited virtual memory for the programmer, gives the compiler the flexibility to aggressively insert prefetches ahead of references, and gives the operating system the flexibility to arbitrate between the competing resource demands of multiple applications.

We implemented our compiler analysis within the SUIF compiler, and used it to target implementations

of our run-time and operating system support on both research and commercial systems (HURRICANE and IRIX 6.5, respectively). Our experimental results show large performance gains for out-of-core scientific applications on both systems: more than 50% of the I/O stall time has been eliminated in most cases, thus translating into overall speedups of roughly twofold in many cases. Our initial experiments motivated a new compiler scheduling algorithm that is capable of tolerating the large and variable latencies that are common for disk accesses, in the presence of multiply-nested loops with unknown bounds. On our current experimental systems, many of our benchmark applications remain I/O bound, however, we show that the new scheduling algorithms are able to substantially improve performance in some cases, reducing execution time by an additional 36% in the best case. We further show that the new algorithms should enable applications to make more effective use of higher-bandwidth disk systems that will be available in the future.

## Acknowledgements

Graduate school is not an experience that can be survived alone. Having finally reached the end of it, I find that acknowledging everyone that has helped me get here is nearly as daunting as producing the rest of the thesis. There are, of course, some obvious places to start.

First, I would like to thank my advisor, Todd Mowry, whom I hold responsible both for getting me into Ph.D. studies and for ultimately getting me out. This dissertation would not exist without his guidance, support, and continual encouragement. Over the years, I have been the recipient of valuable advice on all matters academic, and though I have not always followed it, I have grown as a researcher, a teacher, and a person as a result. I also thank my thesis committee, M. Satyanarayanan, Garth Gibson, and Monica Lam for their input and guidance on this dissertation and the research behind it.

The implementations of the ideas in this thesis would not have been possible without the help and guidance of the Hurricane team at the University of Toronto (in particular, Orran Krieger and Ben Gamsa) and the SGI Irix developers (especially Luis Stevens who showed me around the internals of the Memory Management Control Interface).

There are a large number of people who made my stay at Carnegie Mellon a unique and enriching experience. I would like to thank all the folks at the Parallel Data Lab, including those who ran the show and those who kept it running. Thanks also to the STAMPede group for providing feedback on research ideas and debugging many practice talks. For laughter and other diversions, I thank Greg and Nancy Steffan, Chris Colohan, Chris Palmer, Carrie Sparks, Jason Flinn, Ted and Addie Wong, Rob O'Callahan, Dave Maltz, Joan Digney, Cheryl Gach and Paul Mazaitis.

Is it possible to thank a department? The environment for computer science research at Carnegie Mellon is phenomenal and far more human than one has any reason to expect. I am sure this is due in no small part to the efforts of Sharon Burks, Associate Department Head and de facto den mother. It is also the result of a dedicated and talented team of support staff who keep the organization running smoothly. Special thanks to the folks in facilities who put up with my personal version of Irix and the extra support it required, and to the folks who supplied me with a spare key to my office so many, many times.

I want to thank friends from before graduate school who have stuck with me and encouraged me through it all. Michelle, Nadine, and Siobain deserve a special thanks for not letting me lose touch with the important things. I am also grateful for the support of my parents, my brother and his family and the world's most wonderful in-laws. Finally, I cannot express how much I owe to my husband Joe, who moved to Pittsburgh and provided patience, love, encouragement and supper while I pursued this degree.

There are so many people who have touched my life during these years as a graduate student, and to whom I owe my heartfelt thanks, that there are surely sins of omission herein. For everyone else not mentioned, please forgive my lapses.

# Contents

| 1 | Intr | duction                                             | 1  |

|---|------|-----------------------------------------------------|----|

|   | 1.1  | Problems with Out-of-Core Applications              | 3  |

|   |      | 1.1.1 Virtual Memory Versus Explicit I/O Interfaces | 3  |

|   |      | 1.1.2 Performance Using Virtual Memory              | 5  |

|   |      | 1.1.3 Impact on Other Applications                  | 7  |

|   | 1.2  | Related Work                                        | 8  |

|   |      | 1.2.1 Prefetching in Virtual Memory Systems         | 9  |

|   |      | 1.2.2 Prefetching for Explicit File Accesses        | 10 |

|   |      | 1.2.3 Integrating Prefetching and Replacement       | 11 |

|   |      | 1.2.4 Compiling Out-of-Core Programs                | 12 |

|   |      | 1.2.5 Application-controlled Memory Management      | 12 |

|   | 1.3  | Research Goals                                      | 13 |

|   | 1.4  | Contributions                                       | 13 |

|   | 1.5  | Overview of Dissertation                            | 15 |

| 2 | Syst | m Design Alternatives and Evaluation Framework      | 17 |

|   | 2.1  | Key Requirements                                    | 18 |

|   | 2.2  | Design Alternatives                                 | 22 |

|   |      | 2.2.1 Potential Sources of Information              | 22 |

|   | 4.1  | Issues   | with Interactive Applications                      | 86 |

|---|------|----------|----------------------------------------------------|----|

| 4 | Perf | ormanc   | e in Multiprogrammed Environments                  | 85 |

|   | 3.4  | Lessor   | as and Limitations                                 | 84 |

|   |      | 3.3.2    | Evaluation of IRIX Implementation                  | 80 |

|   |      | 3.3.1    | Implementation                                     | 78 |

|   | 3.3  | Experi   | ence with a commercial operating system: IRIX      | 78 |

|   |      | 3.2.2    | Evaluation of HURRICANE Implementation             | 62 |

|   |      | 3.2.1    | Operating System and Run-Time Layer Implementation | 58 |

|   | 3.2  | An Ini   | tial Prototype: HURRICANE                          | 58 |

|   |      | 3.1.3    | Compiler Implementation                            | 57 |

|   |      | 3.1.2    | Scheduling Prefetches                              | 49 |

|   |      | 3.1.1    | Locality Analysis                                  | 41 |

|   | 3.1  | Compi    | ler Algorithm                                      | 40 |

| 3 | Imp  | act on ( | Dut-of-core Applications                           | 39 |

|   |      | 2.4.4    | Benchmarks                                         | 38 |

|   |      | 2.4.3    | Commercial System Infrastructure                   | 36 |

|   |      | 2.4.2    | Research System Infrastructure                     | 35 |

|   |      | 2.4.1    | Hardware Platforms                                 | 35 |

|   | 2.4  | Evalua   | tion Framework                                     | 35 |

|   |      | 2.3.3    | The Operating System                               | 33 |

|   |      | 2.3.2    | The Run-Time Layer                                 | 33 |

|   |      | 2.3.1    | The Compiler                                       | 31 |

|   | 2.3  | Actual   | System Design                                      | 30 |

|   |      | 2.2.3    | Options for Communicating Decisions                | 27 |

|   |      | 2.2.2    | Options for Sharing Information                    | 25 |

|   | 4.2 | Altern | atives for Memory Management                           | 88  |

|---|-----|--------|--------------------------------------------------------|-----|

|   |     | 4.2.1  | Global vs. Local Replacement                           | 88  |

|   |     | 4.2.2  | Application-Managed Replacement                        | 89  |

|   | 4.3 | Compi  | ler Support                                            | 91  |

|   |     | 4.3.1  | Complications with Generating <i>Release</i> Requests  | 91  |

|   |     | 4.3.2  | An Example of Data Reuse and the Effect on Releases    | 92  |

|   |     | 4.3.3  | Implementation of Compiler Analysis                    | 93  |

|   | 4.4 | Impler | nentation of Operating System Support for Release      | 95  |

|   |     | 4.4.1  | Setting the Memory Limit                               | 96  |

|   | 4.5 | The R  | un-Time Layer Support                                  | 97  |

|   |     | 4.5.1  | Implementation Details                                 | 99  |

|   | 4.6 | Experi | mental Results                                         | 101 |

|   |     | 4.6.1  | Benchmarks                                             | 101 |

|   |     | 4.6.2  | Performance of the Out-of-Core Applications            | 102 |

|   |     | 4.6.3  | Effectiveness of Releases                              | 106 |

|   |     | 4.6.4  | Impact on Interactive Response Time                    | 109 |

|   | 4.7 | Summ   | ary                                                    | 111 |

| 5 | Imp | roving | the compiler scheduling algorithm                      | 113 |

|   | 5.1 | Schedu | Iling challenges                                       | 114 |

|   |     | 5.1.1  | Variations in Prefetch Distance                        | 114 |

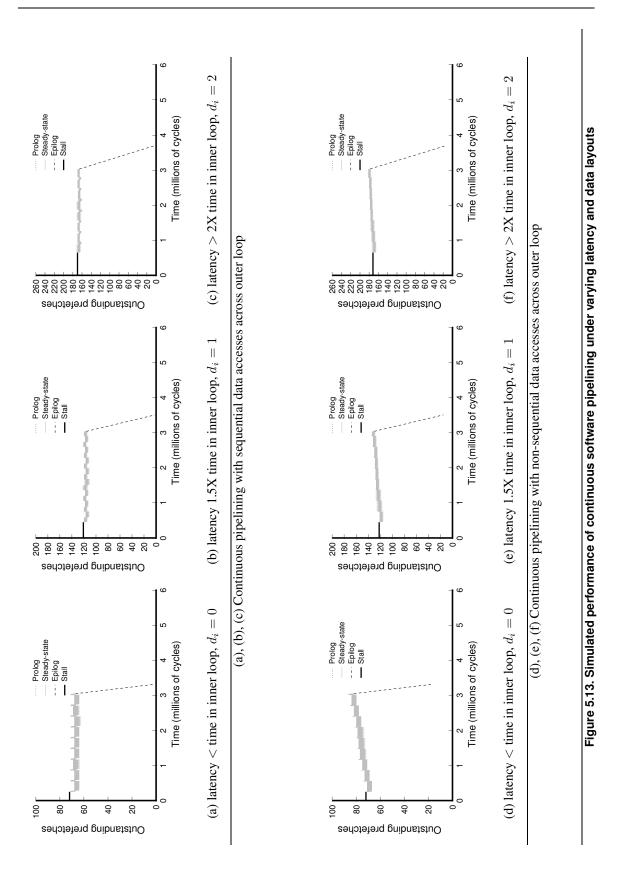

|   |     | 5.1.2  | Problems with nested loops                             | 119 |

|   | 5.2 | Develo | pping the Continuous Software Pipelining Algorithm     | 121 |

|   |     | 5.2.1  | Calculating prefetch distances for multiple loop nests | 121 |

|   |     | 5.2.2  | Nested pipelines                                       | 122 |

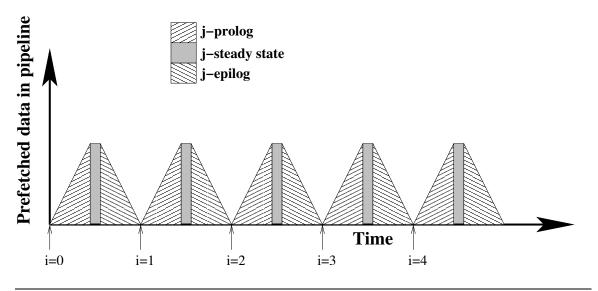

|   |     | 5.2.3  | Merging prologs and epilogs                            | 132 |

|   |     | 5.2.4 Re   | ducing co | de expa  | insio | n   | ••• | ••• | <br>• • | <br> | ••• | • • | <br>• | <br> | • | <br>• | • | <br>• • | 140 |

|---|-----|------------|-----------|----------|-------|-----|-----|-----|---------|------|-----|-----|-------|------|---|-------|---|---------|-----|

|   |     | 5.2.5 Im   | perfectly | nested l | oops  |     | ••• | ••• | <br>    | <br> | •   |     | <br>  | <br> | • | <br>• |   | <br>    | 143 |

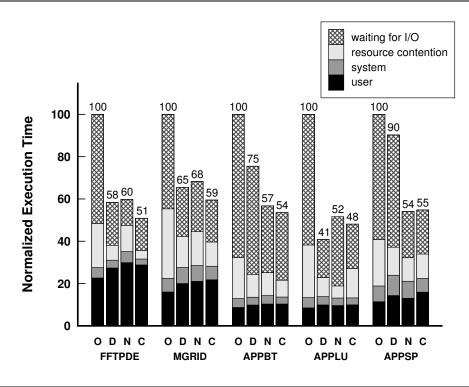

|   | 5.3 | Evaluation |           |          |       | ••• | ••• | ••• | <br>    | <br> | •   |     | <br>  | <br> | • | <br>• |   | <br>    | 146 |

|   | 5.4 | Chapter Su | immary .  |          |       | ••• | ••• | ••• | <br>    | <br> | •   |     | <br>• | <br> |   | <br>• |   | <br>    | 150 |

| 6 | Con | clusions   |           |          |       |     |     |     |         |      |     |     |       |      |   |       |   |         | 153 |

|   | 6.1 | Future Wo  | rk        |          |       | ••• | ••• | ••• | <br>    | <br> | ••  |     | <br>• | <br> | • | <br>• |   | <br>    | 154 |

|   | 6.2 | Final Obse | rvations  |          |       |     |     |     | <br>    | <br> |     |     | <br>  | <br> |   |       |   | <br>    | 156 |

# **List of Figures**

| 1.1 | Virtual memory performance on two systems for in-core and out-of-core problem sizes           | 5  |

|-----|-----------------------------------------------------------------------------------------------|----|

| 1.2 | Time to touch 1MB of data for varying <i>think times</i> between accesses                     | 7  |

| 2.1 | Improving demand paging performance                                                           | 19 |

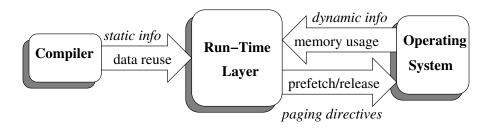

| 2.2 | Information flow between components of our system.                                            | 26 |

| 2.3 | Example illustrating the importance of non-binding prefetches                                 | 28 |

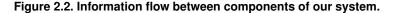

| 2.4 | Steps in the automatic transformation of original application into prefetching/releasing exe- |    |

|     | cutable                                                                                       | 31 |

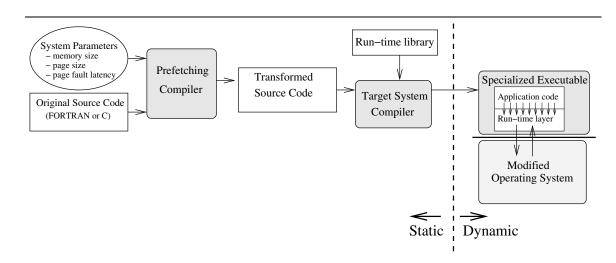

| 3.1 | Data reuse example                                                                            | 43 |

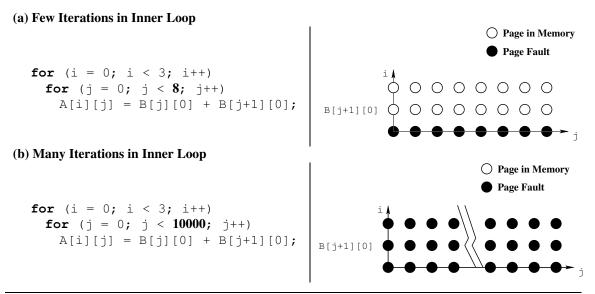

| 3.2 | Example of how loop iteration counts affect locality.                                         | 45 |

| 3.3 | Example of how prefetch predicates are constructed.                                           | 48 |

| 3.4 | Example of peeling the first and last iterations of a loop                                    | 50 |

| 3.5 | Example of unrolling and strip-mining a loop by a factor of 64                                | 50 |

| 3.6 | Example of how software pipelining is used to schedule prefetches the proper amount of time   |    |

|     | in advance. For this example, 12,288 iterations are required to hide I/O latency.             | 53 |

| 3.7 | Example of Software Pipelining with Small Loop Bounds.                                        | 55 |

| 3.8  | Example of the output of the prefetching compiler. (The first argument to all prefetch calls                                 |    |

|------|------------------------------------------------------------------------------------------------------------------------------|----|

|      | is the prefetch address; the second argument to prefetch_release_block is the release                                        |    |

|      | address; the final argument to "block" versions is the number of 4KB pages to be fetched                                     |    |

|      | and/or released.)                                                                                                            | 57 |

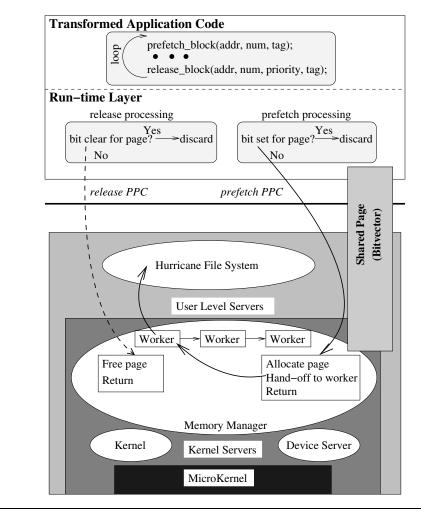

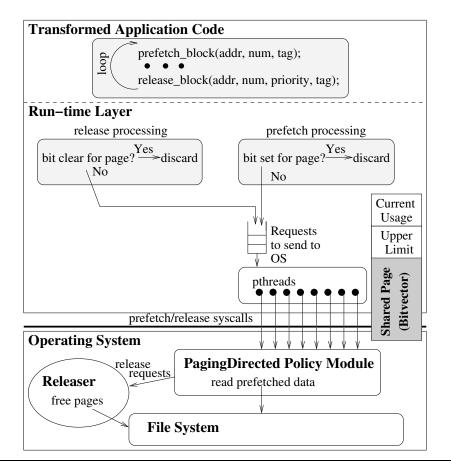

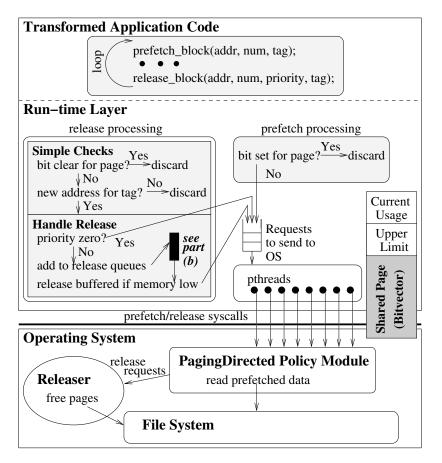

| 3.9  | Implementation of prefetching and releasing support on HURRICANE.                                                            | 59 |

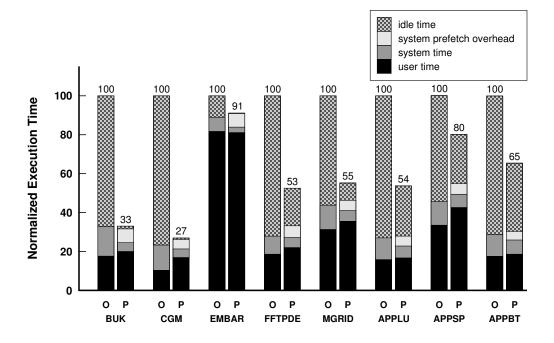

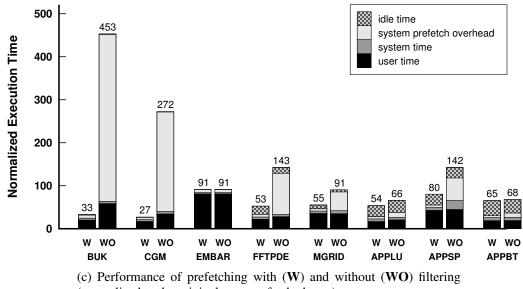

| 3.10 | Overall performance improvement from prefetching on HURRICANE                                                                | 63 |

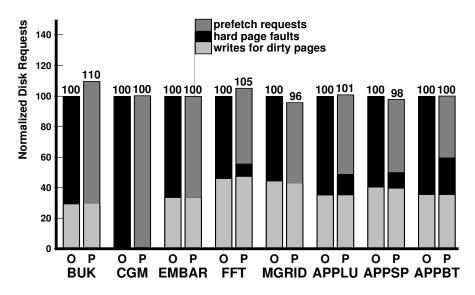

| 3.11 | Impact of prefetch and release on system resources on HURRICANE                                                              | 65 |

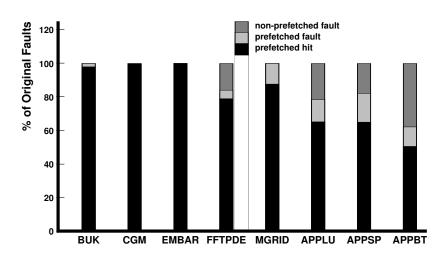

| 3.12 | Effectiveness of the compiler analysis and run-time filtering                                                                | 67 |

| 3.13 | Example of a reference not recognized as an array reference (inside foo) by the compiler. $% f(t)=\int_{t}^{t} f(t) dt$ .    | 69 |

| 3.14 | Example of reuse not identified by the compiler                                                                              | 70 |

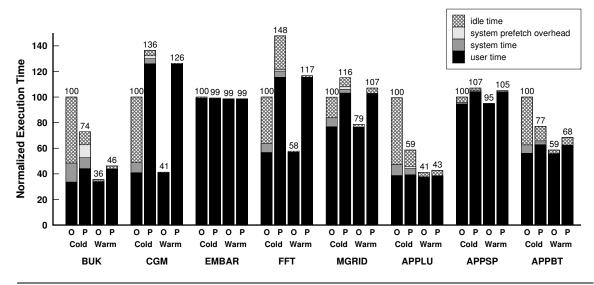

| 3.15 | Performance with in-core data sets ( $\mathbf{O}$ = original, $\mathbf{P}$ = with prefetch; $\mathbf{Cold}$ = cold-started,  |    |

|      | <b>Warm</b> = warm-started). Performance is normalized to the original, cold-started cases                                   | 72 |

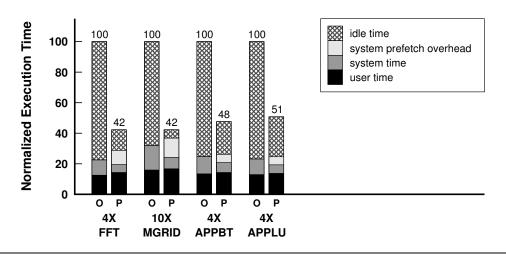

| 3.16 | Performance with larger out-of-core problem sizes. Numbers above application names indi-                                     |    |

|      | cate how much larger the problem sizes are than available memory                                                             | 73 |

| 3.17 | Source code (C representation) for BUK                                                                                       | 75 |

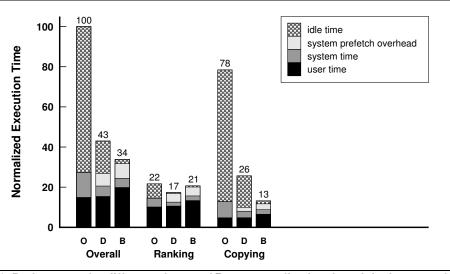

| 3.18 | Performance for different phases of BUK, normalized to the original, non-prefetching case                                    |    |

|      | ( $\mathbf{O}$ = original, $\mathbf{D}$ = with direct-only prefetching, $\mathbf{B}$ = with direct and indirect prefetching) | 76 |

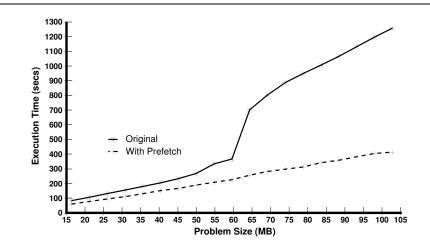

| 3.19 | Performance of BUK (cold-started) across a range of problem sizes                                                            | 77 |

| 3.20 | Implementation of prefetching and releasing support on IRIX                                                                  | 78 |

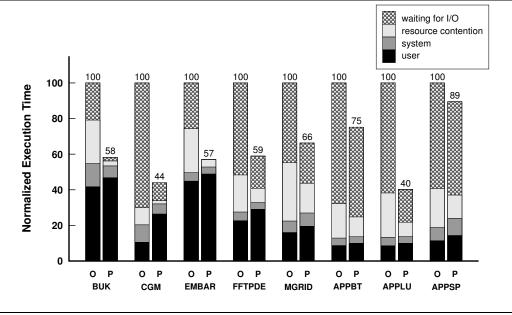

| 3.21 | Overall performance improvement from prefetching and releasing on IRIX ( $\mathbf{O}$ = original, $\mathbf{P}$ =             |    |

|      | with prefetching and releasing).                                                                                             | 81 |

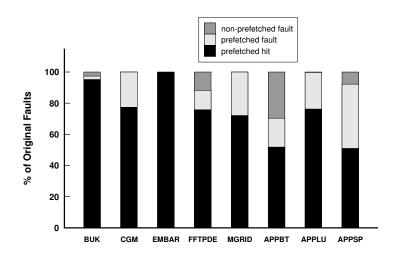

| 3.22 | Impact of prefetching on the original page faults under IRIX                                                                 | 83 |

| 4.1  | Impact of sharing the machine with an out-of-core matrix-vector multiplication (MATVEC)                                      |    |

|      | on the response time of an interactive task across a range of sleep times between touching 1                                 |    |

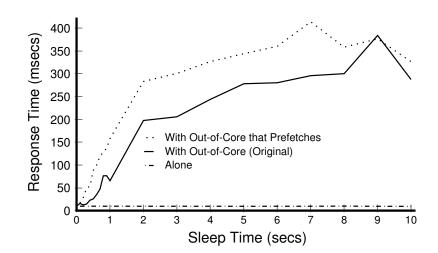

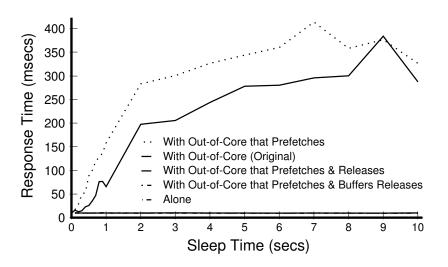

|      | MB of data.                                                                                                                  | 87 |

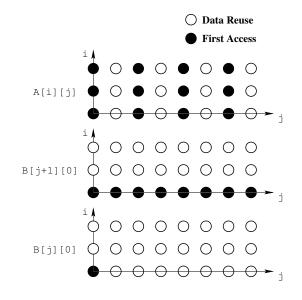

| 4.2  | Example source code showing multiple references with different types of reuse, and graphical                                               |     |

|------|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

|      | view of the data accesses during a single iteration of the innermost loop                                                                  | 92  |

| 4.3  | Example of the output of the prefetching compiler. Arguments are: (prefetch address, release                                               |     |

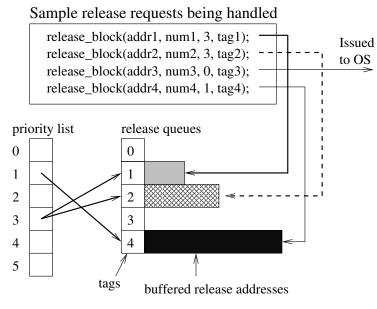

|      | address, number of 16KB pages, release priority, request identifier)                                                                       | 95  |

| 4.4  | Handling prefetches and releases at run-time.                                                                                              | 98  |

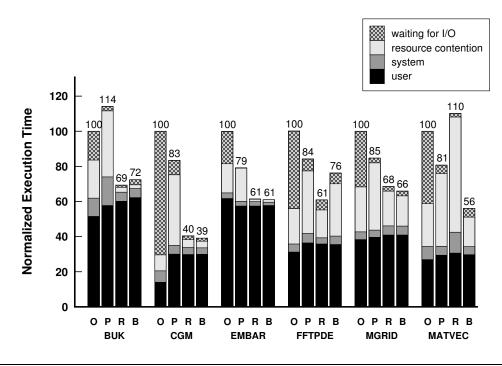

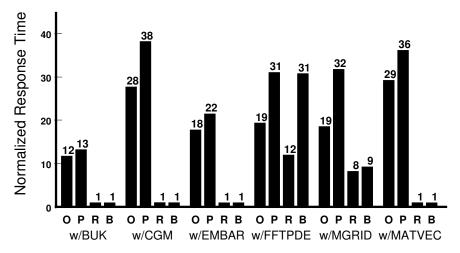

| 4.5  | Impact of prefetching and releasing on the execution times of the out-of-core applications.                                                |     |

|      | ( $\mathbf{O}$ = original, $\mathbf{P}$ = with prefetching, $\mathbf{R}$ = with prefetching and releasing, $\mathbf{B}$ = with prefetching |     |

|      | and release buffering)                                                                                                                     | 103 |

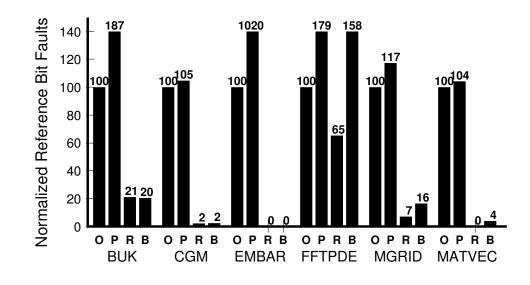

| 4.6  | Soft page faults due to page invalidations.                                                                                                | 105 |

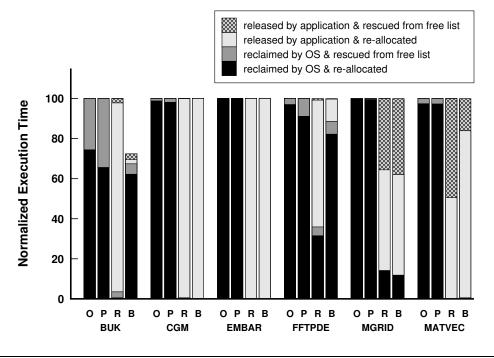

| 4.7  | Breakdown of outcomes for freed pages.                                                                                                     | 108 |

| 4.8  | Impact of releasing on interactive response time                                                                                           | 110 |

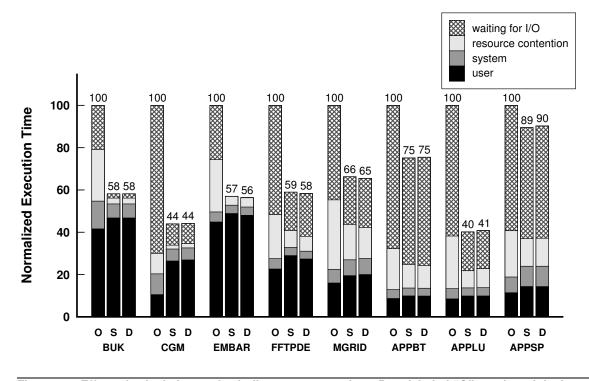

| 5.1  | Effect of calculating prefetch distances at run-time. Bars labeled "O" are the original, non                                               |     |

|      | prefetching version; bars labeled "S" use a static compile-time latency; bars labeled "D" use                                              |     |

|      | a dynamic latency value (equal to the static value) obtained at run-time                                                                   | 117 |

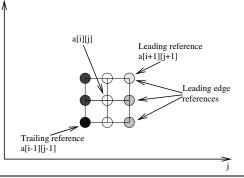

| 5.2  | Adding prefetches for two-dimensional array accesses                                                                                       | 120 |

| 5.3  | Algorithm for calculating prefetch distances in nested loops.                                                                              | 122 |

| 5.4  | Sample code for software pipelining a single loop with multiple loop index offsets                                                         | 122 |

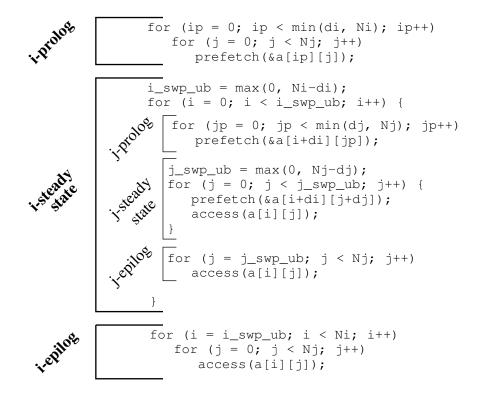

| 5.5  | Nested software pipelines for two-dimensional array prefetches                                                                             | 123 |

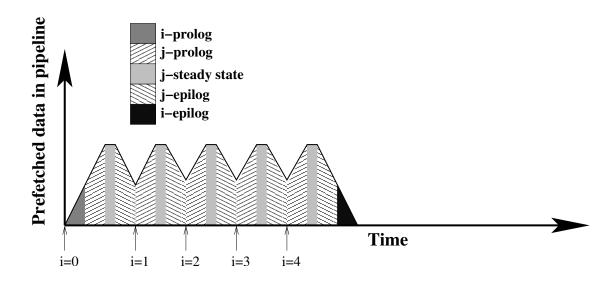

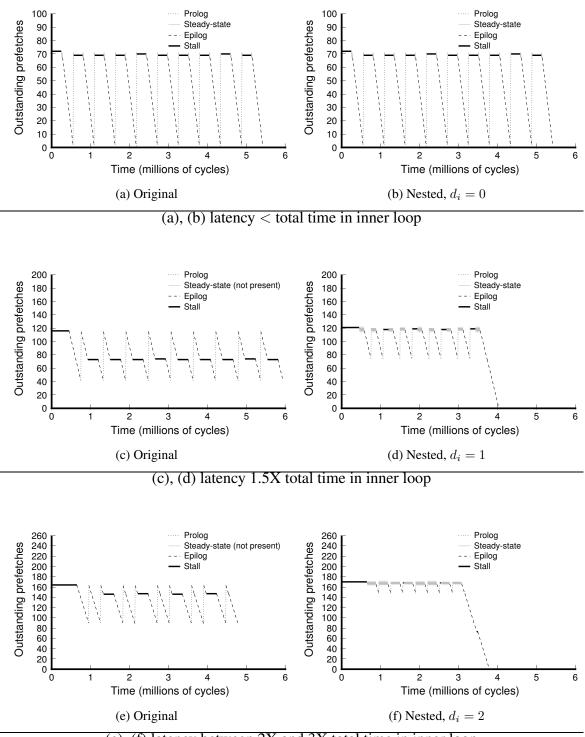

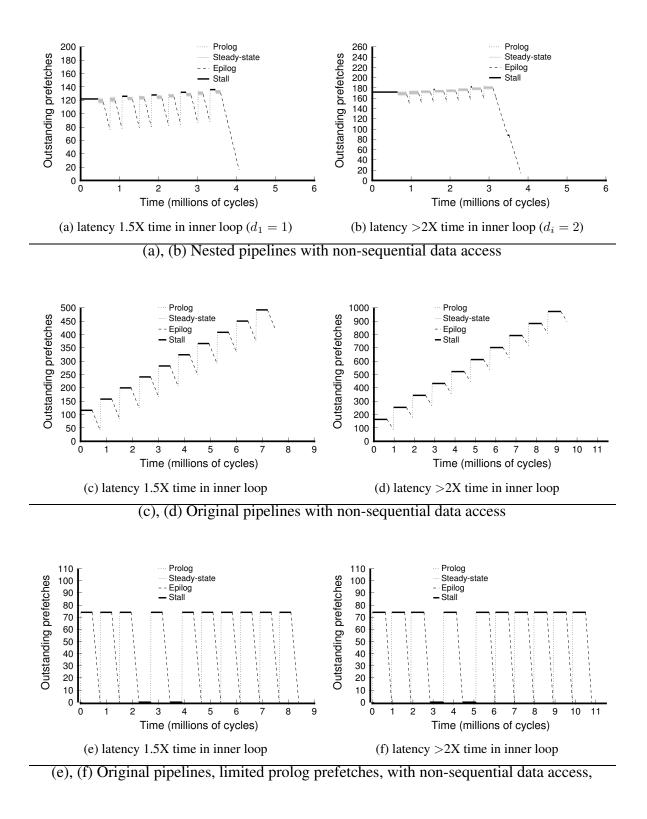

| 5.6  | Comparison of nested pipelining vs. original single-loop pipelining for different latency values                                           | 127 |

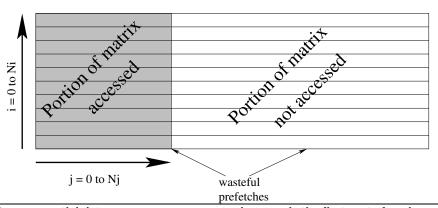

| 5.7  | Non-sequential data accesses across outer loop: only the first part of each row of matrix is used                                          | 128 |

| 5.8  | Effect of non-sequential data access across outer loop                                                                                     | 130 |

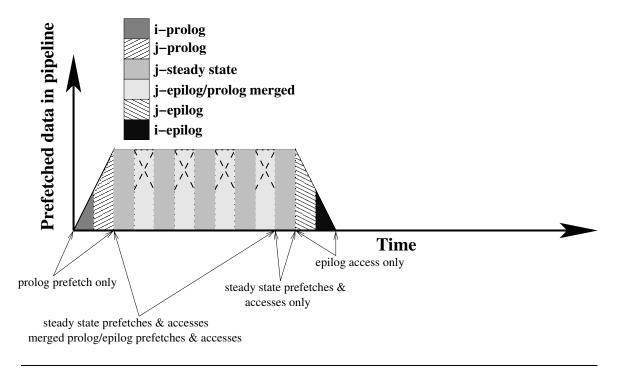

| 5.9  | Continuous software pipelines for two-dimensional array prefetches                                                                         | 131 |

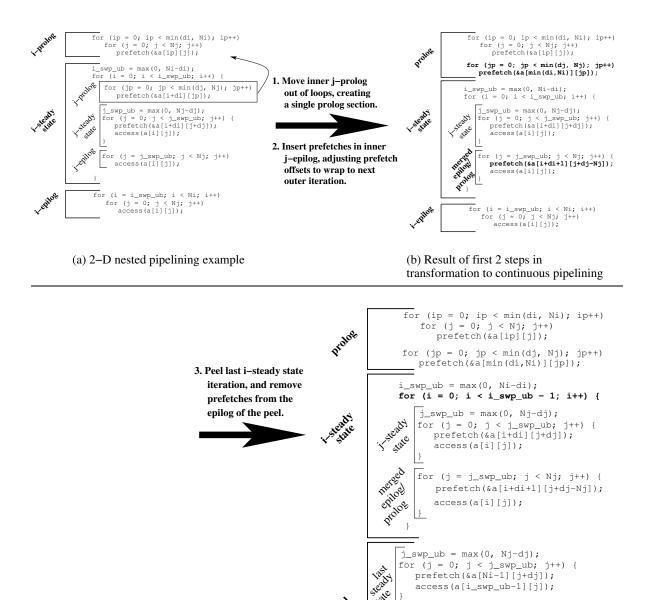

| 5.10 | Progression from Nested pipelines to Continuous pipelines                                                                                  | 133 |

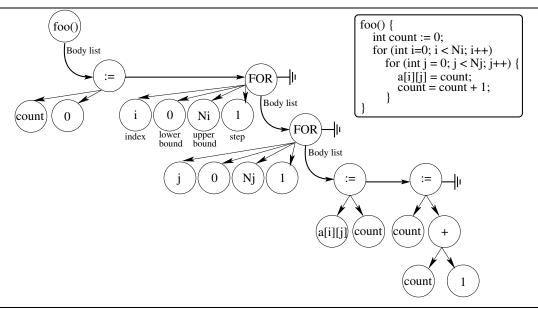

| 5.11 | SUIF-style abstract syntax tree for simple procedure with loops                                                                            | 134 |

| 5.12 | Algorithm for building continuous software pipelines in nested loops                                                                       | 137 |

| 5.13 | Simulated performance of continuous software pipelining under varying latency and data              |

|------|-----------------------------------------------------------------------------------------------------|

|      | layouts                                                                                             |

| 5.14 | Wrapped pipeline: only two copies of the original loop body are needed to cover all situations. 141 |

| 5.15 | Example of imperfect loop nesting structure found in blts subroutine of applu.f 145                 |

| 5.16 | Effect of new scheduling algorithms. Bars labeled "O" are the original, non prefetching             |

|      | version; bars labeled "D" use a dynamic latency value with the original scheduling algorithm;       |

|      | bars labeled "N" use the nested pipelining algorithm; bars labeled "C" use the continuous           |

|      | pipelining algorithm                                                                                |

# **List of Tables**

| 2.1 | Available Information Sources                                                                 | 22  |

|-----|-----------------------------------------------------------------------------------------------|-----|

| 2.2 | HECTOR/HURRICANE characteristics                                                              | 36  |

| 2.3 | SGI Origin 200 characteristics                                                                | 37  |

| 2.4 | Description of applications.                                                                  | 37  |

| 3.1 | Comparing compiler input parameters for cache prefetching vs. I/O prefetching                 | 40  |

| 3.2 | Application characteristics on HURRICANE.                                                     | 62  |

| 3.3 | Application characteristics on IRIX                                                           | 81  |

| 4.1 | Description of applications.                                                                  | 101 |

| 4.2 | Pages freed by system or by release, and pages rescued from the free list                     | 107 |

| 5.1 | Graduated instructions for static and dynamic prefetch distance calculations (millions of in- |     |

|     | structions)                                                                                   | 118 |

| 5.2 | Properties used in presenting continuous pipelining algorithm                                 | 135 |

| 5.3 | Additional procedures used in presenting continuous pipelining algorithm                      | 135 |

| 5.4 | Effect of pipelining algorithms on code size and execution time                               | 142 |

| 5.5 | Simulated performance characteristics                                                         | 146 |

### **Chapter 1**

## Introduction

640K should be enough for anyone. — Bill Gates

Out-of-core applications are here to stay. Programs with data sets that exceed the size of main memory are easy to find, despite the exponential growth in memory capacity. Examples can be drawn from many branches of computer science including artificial intelligence, computational linguistics, databases, graphics, and scientific computing. For the "Grand Challenge" applications of science and engineering the need for more memory appears to be essentially unbounded. For instance, input data sets for scientific visualization can currently exceed 100 gigabytes [19], while the storage requirements for computational biology tasks like protein structure prediction can be measured in petabytes [57]. These types of problems have long been the driving force behind advances in supercomputing, yet as faster processors and massively parallel machines make it possible to solve problems that were computationally infeasible in the past, the demands on the memory system also scale at a commensurate pace.

For these memory-intensive applications, we can expect that disk drives will continue to form the backbone of the memory hierarchy, providing stable, cost-effective, mass storage. I/O will be required throughout the computation, both to bring the required data into main memory and to write intermediate results out to disk. Unfortunately, although advances in magnetic storage technology have led to dramatic increases in disk drive capacity and throughput, the average access time has not improved significantly. Given the large (and increasing) gap between processor speeds and disk latencies, it is expected that out-of-core programs will spend a substantial portion of their execution time waiting for I/O. If we hope to leverage more powerful processors to solve the scientific computing problems of the future, we clearly need techniques to manage the I/O requirements of these programs.

One effective technique to reduce the time spent waiting for I/O is *prefetching*. By requesting data before it is needed, the I/O latency can be overlapped with other computation, resulting in dramatic reductions in the overall execution time. Successful prefetching, however, depends critically on determining what data should be prefetched and when the prefetch should be initiated. Because making these decisions manually represents a substantial burden on the application programmer, this thesis explores automated techniques, which are based in static compiler analysis, for obtaining the required information.

In addition to suffering from large I/O latencies, out-of-core tasks are also extremely bad neighbors in a multiprogrammed environment, yet executing them in such a setting is desirable for a number of reasons. It is not only more cost-effective to be able to share machine resources between an out-of-core application and other programs, it may also be necessary for some applications such as a visualization task that is enabling the user to interactively guide a physical simulation in real-time. Unfortunately, operating on massive data sets consumes physical resources (memory and disk bandwidth) at a rapid rate, thereby potentially displacing the working sets of other applications and increasing their page fault service times. To make matters worse, the performance gains achieved if prefetching for out-of-core applications is successful will cause physical resources to be consumed at an even faster rate, increasing the negative impact on other applications. A key observation is that the excessive resource consumption by out-of-core tasks is not the result of their inherent resource requirements. It can instead be attributed to resource management policies in the operating system that are not well suited to this class of applications. For instance, global page replacement policies perform well in the general case, but allocate too many pages to an out-of-core program that is sweeping though its data set rapidly.

Good overall performance in a multiprogrammed workload with out-of-core applications depends on making the right decision about what data should be replaced from memory to make room for the prefetched data. Thus, in this thesis we also evaluate the use of compiler analysis to guide replacement decisions. For both prefetching and replacement, we show that static analysis alone is insufficient in many cases, and must be coupled with a run-time system capable of adapting to dynamic conditions if performance improvements are to be realized.

We begin the rest of this chapter by taking a closer look at the performance problems experienced and caused by out-of-core programs before summarizing other approaches for managing I/O. We then describe our research goals, list the major contributions of this thesis, and end with an overview of the remaining chapters.

#### 1.1 Problems with Out-of-Core Applications

Given that applications with extremely large data sets will require I/O throughout their execution, there are two primary approaches that could be used—either manage the I/O explicitly through read and write system calls, or rely on the operating system (via paged virtual memory) to fetch and replace data as needed. These traditional solutions force the programmer to choose between performance and ease-of-use.

#### 1.1.1 Virtual Memory Versus Explicit I/O Interfaces

Using virtual memory to handle intermediate I/O requirements has one enormous advantage over explicit I/O calls—it is easy to use. Programs that were written assuming the data set would fit in memory need no modification (other than increasing the size of relevant parameters and data structures) to scale them up to larger (out-of-core) problem sizes. Programmers writing new applications can focus on the problem they are trying to solve, without regard to the I/O requirements of their programs. For instance, algorithms can be chosen for their numerical stability, rather than to minimize the number of disk accesses required. Unfortunately, the abstraction of paged virtual memory is not transparent with regard to performance: it is painfully obvious when the physical memory boundary has been crossed. Worse, although paging clearly degrades performance, the programmer cannot easily address these problems as paging decisions are controlled by the operating system.

There are essentially two reasons why paged virtual memory typically has poor performance: the timing

of requests, and the size of requests. First, disk requests are initiated in response to a page fault. That is, the I/O is initiated when the application needs the data, forcing the application to stall for the full latency of a disk read before it can continue. Second, each page fault typically brings only a page-sized chunk of data into memory at a time. Even if we construct an extremely high-bandwidth disk array, and stripe our data across all the disks, we cannot exploit this extra bandwidth since only a single disk is ever active at any time.

These performance problems can be addressed by explicit I/O calls as follows. First, the non-blocking I/O calls provided by asynchronous I/O interfaces allow an application to hide latency by overlapping disk I/O with computation. Second explicit I/O calls can fetch a large number of blocks in a single request, which is important to fully exploit the underlying parallelism in high-bandwidth I/O systems (e.g., disk arrays).

While explicit I/O offers the potential for improved performance over paging, it unfortunately suffers from several disadvantages. The primary disadvantage is the large burden placed on the programmer of rewriting an application to insert the I/O calls—one goal of this thesis is to avoid placing additional burdens on the programmer altogether. Another disadvantage is the performance overhead of these I/O system calls, which typically involve copying overhead to transfer data between the system's I/O buffers and the buffers managed by the application.

A third, less obvious disadvantage is that with explicit I/O, the application is implicitly making lowlevel policy decisions with its I/O requests (e.g., the size of the requests, and the amount of memory to be used for I/O buffering). However, the best policy decisions depend not only on application access patterns, but also on the physical resources available. Hence an application written assuming a particular amount of physical memory and disk bandwidth may perform poorly on a machine with a different set of resources, or in a multiprogrammed environment where some of the resources are being used by other applications. To illustrate how the available physical resources affect an application's performance, consider the amount of memory available for buffering I/O. If sufficient physical memory is available such that the entire data set can fit in memory, then an application with explicit I/O will pay the system call overhead with no benefit. On the other hand, if the application uses more buffer space for I/O than the available physical memory, then the buffers will suffer page faults, possibly resulting in worse performance than if the application had simply

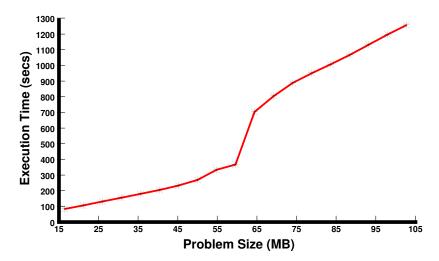

(a) Performance of BUK on a research operating system (HURRICANE) using virtual memory for I/O

(b) Performance of BUK on a commercial operating system (IRIX) using virtual memory for I/O Figure 1.1. Virtual memory performance on two systems for in-core and out-of-core problem sizes.

#### relied on paged virtual memory from the start.

#### 1.1.2 Performance Using Virtual Memory

The simplicity of the virtual memory programming model makes it an extremely appealing interface to target, if the performance difficulties can be overcome. To illustrate some of the challenges we present an example of an out-of-core application that uses virtual memory for I/O. More details on this benchmark and the experimental setup will be given later in Section 2.4.4, with only the most relevant characteristics presented here.

Figure 1.1 shows the total execution time for a single benchmark from the NAS Parallel suite [6], across a range of data set sizes, on two very different systems. The benchmark is BUK: a bucket-sort algorithm with computation that scales linearly with the problem size. If physical memory were unlimited, we would expect the performance curve to be a straight line. Instead, on both systems a large increase in the execution time can be seen when the physical memory is exhausted and paging is needed. Results on HURRICANE, a research operating system designed for large-scale multiprocessors [56], are shown in Figure 1.1(a). On this system, every page fault pays the full cost of a disk access and the effect on performance at out-of-core problem sizes is severe.

Although it would be easy to dismiss the HURRICANE results as an artifact of a research prototype, this is not the case. Figure 1.1(b) shows the same benchmark (with different problem sizes) on a modern, commercial operating system (Irix 6.5). Despite large disk buffers, and disk controller read-ahead policies for sequential data [45], it is still easy to discern the memory boundary from the performance curve even though over two thirds of the references in BUK are sequential array accesses! The remaining accesses in BUK are essentially random, and the large gap between disk latency and processor performance makes them extremely costly. Furthermore, the disk read-ahead policies may be defeated by a lack of control over the mapping of pages to disks and the order in which page faults occur. That is, even though a particular data structure may be accessed sequentially in the program code, there is no guarantee that the accesses seen by a particular disk will also be sequential.

To successfully prefetch page faults it is necessary to determine which pages will be needed in the future. Although automatically detecting access patterns at run-time is conceptually appealing, in practice it is extremely difficult. Indirect references (such as those found in sparse-matrix codes) lead to random accesses which are not predictable by pattern detection. Even when patterns exist, as in regular strided or stencil matrix codes, interleaving of accesses from multiple data structures can obscure these patterns at run-time. Finally, as the BUK example illustrates, detecting sequential accesses is not sufficient. To make matters worse, prefetching based on pattern detection can actually hurt performance when the future accesses do not conform to the previously detected pattern. Mis-predicted prefetches are costly because they displace

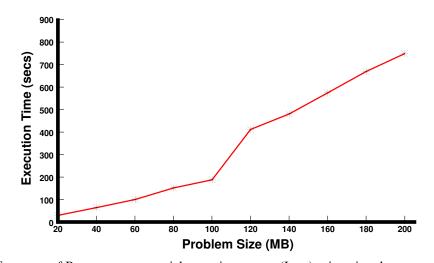

Figure 1.2. Time to touch 1MB of data for varying *think times* between accesses.

other pages from memory without providing any benefit. Smith refers to this effect as *memory pollution* and observes that it worsens with increasing page sizes [48].

This thesis presents an alternative method for predicting which pages will be needed in the future based on static analysis techniques that have the potential to automatically detect access patterns at compile-time. Given knowledge of the access pattern, it is also possible to statically transform the program to insert memory management primitives, such as prefetch instructions for data references that are expected to incur page faults. Such compiler-based techniques have been successfully applied in the past to the problem of predicting cache misses and prefetching data from main memory into the processor cache [39,41]. Since physical memory can be viewed as just another level in the memory hierarchy, it is natural to consider applying these methods to the problem of prefetching data from disks into memory. Section 2.3 presents our design for a system that combines static analysis with dynamic adaptation, while Chapter 3 evaluates how well this design improves the performance of out-of-core applications on a dedicated machine.

#### **1.1.3 Impact on Other Applications**

As noted earlier in this chapter, out-of-core applications can hurt the performance of other programs by displacing their working sets from memory. The negative effect of out-of-core applications on other applications is most distressing for interactive programs where a human user is able to perceive an increase in response time. Ironically, these interactive programs are also particularly susceptible since they spend most of their execution time waiting for user input, and are unable to defend their memory pages. Figure 1.2 shows the results of a simple experiment that demonstrates the magnitude of the problem.

In this experiment, we simulate the memory reference behavior of an interactive task by executing a simple program that responds to *requests* by touching a portion of its data set. Requests are separated by some fixed amount of *think time* representing delays between input from a user. The measured response time is the amount of time required to touch the data set, and should be a constant independent of *think time* if the pages of the data set remain in memory between accesses. This simple program is executed both (i) alone on the machine and (ii) with an unmodified out-of-core program (in this case, a large matrix-vector multiply that consumes memory rapidly).

As can be seen from Figure 1.2, when the interactive program executes on a dedicated machine, its response time is indeed uniform as *think time* ranges from 0 to 10 seconds (see the line labeled "*Alone*"). When a non-prefetching out-of-core program is executed concurrently, however, the response time increases dramatically, even for relatively short *think times* of 1-5 seconds, as shown by the "*With out-of-core*" line. Employing prefetching to improve the performance of the out-of-core program only serves to make the situation worse for the interactive task.

In this thesis we argue that the responsibility for reducing the negative impact of the out-of-core program should rest with the out-of-core program itself, since it is the source of the problem. By leveraging the same static analysis that supports prefetching decisions, the compiler can identify pages that may be good candidates for replacement, thus reducing the need to steal pages from other applications. The effect of explicitly releasing memory on the out-of-core program is studied in Chapter 3, while the overall effects in a multiprogrammed environment are the subject of Chapter 4.

#### **1.2 Related Work**

The general problems of hiding disk latency through prefetching, and improving the memory performance of data-intensive applications have been well studied in the past in a variety of forms. In this thesis we focus on techniques with a strong operating system or compiler component; although there is a large body of research on algorithms for out-of-core computations, we will not discuss them here since we are not modifying the program's algorithm. Our techniques can be applied to hide the I/O latency in an out-of-core program after the most suitable algorithm for the problem has been chosen.

Related research can be classified into five broad areas: (i) prefetching of page faults in virtual memory systems; (ii) prefetching of explicit file accesses; (iii) combining prefetching and replacement decisions; (iv) compilation for out-of-core programs; and (v) application-controlled memory management. We will discuss each of these areas in turn.

#### **1.2.1** Prefetching in Virtual Memory Systems

Over twenty years ago, Trivedi presented a strategy for automatically extracting application access patterns in looping programs using a compiler [55]. The detected patterns were used to implement *prepaging*, which included directives to fetch particular pages into physical memory, and replace other pages. At a high level, this work is very similar to the scheme presented in this thesis, with two important differences. First, advances in compiler technology have greatly expanded the range of applications that can be handled. Trivedi's compiler analysis was restricted to programs in which blocking could be performed whereas previous studies on prefetching for caches have shown that many programs which can be prefetched cannot be blocked [41]. Second, the introduction of a run-time layer to filter unnecessary hints allows the compiler to act much more aggressively, further increasing the situations in which prefetching and releasing memory can be applied successfully.

Other work in the area of prefetching for paged virtual memory systems generally depends on the operating system being able to detect patterns to initiate prefetching. Curewitz, Krishnan, and Vitter investigated using techniques developed for data compression to predict what to prefetch [20]. In their design a *prefetcher* examines a database client's previous page requests and issues prefetch requests to the database server. They note that prediction accuracy is better when a separate prefetcher is used for each instance of a client application, since user access patterns can vary widely. In a similar vein, Song and Cho use the fault history to detect patterns and initiate prefetching [49]. Pattern-based prediction techniques all suffer from the fact that some number of faults are required to establish patterns before prefetching can begin. Worse, mis-predictions are likely to occur when the patterns change, leading to potentially harmful memory pollution.

Much of the work on automated page fault prefetching has been done in the context of distributed shared memory systems, where pages are fetched from remote memories rather than from local disks. Representative examples include [7, 50, 63]. Network latencies in these settings are typically much smaller, and hence easier to hide, than disk latencies. The fundamental issue is that mis-predictions increase with the latency. Techniques which are successful at hiding network latency are likely to cause too much memory pollution when applied to the problem of hiding disk latency. In contrast, techniques that are successful for disk prefetching can also be used to hide smaller network latencies in a distributed shared memory system.

A final option for virtual memory prefetching makes use of the *madvise* system call, provided by some UNIX operating systems. This system call allows a programmer to give advice such as MADV\_WILLNEED or MADV\_DONTNEED for ranges of the virtual address space. While this is conceptually similar to the operating system interface we present, it relies on the programmer to manually provide information about the memory usage of their program. In addition, even when the interface is provided, many operating systems make no claims about how the advice will be handled—it may simply be ignored. Thus the utility of the interface, by itself, is quite limited.

#### **1.2.2** Prefetching for Explicit File Accesses

Prefetching in file systems by automatically detecting file access patterns has been well studied [3, 24, 25, 28, 32, 34]. Kroeger and Long look at using the compression technique known as *prediction by partial match* to detect access patterns and to decide what to prefetch [34]. Griffioen and Appleton construct a *probability graph* based on prior file system accesses [24]. Both approaches attempt to improve the performance of the overall file system by predicting which *files* are likely to be referenced next when a particular file is opened. In contrast, our focus is on improving performance for out-of-core applications that typically access a small number of very large files, and/or have many accesses to the swap file. Kotz and Ellis studied prefetching

when a program's dynamic access patterns matched one of eight access patterns commonly found in parallel applications [32]. Once again, techniques that depend on being able to detect an access pattern cannot prefetch until the pattern has been established and may do the wrong thing when the pattern changes. In addition, the access patterns may be extremely difficult to detect automatically, or may not match the pre-selected set of possible patterns.

Another technique implemented in file systems is to support prefetching based on information supplied explicitly by the application. One such approach is the TIP system, developed by Patterson et al. [43], which considers both prefetching and caching, and will be discussed in the following section.

#### 1.2.3 Integrating Prefetching and Replacement

The importance of considering both prefetching and replacement decisions in tandem has been studied by several groups in the context of I/O prefetching and caching for file system references. Cao *et al.* [11] present several properties that optimal prefetching and caching strategies must have, however the complete reference stream is required to satisfy these properties. The TIP system for I/O prefetching by Patterson *et al.* [43] uses a cost-benefit model to estimate which file blocks should be replaced from the buffer cache, based on access-pattern hints disclosed by the application. While the goal of using application-specific knowledge to improve overall system performance is the same as in our system, we focus on virtual memory references rather than file reads and writes. Because it is much more costly to track all virtual memory references (versus explicit file requests only) the techniques applied by the TIP system for determining what to eject from the file cache are not especially applicable for virtual memory management decisions.

In the original TIP implementation, applications had to be manually modified to generate the necessary access hints. Recently, another approach for automatically modifying applications (using a binary modification tool on the program executable) to provide hints about their future accesses has been presented by Chang and Gibson [12]. Applications are altered to speculatively execute their code for the purpose of discovering future read requests, which can be passed as hints to the TIP system.

Vellanki and Chervenak used cost-benefit analysis similar to TIP, however prefetch decisions were made

using a markov-based predictor built from past disk access history [58]. Their scheme suffers from the same limitations as other approaches that use past access patterns to derive future predictions. Finally, Voelker *et al.* present a hybrid approach that uses both disk and network memory prefetching [59]. They assume that future accesses are fully known (either through TIP-style application hints, or some other method) and adapt the *Forestall* algorithm of Kimbrel *et al.* to consider both types of prefetching. Although their results demonstrate that prefetching can be successfully applied to hide multiple kinds of latency at the same time, they do not address the question of deciding what to prefetch when full knowledge of future accesses is not available.

#### 1.2.4 Compiling Out-of-Core Programs

Compiling for out-of-core codes tends to focus on three areas. The first area is reordering computation to improve data reuse and reduce the total I/O required [9]. The second area is inserting explicit I/O calls into array codes [16, 31, 42, 54]. In general, the compilers are aided by extensions to the source code that indicate particular structures are out-of-core. In addition, some of the work specifically targets I/O performance for parallel applications [9], while we aim to improve the performance of even single-threaded applications. The third compilation approach is to take programs that already contain explicit I/O calls, move them to an earlier program point, and change them to asynchronous I/O calls instead. However, asynchronous I/O calls cannot be issued unless it is known that the data being read will not be modified between the asynchronous call, and the point of the original read. Aliasing can complicate the compiler's ability to determine the safety of changing synchronous reads into asynchronous ones at an earlier time, and limits the opportunities available for applying this transformation. In contrast, prefetching based on a virtual memory interface can be applied at any time, even if all aliases cannot be resolved.

#### 1.2.5 Application-controlled Memory Management

Many researchers have suggested that better performance can be obtained if sophisticated applications are given control over their own memory management decisions. Most previous work in this area has focused on how the operating system can provide this functionality to the applications. For instance, the Mach operating system supports external pagers to allow applications to control the backing storage of their memory objects [44]. Extensions to the external pager interface have been used to implement user-level page replacement policies [38] and to support discardable pages (i.e., dirty pages that do not have to be written to backing store) [51]. More aggressive application control of physical memory was implemented in the V++ kernel by Harty and Cheriton [27]. In their scheme, the application was given complete control over a cache of physical pages, enabling the implementation of application-specific memory management policies. Giving applications more control over physical resources (not just memory) is also a part of the motivation behind extensible operating systems such as Exokernel [30], SPIN [8], and Vino [47].

Providing support for application-specific control is only half of the picture, however. If the mechanisms provided require programmers to re-write their applications manually, the full power of the scheme is unlikely to be realized in the real world. In contrast, our approach provides not only the mechanisms for application-controlled memory management, but also a means to leverage these mechanisms automatically through the use of the compiler.

#### **1.3 Research Goals**

At the highest level, the goal of this thesis is to demonstrate the following statement:

A combination of I/O prefetching and page replacement hints inserted by automatic compiler analysis and transformation can successfully hide the latency of page faults in outof-core programs while simultaneously reducing the negative impact on the performance of other programs in a multiprogrammed environment. Adaptation to run-time conditions can be achieved by a user-level software layer which synthesizes information provided by the compiler and the operating system to perform memory management operations (i.e. issuing prefetch and replacement hints) only when they are actually needed.

We aim to demonstrate the preceding statement by providing a concrete implementation of the technique presented by this thesis, using a full-featured optimizing compiler and a modern commercial operating system.

#### 1.4 Contributions

This thesis makes the following contributions:

- The proposal of a new strategy for coping with I/O latency in out-of-core programs that introduces a run-time layer to integrate information obtained from compiler analysis with information readily available to the operating system during program execution. Key features of this strategy are that it is fully-automatic, capable of improving overall performance in a multi-programmed setting, and able to adapt to dynamic conditions.

- A detailed evaluation of the proposed strategy, based on a full implementation of each of the three key components. The prefetching algorithm is implemented in the SUIF optimizing compiler [26, 61]. The operating system support has been implemented in two distinct operating systems—a research prototype designed for large-scale multiprocessors (HURRICANE) and a commercial operating system (Irix 6.5). By comparing the results on the two systems, we are able to gain insight into the key features that the operating system support should provide, and the effect that other architectural and software design decisions may have on our ability to support out-of-core programs successfully.

- An investigation into the feasibility of having out-of-core applications voluntarily release pages to improve overall performance in a multiprogrammed environment. Typically replacement decisions are the sole responsibility of the operating system, which has the only global view of competing demands for memory. This thesis evaluates whether it is possible for applications to make local decisions that improve global performance, based on minimal information about memory usage from the operating system.

- The development, implementation, and evaluation of a new compiler algorithm for *software pipelining* which is able to handle unknown or variable latencies, multi-dimensional loops, and unknown loop bounds (all of which present problems for existing software pipelining algorithms).

Although this thesis presents and evaluates a solution to a particular resource management problem (that of managing physical memory for an out-of-core program), we believe that the approach taken here, bringing together the strengths of the compiler and the operating system with a run-time adaptation layer, will be applicable to many other resource management problems as well.

#### 1.5 Overview of Dissertation

Chapter 2 lays out the overall design of the system and describes how the compiler, operating system, and run-time layer relate to each other. It also describes the benchmarks and hardware platforms used to evaluate the system. Chapter 3 studies the effect of our approach on the performance of out-of-core programs running on a dedicated computer system. Both the initial research prototype operating system, and the commercial system are studied. Chapter 4 studies the performance of both out-of-core and interactive applications in a multiprogrammed setting. Based on these results, a number of limitations of the compiler scheduling algorithm are identified, leading to a new algorithm which is described and evaluated in Chapter 5. Finally, Chapter 6 summarizes the important results in this dissertation, highlights their implications, and suggests directions for future work in this area.

### **Chapter 2**

## **System Design Alternatives and**

## **Evaluation Framework**

Recognizing the need is the primary condition for design. — Charles Eames

In this chapter we present the basic design of our system for automatically managing the I/O requirements of out-of-core programs. In this thesis, we focus on scientific computing applications, where large arrays are the primary data structure, and most data accesses occur in loops. Our goal is to fully hide I/O latency, thus eliminating its impact on overall execution time for this important class of applications. Conceptually, one can view our approach as enhancing the performance of virtual memory, since that is the abstraction we present to the programmer. Our design space, however, is not limited to the operating system where virtual memory support is traditionally implemented. We view the problem as one of collecting enough information about an application's memory requirements to enable us to make good management decisions. Relevant information may be most readily available at different times in a program's life cycle, and to different entities. Similarly, some actions or transformations may be easier to perform at certain program stages than at others.

In this chapter, we explore alternatives for collecting and acting on the information needed to make good memory management decisions. We begin in Section 2.1 by considering the features and actions our system

needs to support. We then present a number of options for providing these features, identifying strengths and limitations of each in Section 2.2. The actual design of the system presented in this thesis is then outlined in Section 2.3. The chapter concludes in Section 2.4 with an overview of the framework we will use to evaluate our overall design.

#### 2.1 Key Requirements

In Section 1.1.1 we identified two performance problems with virtual memory, namely the timing and size of I/O requests. A third problem is that the operating system must evict data from memory without knowing when or if the application will need it again. Any design that aims to preserve the abstraction of virtual memory for the application programmer must address these three problems.

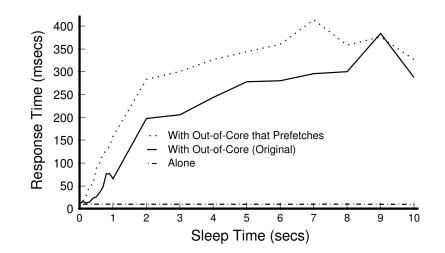

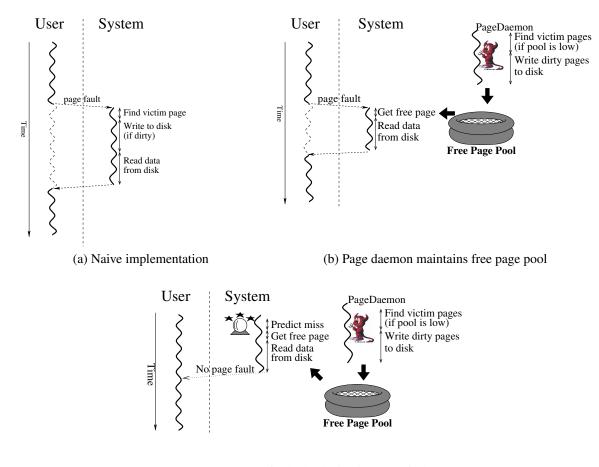

Under paged virtual memory, the operating system performs two types of disk accesses on behalf of applications: (i) pages are read from disk to satisfy a reference to data that was not present in memory, and (ii) modified (or *dirty*) pages are written out to disk to create free page frames for these reads. In the earliest implementations of virtual memory systems, victim page frames were selected and written out to disk (if dirty) in response to a page fault, creating a free page frame that was immediately filled by reading the required data from disk [22]. With this model, the performance cost of a page fault could be the latency of two disk accesses, as well as the processing cost of selecting a victim frame. Figure 2.1(a) illustrates the situation.

In general, hiding write latency is straightforward since writes can be buffered and pipelined, however when cleaning dirty pages, the write must complete before we can reuse the page frame. Fortunately, since the writes are transparent to the application, there is no restriction on when the request can begin. Modern Unix systems hide write latency using the *page daemon* approach introduced by 3BSD UNIX [4]. Rather than waiting for a free page to be needed before finding one, the operating system maintains a pool of (clean) free pages which can immediately be allocated in response to a page fault. A background system process (called the page daemon) monitors memory usage, identifies victim pages, and schedules writes for those that are dirty before they are moved to the free list. Figure 2.1(b) shows how the use of a page daemon improves

(c) Pages are prefetched, eliminating page faults Figure 2.1. Improving demand paging performance

performance.

The page daemon illustrates a key principle that we need to exploit to further improve virtual memory performance: the operation (a write) is scheduled early enough that the result (a clean free page) is available before it is needed, and furthermore the operation occurs in parallel with normal execution of the application. In other words, the introduction of the page daemon solves the timing problem for virtual memory writes by decoupling the I/O activity from the application's need for page frames.

The page daemon is also able to address the request size problem for virtual memory writes. Because free page frames are no longer generated in response to a particular page fault, the daemon can collect a larger set of dirty pages and write them to disk as a single large request, thus making more effective use of the available disk bandwidth. There is, of course, a cost associated with producing free page frames before they

are needed—the number of "soft" page faults could increase, and frequently-modified pages could be written to disk repeatedly they are cleaned and freed too early.

In contrast to writes, hiding *read* latency is difficult because the application cannot proceed without the missing data and thus must stall waiting for the I/O to complete. As with writes, we need to find a way to schedule the read operation early enough that the data arrives in memory before it is needed. Thus, the key to tolerating read latency is to split apart the *request* for data and the *use* of that data, while finding enough useful work to keep the application busy in between. This is an especially difficult task for a virtual memory system since the actual request occurs as a side effect of attempting to use a particular data item. Our system needs to provide a mechanism for predicting when the application is likely to access a page that is missing from memory so that an asynchronous *prefetch* request can bring the required data into memory before it is needed. Our prediction mechanism should attempt to bring pages into memory "just-in-time" to minimize the added memory pressure as much as possible. Figure 2.1(c) illustrates the effect on performance of an ideal predictor which brings pages into memory before they are needed, eliminating page faults in the application. We will refer to the combination of predicting pages that should be brought into memory, and deciding when to initiate the I/O requests for these pages as *prefetching*.

Prefetching does not reduce the number of disk accesses; it simply attempts to perform them over a shorter period of time by overlapping I/O with normal program execution. Thus, it cannot significantly reduce the execution time of an application whose I/O bandwidth demands already outstrip the bandwidth provided by the hardware. Fortunately, we can construct cost-effective, high-bandwidth I/O systems by harnessing the aggregate bandwidth of multiple disks [13, 33, 53]. Roughly speaking, one can always increase the I/O bandwidth by purchasing additional disks. It is important, therefore, that our prefetching mechanism be able to support multiple simultaneous requests to allow us to exploit the available bandwidth in a multiple-disk system. By overlapping I/O requests with each other, as well as with program execution, we create the potential for speedup factors greater than two.

In addition to hiding read latency and leveraging the available I/O bandwidth, a third challenge in achieving high performance is effectively managing main memory, which can be viewed as a large, fully-associative cache of data that actually resides on disk. There are two issues here. First, to minimize page faults, we would like to choose the optimal page to evict from memory when we need to make room for a new page that is being faulted in. Toward this goal, most commercial operating systems use an approximation of LRU (leastrecently-used) replacement to select victim pages. While LRU replacement may be a good choice for a default policy, there are cases where it performs quite poorly, and in such cases we would like to exploit application-specific knowledge to choose victim pages more effectively. The second issue is that we would like to minimize memory consumption, particularly when doing so does not degrade performance. For example, rather than filling up all of main memory with data that we are streaming through, we may be able to achieve the same performance by using only a small amount of memory as buffer space. By minimizing memory consumption, more physical memory will be available to the rest of the system, which is particularly important in a multiprogrammed environment. To accomplish both of these goals, we need a mechanism to predict which pages are relatively less important to a particular application, and to cause these pages to be freed first. Conceptually, we would like the predictor of Figure 2.1(c) to be responsible for replenishing the free page pool, based on its oracular knowledge of program accesses. In essence, we would like the flexibility to define an application-specific replacement policy, rather than being forced to choose from a fixed set of pre-defined policies.

In summary, the design of a system to improve virtual memory performance must provide the following features:

- support for *prefetching*, that is, asynchronously requesting data before it is needed, thus allowing us to tolerate disk read latency

- support for *multiple outstanding requests* to exploit the strengths of high-bandwidth multiple-disk I/O systems

- a means to explicitly identify pages that can be replaced, allowing us to build *application-specific replacement policies*.

| Entity     | Time                    | Information                    | Limitations             |

|------------|-------------------------|--------------------------------|-------------------------|

| Programmer | application development | purpose of program             | not system expert       |

| Compiler   | compile-time            | data structures, control flow, | no dynamic information  |

|            |                         | target system                  |                         |

| Operating  | run-time                | global resource usage, dy-     | no knowledge of program |

| System     |                         | namic behavior                 |                         |

Table 2.1. Available Information Sources

## 2.2 Design Alternatives

Having identified the features our system needs, we now discuss various alternatives for providing them. Our most difficult challenge is to predict page references accurately, allowing missing pages to be brought into memory before they are needed, and non-essential pages to be replaced first. In Section 2.2.1, we consider three possible sources of information to drive our predictions: the application programmer, the compiler and the operating system. We also consider the opportunities for making prefetching and replacement decisions in each of these components. To make the best decisions, we would like to combine the information that is readily available to each component in a single place; options for sharing information are presented in Section 2.2.2. We next consider how our predictor might communicate its decisions to the operating system, which has ultimate responsibility for managing physical memory pages, in Section 2.2.3.

## 2.2.1 Potential Sources of Information

Table 2.1 summarizes the entities that could be involved in collecting information about a program's memory accesses and implementing prefetching and replacement decisions.

## **The Programmer**

The application programmer has sole responsibility for high-level decisions such as the choice of algorithm to solve the problem, the data structures, and the overall program structure. Given suitable interfaces to the operating system, the programmer could make memory management decisions manually as the program is being designed and written. Explicit I/O calls are a typical example of this approach, which has three major drawbacks. First, the programmer is likely to be an expert in the application area, not the details of the target system where the program will run. Second, the decisions of the programmer are built into the source code and may seriously restrict the portability of the program; operations that improve performance on one system may be unsupported or may degrade performance on another. Third, programs that were initially written without concern for I/O cannot be improved without substantial programmer effort.

We believe that producing correct, readable, and maintainable programs is already difficult enough, and that limited human attention is best spent on these high-level details, rather than on contorting the program's source code to optimize performance on a specific execution platform. Our goal in this thesis is to allow the programmer to use the abstraction of virtual memory, without concern for performance. Therefore, we do not consider the programmer as a viable source of information about memory access patterns.

#### The Compiler

The compiler is responsible for translating the application from its high-level representation into a binary executable for a target system. It thus has natural access to information about data structures and control flow, such as the arrays and loops that are common in scientific computing applications. The compiler also has knowledge of low-level details of the target architecture. Although these architectural details are typically only used by the back-end to select machine instructions and allocate registers, it is reasonable to consider augmenting the compiler with system-level information such as the page size. Given this information, it is straightforward for the compiler to detect array accesses in loops, to determine which of these accesses will fall on separate pages, and to detect when pages are being reused. To predict whether or not these accesses will cause page faults, however, the compiler also needs to know how much data is being accessed in the loop, and how much memory is available on the target system. Accurately determining these parameters at compile-time is not always possible, even for numerical applications, since loop bounds may be symbolic variables at compile-time and available memory depends on dynamic demand from other programs at runtime. General-purpose applications are even harder to analyze statically, and are beyond the scope of this thesis.

Assuming predictions about page faults can be made at compile-time, the compiler could insert new instructions to prefetch these pages. To hide the latency of a disk access on modern processors, however,

the prefetch instruction needs to occur millions of instructions before the actual data reference. For generalpurpose codes with arbitrary control flow, it is impossible to find a single, static point in the code to insert the prefetch so far ahead of the use of the data. The loop structure common in numerical codes, on the other hand, gives us some chance for success. Even for numerical applications, however, deciding where in the program to place the prefetch instructions requires the compiler to know how long it will take for the prefetch to complete on the target system (and how long it will take to execute the code between the point where the prefetch is inserted and the point where the access occurs). While it is possible to provide the compiler with an estimate of the time to read a page of data from disk into memory, the actual time will depend on dynamic conditions such as other requests at the disk.

In spite of being limited by a lack of dynamic information, the compiler has considerable advantages. First, it does have access to some high-level program information (less than the programmer, but certainly much more than the operating system). Second, the time spent analyzing the program and collecting information about accesses only occurs once, while the payoffs in improved program performance will be realized each time the program is run. Third, the transformations performed by the compiler are fully-automatic, making it easier to port the application to a different system. We want to leverage the strengths of the compiler by making decisions *statically* whenever possible, but we need to retain the ability to improve upon these decisions *dynamically* as better information becomes available during execution.

#### The Operating System

The operating system is responsible for allocating system resources to competing applications, and is the only entity with a global view of dynamic conditions. These characteristics make it the natural choice for deciding when to allocate more memory to an application for prefetching, and when to reclaim memory from an application. Unfortunately, the operating system has no higher-level information about the data structures or control flow of a program. It must base its decisions on observations of past behavior, with the typical assumption that the recent past is a good predictor of the near future.

To make better decisions, we would like to combine the dynamic information available to the operating

system with the application-specific information available to the compiler.

## 2.2.2 Options for Sharing Information

Rather than trying to make any memory management decisions with incomplete information, we could have the compiler insert code to periodically notify the operating system of future page accesses by the application. For instance, a call could be added at the start of a set of loops to pass down a list of virtual pages that would be accessed in the loop. The operating system would then decide which of these pages needed to be prefetched and schedule the disk reads appropriately. Similarly, the list could be used to select pages for replacement (either pages that are not in the list, or pages whose access occurs furthest in the future)<sup>1</sup>. The problem is that the operating system does not know how much computation time will occur between accesses to pages in the list, and thus it doesn't know when to schedule the disk reads. The compiler could include a time estimate for each page, but for complex access patterns, the amount of information being communicated and the work required by the operating system to act on this information easily becomes excessive. For example, in the bucket sort application (BUK), many of the important data accesses are indirect references based on the contents of a very large array. The values in this array are unknown at compile-time, hence the list of page addresses would need to be generated dynamically and the information passed to the operating system would be at least twice the size of the array itself.

An alternative is to have the compiler make the best decisions it can based on available information. Those decisions (i.e., requests to prefetch or free pages) are re-examined at run-time when better information becomes available. For instance, a request to prefetch a page can be discarded if the page is already in memory, or if there is not enough memory available for the request. A request to free a page may be delayed or discarded if memory is ample when the request occurs. Although this information belongs to the operating system, crossing the user-level/system boundary is an expensive operation. The overhead of consulting the operating system for a decision on each request could become significant if the compiler frequently inserts requests which are discarded at run-time. We could force the compiler to only insert requests that are highly

<sup>&</sup>lt;sup>1</sup>This is essentially the approach taken by the TIP [43] system for prefetching explicit read requests. The original read system calls are used to track the application's progress and schedule the prefetches; with virtual memory accesses we do not have an original system call to use for this purpose.