### Compiler Optimization of Value Communication for Thread-Level Speculation

Antonia Zhai January 13, 2005 CMU-CS-05-103

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy.

Thesis Committee:

Todd C. Mowry, Chair Seth C. Goldstein Peter Lee Wen-mei W. Hwu, UIUC

Copyright © 2005 Antonia Zhai

This research was sponsored by the National Aeronautics and Space Administration (NASA) under grant nos. NAG2-6054 and NAG2-1230, the National Science Foundation (NSF) under grant no. CCR-0219931, and the Intel Corporation.

The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of any sponsoring institution, the U.S. government or any other entity.

**Keywords:** Thread-Level Speculation, Architecture, Compiler Optimization, Automatic Parallelization, Dataflow Analysis, Dependence Profiling

#### Abstract

In the context of Thread-Level Speculation (TLS), inter-thread value communication is the key to efficient parallel execution. From the compiler's perspective, TLS supports two forms of inter-thread value communication: speculation and synchronization. Speculation allows for maximum parallel overlap when it succeeds, but becomes costly when it fails. Synchronization, on the other hand, introduces a fixed cost regardless of whether the dependence actually occurs or not. The fixed cost of synchronization is determined by the critical forwarding path, which is the time between when a thread first receives a value from its predecessor to when a new value is generated and forwarded to its successor. In the baseline implementation used in this dissertation, we synchronize all register-resident values and speculate on all memory-resident values. However, this naive approach yields little performance gain due to the excessive cost from inter-thread value communication. The goal of this dissertation is to develop compiler-based techniques to reduce the cost of inter-thread value communication and improve the overall program performance.

This dissertation proposes to use the compiler to orchestrate interthread value communication for both memory-resident and register-resident values. To improve the efficiency of inter-thread value communication, the compiler must first decide whether to synchronize or to speculate on a potential data dependence based on how frequently the dependence occurs. If synchronization is necessary, the compiler will then insert the corresponding *signal* and *wait* instructions, creating a point-to-point path to forward the values involved in the dependence. Because synchronization could serialize execution by stalling the consumer thread, we use the compiler to avoid such stalling by applying novel dataflow analyses to schedule instructions to shrink the critical forwarding path.

This dissertation reports the performance impact of several compilerbase value communication optimization techniques on a four-processor single-chip multiprocessor that has been extended to support thread-level speculation. Relative to the performance of the original sequential program executing on a single processor, for the set of loops selected to maximize program performance, parallel execution with the proposed baseline implementation results in 1% performance degradation for integer benchmarks and 21% performance improvement for floating point benchmarks, while with the optimization techniques we developed, parallel execution achieves 22% and 42% performance improvement for integer benchmarks and floating point benchmarks, respectively.

### Acknowledgements

After generating several gigabytes of compilation intermediate files and parsing through hundreds of simulation outputs, I am amazed that this document has finally come together. Now, looking back to all my years at CMU, one thing is for sure: I could not have done this alone and I owe my thanks to many people.

First and foremost, I am deeply indebted to my advisor, Todd Mowry, for providing continuous guidance and support for the part ten (!) years (I have been working with Todd since I was a wee undergraduate). Words fail to describe the extend to which he has so patiently shaped my technical thinking, research abilities, presentation skills, among other things. Thank you, Todd!

I would also like to thank the other members of my thesis committee—Seth Goldstein, Peter Lee, and Wen-Mei Hwu—for providing invaluable assistance at all stages of this thesis. Their criticisms and advices are vital in making this thesis more accurate, more complete, and easier to read.

Furthermore, I also owe many thanks to my fellow STAMPeders for providing inspirations, criticisms, etc., during the meetings, and for sitting through so many practice talks! My special thanks go towards Chris Colohan and Greg Steffan, with whom I have worked closely, for building infrastructures and tools that make my research possible.

Last, but not least, I would also like to thank my family and friends for their love and support without which I would not have survived the Ph.D. process.

## Contents

| 1        | Intr | oduct  | ion                                                                        | 1  |

|----------|------|--------|----------------------------------------------------------------------------|----|

|          | 1.1  | TLS a  | and Inter-Thread Communication                                             | 2  |

|          | 1.2  |        | ating the Performance Impact of Optimizing Inter-Thread Value nunication   | 5  |

|          | 1.3  | Relate | ed Work                                                                    | 7  |

|          |      | 1.3.1  | Hardware-Based Schemes for Improving Inter-Thread Value Com-<br>munication | 7  |

|          |      | 1.3.2  | Improving Inter-Thread Value Communication Using Compiler<br>Techniques    | 10 |

|          | 1.4  | Disser | tation Contributions                                                       | 11 |

| <b>2</b> | Har  | dware  | and Software Support for TLS                                               | 13 |

|          | 2.1  | Execu  | tion Model                                                                 | 13 |

|          |      | 2.1.1  | Inter-Thread Value Communication                                           | 15 |

|          | 2.2  | Hardv  | vare Support                                                               | 17 |

|          | 2.3  | Hardv  | vare/Software Interface                                                    | 19 |

|          |      | 2.3.1  | Thread Creation and Termination                                            | 21 |

|          |      | 2.3.2  | Homefree Token                                                             | 22 |

|          |      | 2.3.3  | Speculative State Manipulation                                             | 23 |

|          |      | 2.3.4  | Stack Management                                                           | 23 |

|          |      | 2.3.5  | Exception Handling                                                         | 25 |

|          |      | 2.3.6  | Inter-Thread Value Communication                                           | 27 |

|          | 2.4  | Comp   | iler Support                                                               | 29 |

|          |      | 2.4.1  | Parallel Loop Selection                                                    | 32 |

|          |      | 2.4.2  | Parallelization                                                            | 34 |

|          |      | 2.4.3  | Optimization                                                               | 35 |

|          |      |        |                                                                            |    |

|          |      | 2.4.4                             | Code Generation                                                                      | 35 |  |

|----------|------|-----------------------------------|--------------------------------------------------------------------------------------|----|--|

|          | 2.5  | Chapt                             | er Summary                                                                           | 36 |  |

| 3        | Aut  | omati                             | c Synchronization                                                                    | 37 |  |

|          | 3.1  | Synch                             | ronization Versus Speculation                                                        | 37 |  |

|          | 3.2  | Relate                            | ed Work on Automatic Synchronization                                                 | 41 |  |

|          | 3.3  | Comp                              | iler-Inserted Synchronization                                                        | 42 |  |

|          | 3.4  | Synch                             | ronizing Register-Resident Values                                                    | 44 |  |

|          |      | 3.4.1                             | Constraints on Synchronization Insertion                                             | 45 |  |

|          |      | 3.4.2                             | Synchronization Insertion Algorithm                                                  | 45 |  |

|          |      | 3.4.3                             | Proof of Correctness                                                                 | 47 |  |

|          | 3.5  | Synch                             | ronizing Memory-Resident Values                                                      | 50 |  |

|          |      | 3.5.1                             | Hardware Support                                                                     | 51 |  |

|          |      | 3.5.2                             | Compiler Support                                                                     | 54 |  |

|          | 3.6  | Chapt                             | er Summary                                                                           | 59 |  |

| 4        | Inst | Instruction Scheduling 61         |                                                                                      |    |  |

|          | 4.1  | Critica                           | al Forwarding Path                                                                   | 61 |  |

|          |      | 4.1.1                             | Instruction Scheduling                                                               | 63 |  |

|          |      | 4.1.2                             | Aggressive Instruction Scheduling                                                    | 63 |  |

|          | 4.2  | Relate                            | ed Work                                                                              | 64 |  |

|          | 4.3  | Instruction Scheduling Algorithms |                                                                                      |    |  |

|          |      | 4.3.1                             | Conservative Scheduling                                                              | 67 |  |

|          |      | 4.3.2                             | Aggressive Instruction Scheduling                                                    | 73 |  |

|          | 4.4  | Chapt                             | er Summary                                                                           | 80 |  |

| <b>5</b> | Per  | formai                            | nce Evaluation                                                                       | 81 |  |

|          | 5.1  | Simula                            | ation Framework                                                                      | 81 |  |

|          | 5.2  | Bench                             | mark Characteristics                                                                 | 83 |  |

|          |      | 5.2.1                             | Benchmark Input                                                                      | 83 |  |

|          | 5.3  |                                   | ating the Performance Upper Bounds for Value Communication<br>nizations on All Loops | 86 |  |

|          |      | 5.3.1                             | Evaluation Methodology                                                               | 86 |  |

|          |      | 5.3.2                             | Reducing Critical Forwarding Path for Register-Resident Values                       | 88 |  |

|          |      | 5.3.3                             | Avoiding Speculation Failures for Memory-Resident Values                             | 92 |  |

|   | 5.4             | Loop Selection                                                                                                                   | 92  |

|---|-----------------|----------------------------------------------------------------------------------------------------------------------------------|-----|

|   | 5.5             | Evaluating Value Communication Optimizations                                                                                     | 95  |

|   | 5.6             | Program Performance                                                                                                              | 98  |

|   | 5.7             | Reducing the Critical Forwarding Path                                                                                            | 100 |

|   |                 | 5.7.1 Impact of Conservative Scheduling                                                                                          | 101 |

|   |                 | 5.7.2 Comparing Conservative Scheduling with the Multiscalar Algo-<br>rithm                                                      | 103 |

|   |                 | 5.7.3 Impact of Aggressive Scheduling                                                                                            | 105 |

|   |                 | 5.7.4 Comparison with Hardware-Based Optimizations                                                                               | 105 |

|   | 5.8             | Automatically Synchronizing Memory Accesses                                                                                      | 107 |

|   |                 | 5.8.1 Comparing Compiler-Based and Hardware-Based Automatic Syn-                                                                 |     |

|   |                 | $chronization \dots \dots$ | 110 |

|   |                 |                                                                                                                                  | 113 |

|   | 5.9             |                                                                                                                                  | 114 |

|   | 5.10            | Chapter Summary                                                                                                                  | 117 |

| 6 | Con             | clusions                                                                                                                         | 123 |

|   | 6.1             | Future Work                                                                                                                      | 124 |

| A | Pro             | filing Methodology                                                                                                               | 127 |

|   | A.1             | Control Dependences                                                                                                              | 128 |

|   | A.2             | Data Dependences                                                                                                                 | 130 |

| в | Sele            | ected High Coverage Loops                                                                                                        | 133 |

| С | $\mathbf{Esti}$ | mating the Performance Upper Bounds for Value Communica-                                                                         |     |

|   | tion            | Optimizations on All Loops                                                                                                       | 139 |

|   | C.1             | Avoiding Frequently Occurring Speculation Failures                                                                               | 139 |

|   | C.2             | Avoiding Speculation Failures on the First Occurrences of Loads                                                                  | 140 |

|   | C.3             | Impact of Optimizing Data Dependences in Callee Procedures                                                                       | 142 |

|   | C.4             | Impact of Optimizing Distance One Dependences                                                                                    | 144 |

|   | C.5             | Search for the Threshold of Frequently Occurring Data Dependences .                                                              | 144 |

|   | C.6             | Impact of False Sharing                                                                                                          | 149 |

| D | Loo             | ps with No Inter-Thread Data Dependences for Memory-Resident                                                                     | t   |

|   | Valı            | ies                                                                                                                              | 155 |

#### vii

## List of Figures

| 1.1  | Loops with potential inter-thread data dependences can be parallelized<br>under TLS                                                                                                                                                                                                                                |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1.2  | Synchronization vs. speculation under TLS                                                                                                                                                                                                                                                                          |

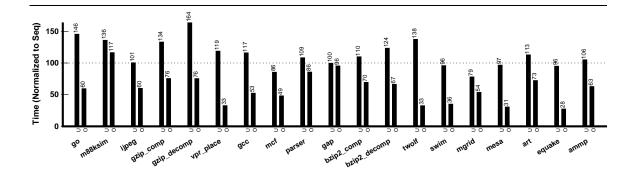

| 1.3  | Program performance potential of optimizing inter-thread value com-<br>munication. <b>U</b> is unoptimized for inter-thread value communication,<br>all register-resident values are synchronized and all memory-resident<br>values are speculated; <b>O</b> assumes a perfect value predictor for all val-<br>ues |

| 2.1  | Basic architecture and execution model for TLS                                                                                                                                                                                                                                                                     |

| 2.2  | TLS execution model. $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $16$                                                                                                                                                                                                                  |

| 2.3  | TLS value communication model                                                                                                                                                                                                                                                                                      |

| 2.4  | Hardware support for TLS                                                                                                                                                                                                                                                                                           |

| 2.5  | A simple while loop 20                                                                                                                                                                                                                                                                                             |

| 2.6  | Interface for thread creation and termination                                                                                                                                                                                                                                                                      |

| 2.7  | Interface for managing homefree token                                                                                                                                                                                                                                                                              |

| 2.8  | Interface for managing speculative modes                                                                                                                                                                                                                                                                           |

| 2.9  | Interface for stack manipulation                                                                                                                                                                                                                                                                                   |

| 2.10 | Interface for handling exception                                                                                                                                                                                                                                                                                   |

| 2.11 | Interface for value communication                                                                                                                                                                                                                                                                                  |

| 2.12 | Compiler infrastructure                                                                                                                                                                                                                                                                                            |

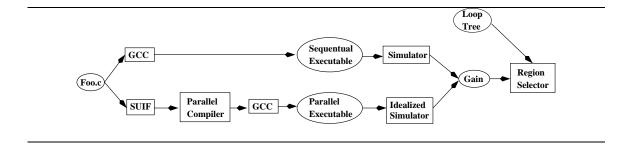

| 2.13 | Region selection process                                                                                                                                                                                                                                                                                           |

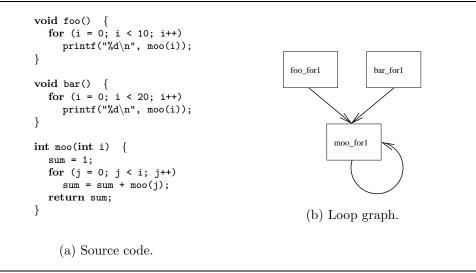

| 2.14 | Converting a program into a loop graph                                                                                                                                                                                                                                                                             |

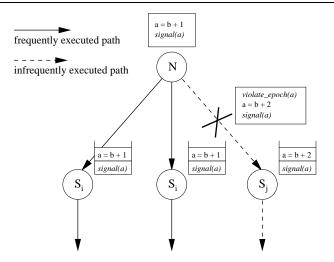

| 3.1  | Performance trade-off between speculation and synchronization $39$                                                                                                                                                                                                                                                 |

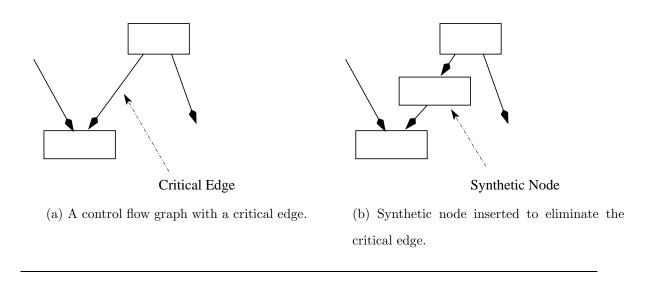

| 3.2  | Inserting synthetic nodes to eliminate critical edges                                                                                                                                                                                                                                                              |

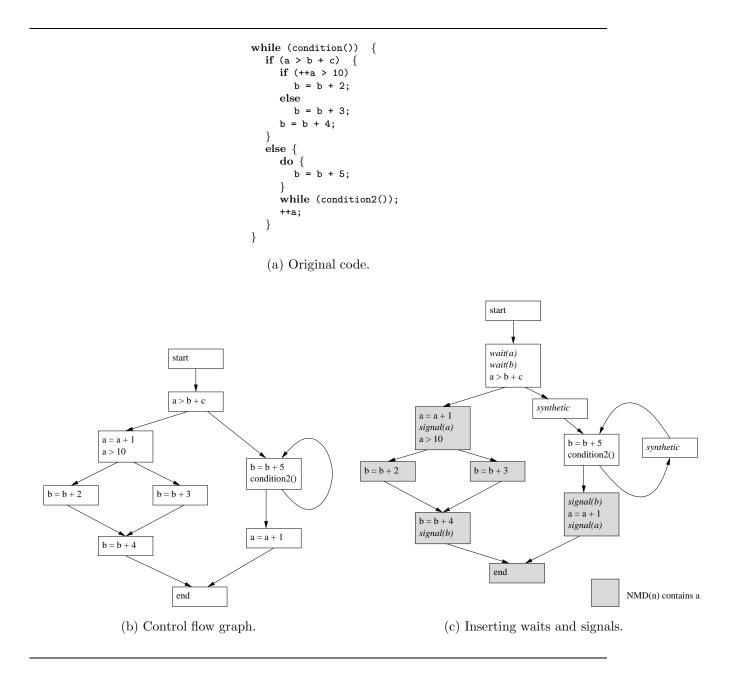

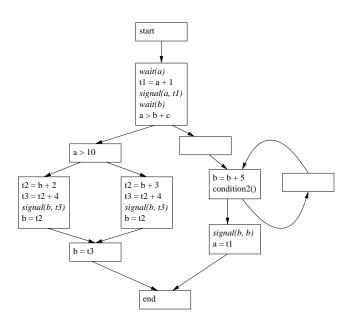

| 3.3  | Example of how waits and signals are inserted                                                                                                                                                                                                                                                                      |

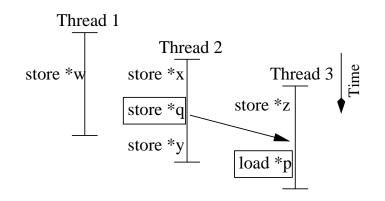

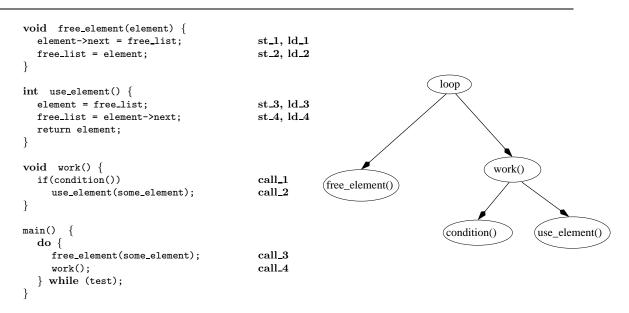

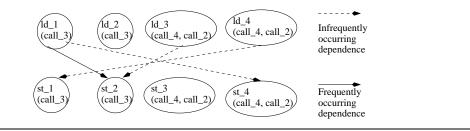

| Program transformation to synchronize frequently occurring memory-<br>resident dependences between threads.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 52                                   |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Compiler-directed procedural cloning and synchronization insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 55                                   |

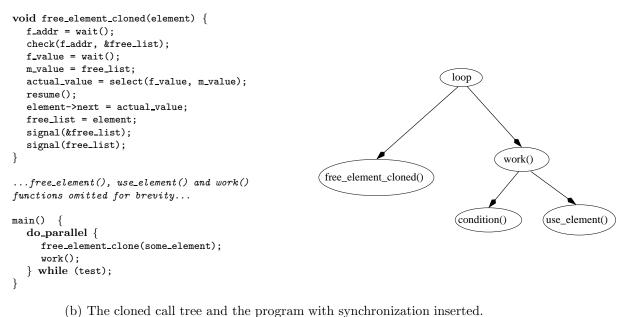

| An example dependence graph. Each vertex represents a load or store, identified by the combination of a unique number and call stack. Each edge shows a true data dependence between memory references. Ignoring infrequent data dependences, a group is formed with two vertices: $ld_{-1}$ and $st_{-2}$ (both having call stack (call_3)). Accounting for infrequent data dependences would result in an overly large group                                                                                                                                                                                                                                                              | 58                                   |

| Impact of scheduling on the critical forwarding path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 62                                   |

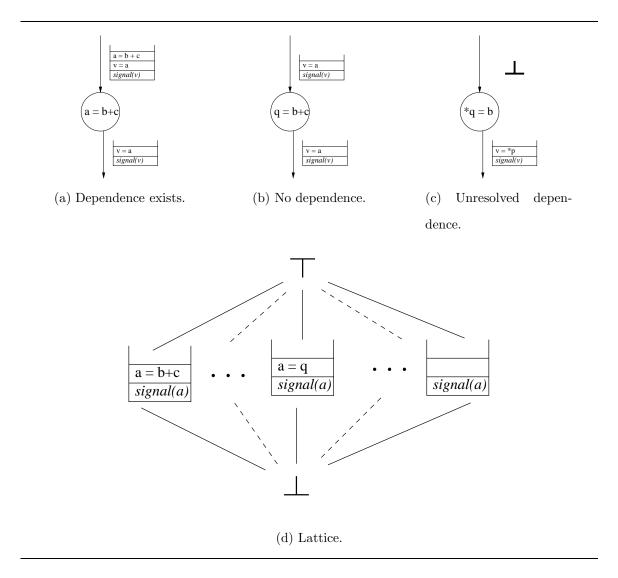

| Illustration of the <i>transfer</i> function (parts (a), (b), and (c)) used for computing the value of the <i>stack</i> in equation $(4.1)$ and the lattice (part (d)) over which the <i>stack</i> dataflow analysis is defined                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 68                                   |

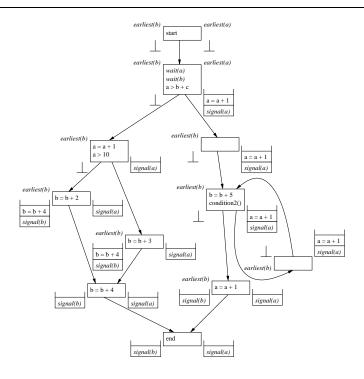

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 71                                   |

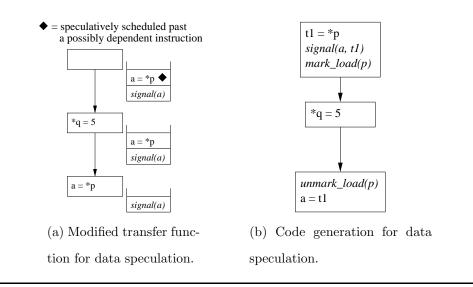

| Modified meet operator for speculatively scheduling instructions across                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 74                                   |

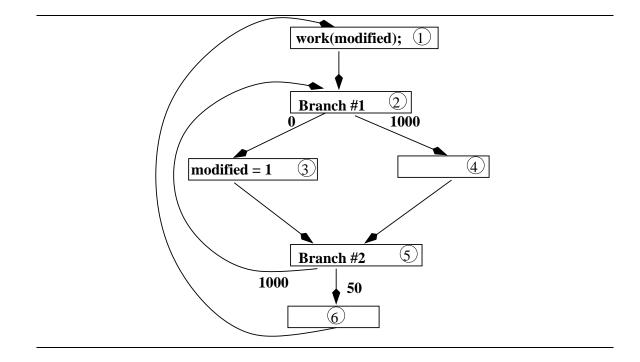

| Control dependence speculation for regions with an inner loop, and<br>each node is labelled with a unique identification. Edges are labeled<br>with number of times that edge is followed during execution. Both<br>branch #1 and branch #2 are biased branches                                                                                                                                                                                                                                                                                                                                                                                                                             | 77                                   |

| Modified dataflow analysis for speculatively scheduling instructions across data dependence.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 78                                   |

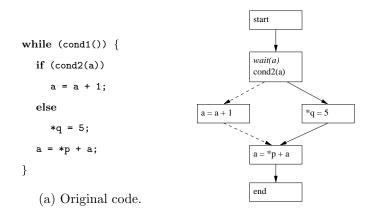

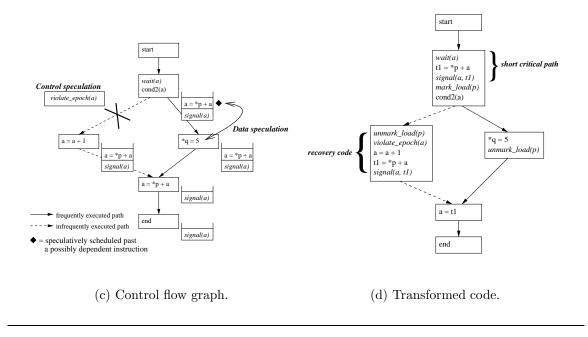

| Illustration of how speculation on control and data dependences can be complementary.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 79                                   |

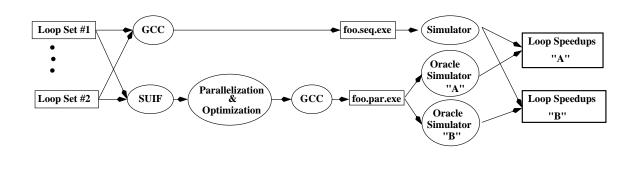

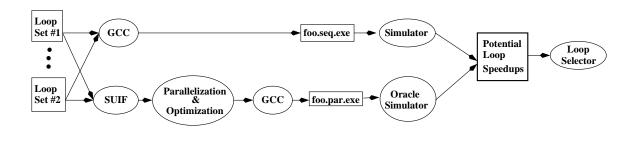

| Compilation and simulation framework for studying performance po-<br>tential of different optimizations.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 88                                   |

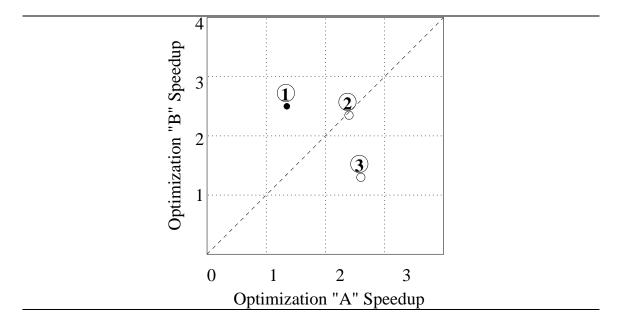

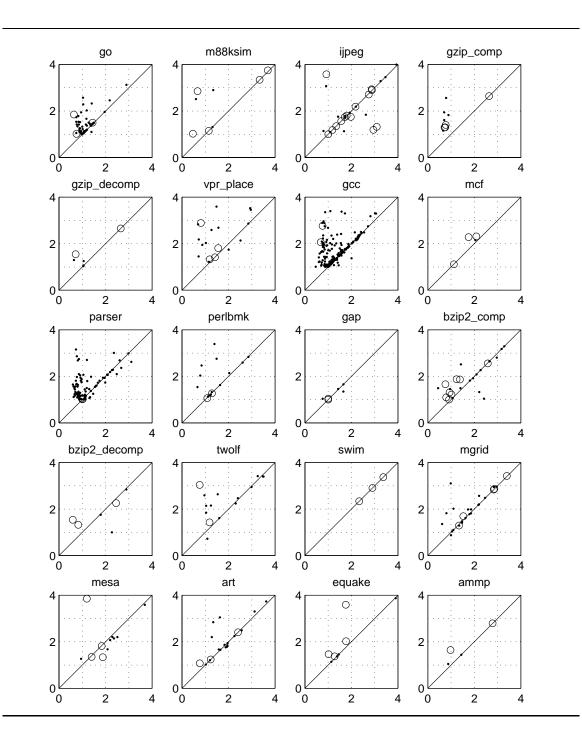

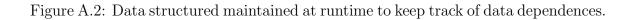

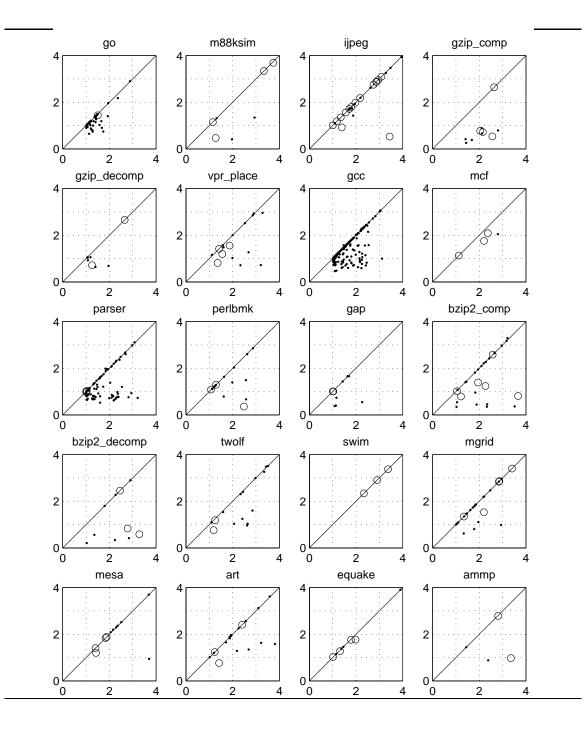

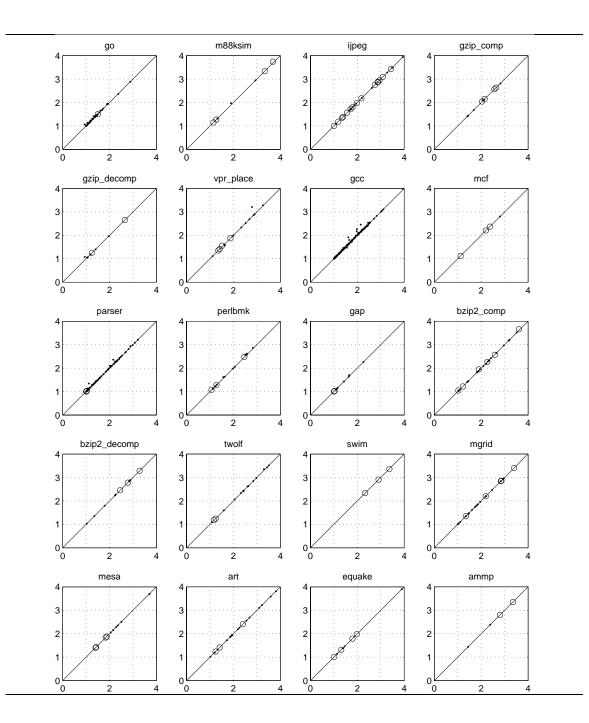

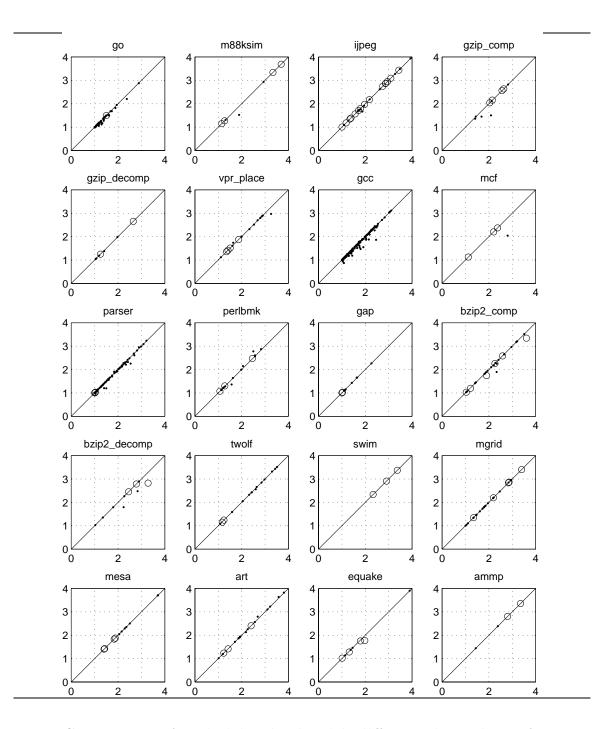

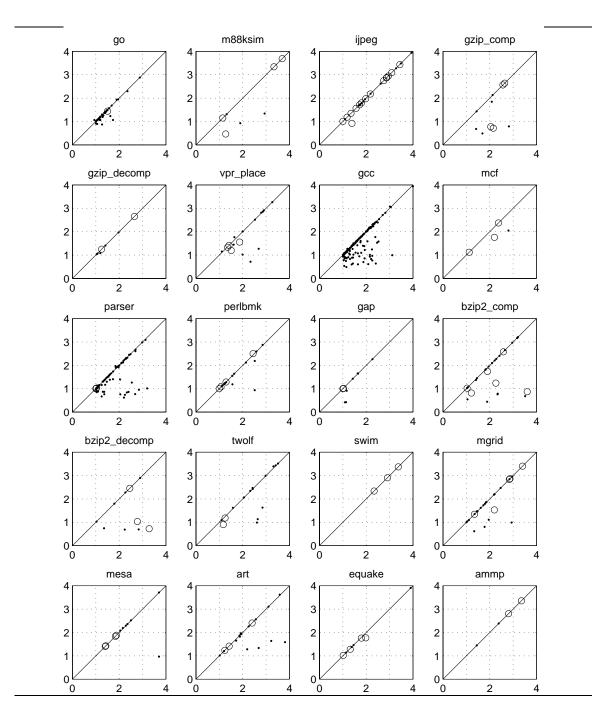

| Comparing the impact of optimization <b>A</b> vs. optimization <b>B</b> . Each data point in the graph represents a loop. Its x-coordinate is the loop's speedup when optimization <b>A</b> is applied, and its y-coordinate is the loop's speedup when optimization <b>B</b> is applied. ① represents a loop with less than 5% coverage that performs better with optimization <b>B</b> ; ② represents a loop with more than 5% coverage that performs a loop with more than 5% coverage that performs a loop with more than 5% coverage that performs a loop with more than 5% coverage that performs a loop with more than 5% coverage that performs better with optimization <b>A</b> . | 89                                   |

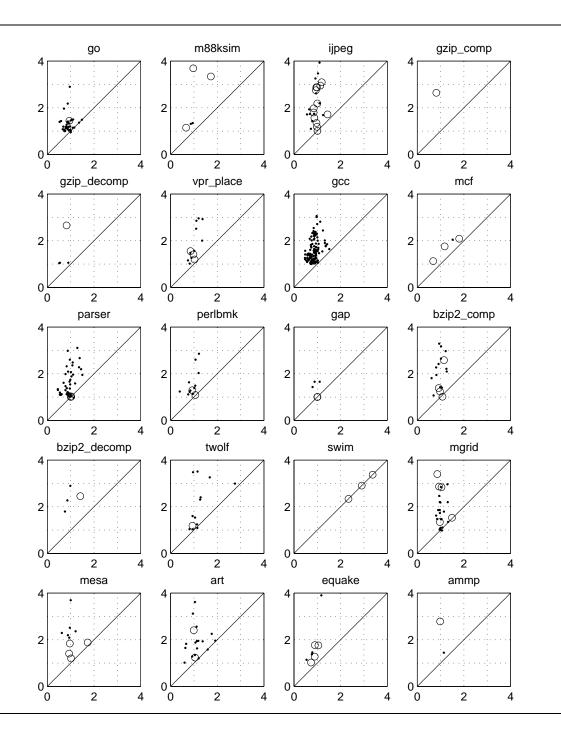

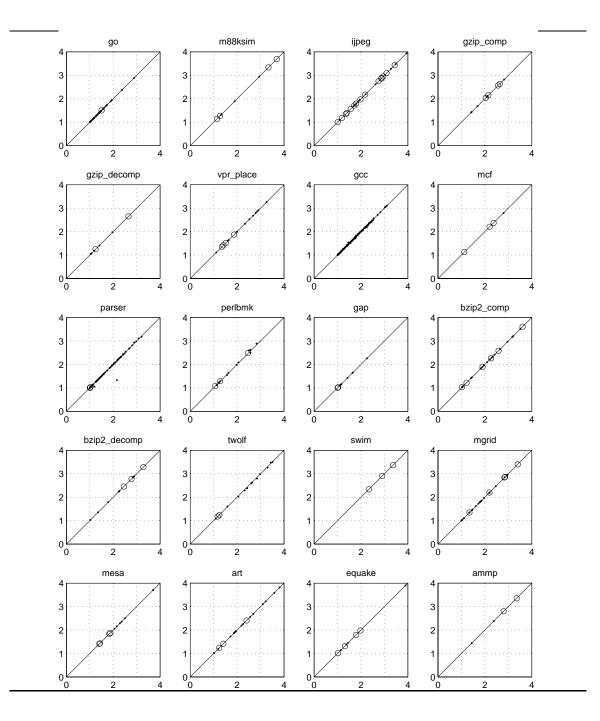

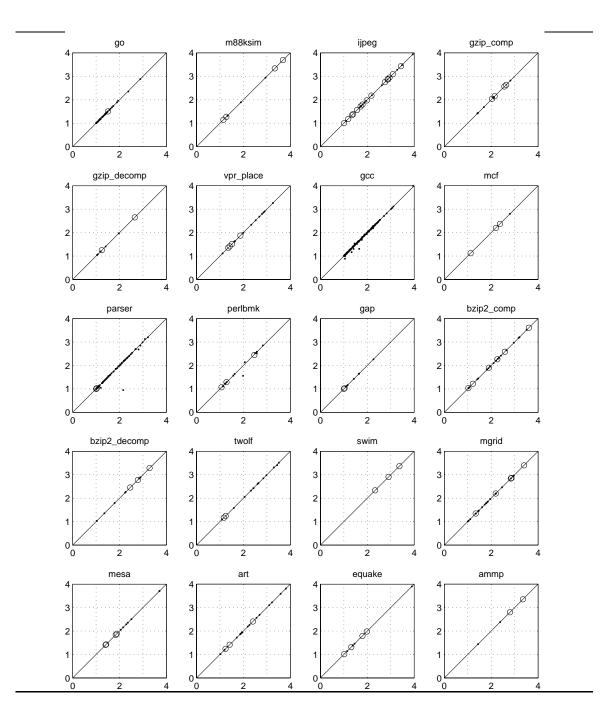

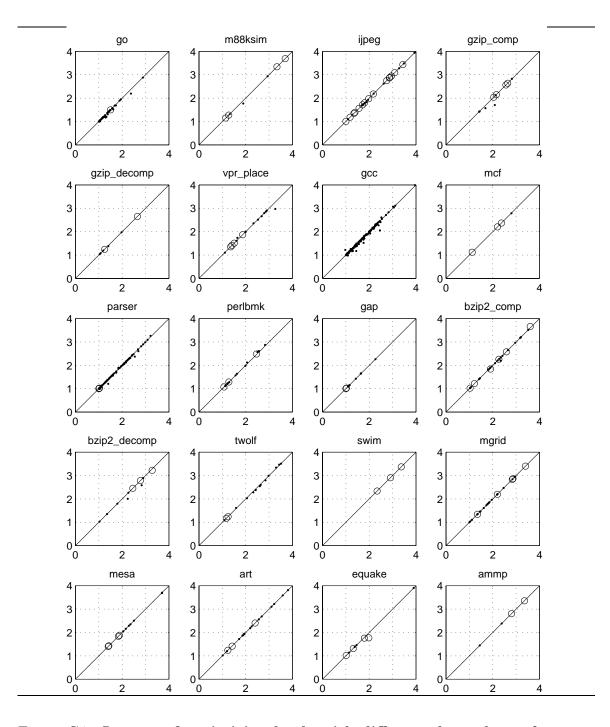

| Impact of reducing the critical forwarding path for register-<br>resident values. In each graph, the x-axis is the speedup with<br>no value predictor, and the y-axis is the speedup with a prefect value<br>predictor for all register-resident values. Loops that do not speed up<br>in both cases are omitted from the graph for clarity.                                                                                                                                                                                                                                                                                                                                                | 90                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | resident dependences between threads |

| 5.4  | Impact of avoiding speculation failures for memory-resident values. In each graph, the x-axis is the speedup with a prefect value predictor for all register-resident values, and the y-axis is the speedup with a perfect value predictor for both register-resident and memory-resident values. Loops that do not speed up in both cases are omitted from the graph for clarity.                                                                                                                                                                                                                                                                                                                                                                                                                      | 91  |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 5.5  | Region Selection Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 95  |

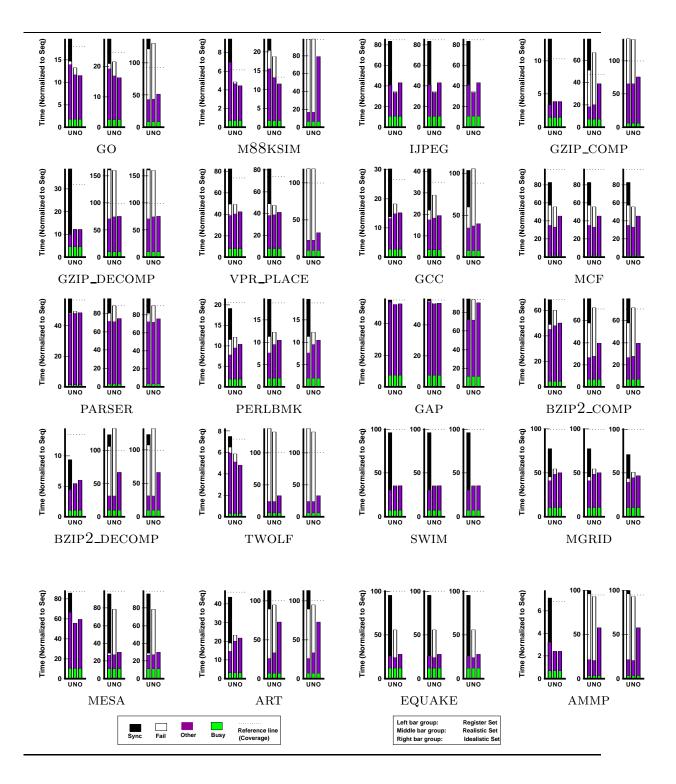

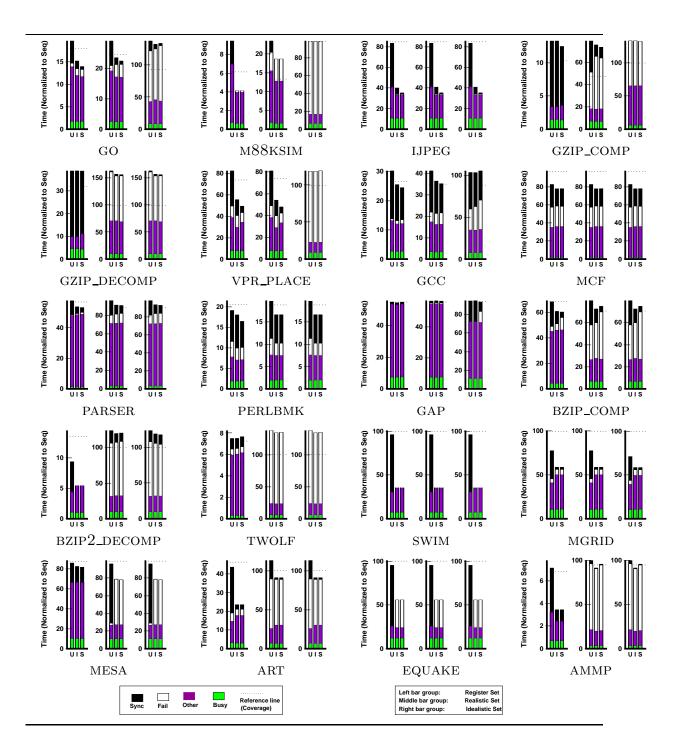

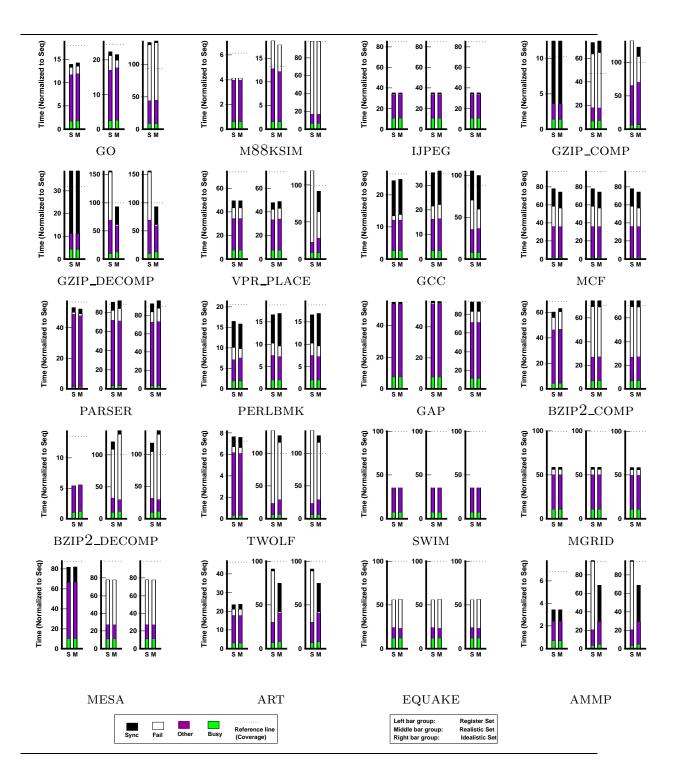

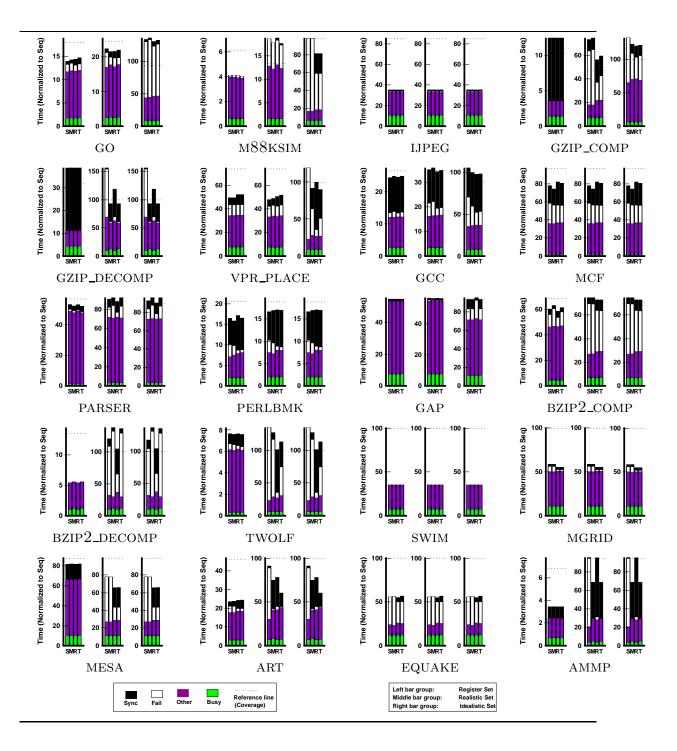

| 5.6  | Potential impact of optimizing inter-thread value communi-<br>cation. For each benchmark, three sets of results are presented, cor-<br>responding to the register, the realistic, and the idealistic loop sets,<br>respectively. Bars represent execution time of the parallel loops on a<br>four-processor CMP normalized to the sequential program execution<br>time. U is unoptimized, all register-resident values are synchronized<br>and all memory-resident values are speculated; N assumes a perfect<br>value predictor for all register-resident values; and O assumes a per-<br>fect value predictor for all values                                                                                                                                                                          | 96  |

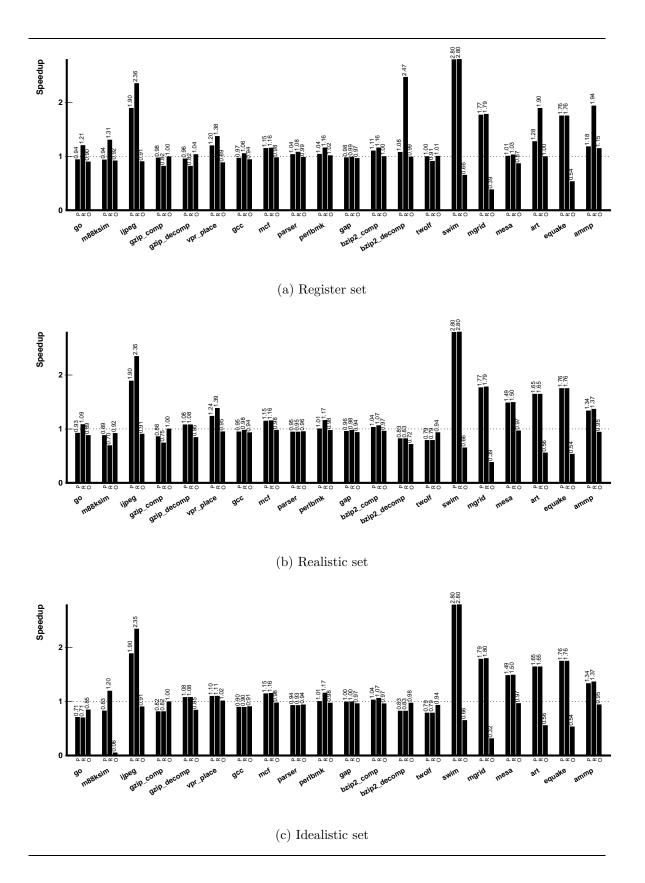

| 5.7  | Speedup achieved with TLS on a four processors CMP with previously described optimizations. $P$ is program speedup, $R$ is region speedup, and $O$ is outside-region speedup.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 99  |

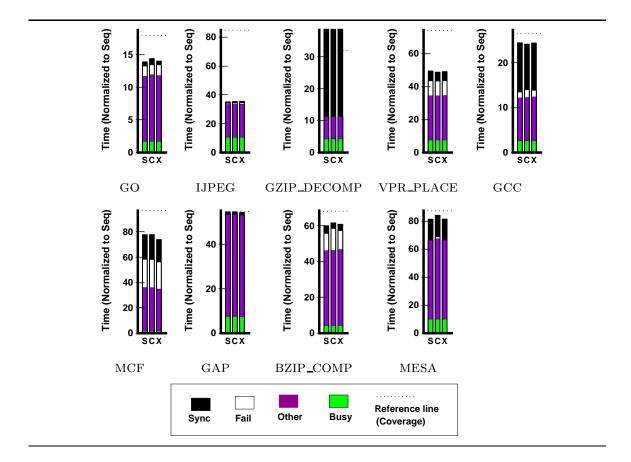

| 5.8  | Impact of instruction scheduling on reducing critical forward-<br>ing path for register-resident values. For each benchmark, three<br>sets of results are presented, corresponding to the performance of the<br>register, the realistic, and the idealistic loop sets, respectively. Bars<br>represent execution time of the parallel loops on a four-processor CMP<br>normalized to the sequential program execution time and the reference<br>line represents the coverage of each loop set. U is unoptimized, in<br>which all register-resident values are synchronized at first use and last<br>definition; I corresponds to only optimizing critical forwarding path<br>introduced by induction variables; S corresponds to reducing critical<br>forwarding paths for all register-resident values | 102 |

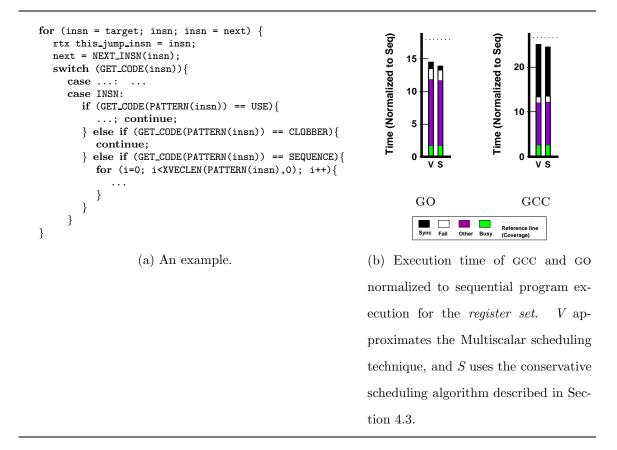

| 5.9  | Comparison with the Multiscalar scheduling algorithm.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 104 |

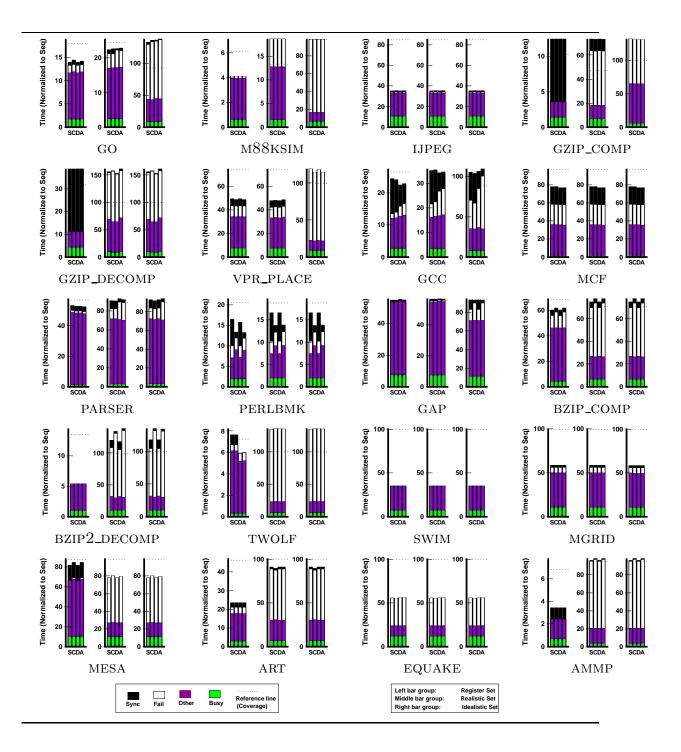

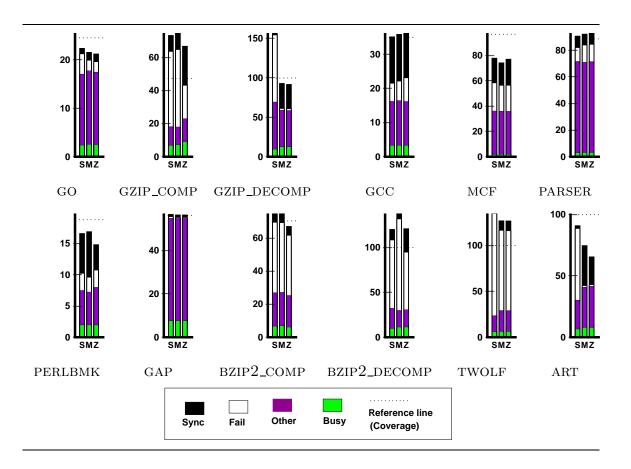

| 5.10 | Impact of speculative instruction scheduling on reducing critical forwarding path for register-resident values. For each benchmark, three sets of results are presented, corresponding to the performance of the register, the realistic, and the idealistic loop sets, respectively. Bars represent execution time of the parallel loops on a four-processor CMP normalized to the sequential program execution time and the reference line represents the coverage of each loop set. S schedules instructions using conservative instruction scheduling algorithm; C schedules instructions across control dependences; D schedules instructions across both control and data dependences.                                                                                                            | 106 |

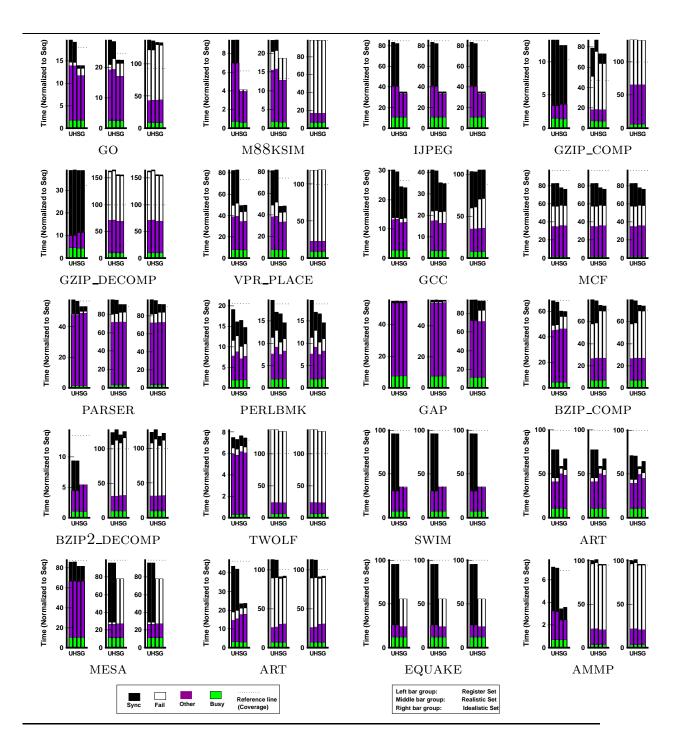

- 5.11 Impact of hardware optimization vs. compiler optimization for reducing critical forwarding path. For each benchmark, three sets of results are presented, corresponding to the performance of the register, the realistic, and the idealistic loop sets, respectively. Bars represent execution time of the parallel loops on a four-processor CMP normalized to the sequential program execution time and the reference line represents the coverage of each loop set. U is unoptimized, in which all register-resident values are synchronized at first use and last definition; H uses hardware optimization but not compiler optimization; S uses compiler optimization but not hardware optimization; G uses both the hardware and the compiler.

- 5.12 Impact of compiler-inserted synchronization on reducing speculation failures. For each benchmark, three sets of results are presented, corresponding to the performance of the register, the realistic, and the idealistic loop sets, respectively. Bars represent execution time of the parallel loops on a four-processor CMP normalized to the sequential program execution time and the reference line represents the coverage of each loop set. S has no synchronization for memory-resident values; M has compiler-inserted synchronization for memory-resident values, as described in Section 3.5.2.

108

109

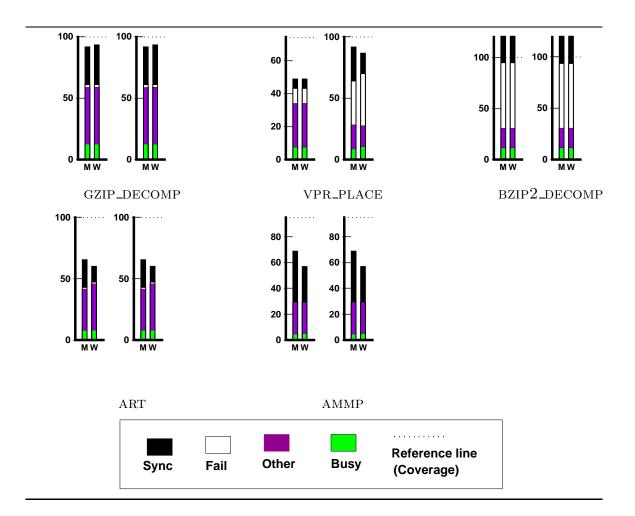

- 5.13 Impact of compiler-inserted vs hardware-inserted synchronization. For each benchmark, three sets of results are presented, corresponding to the performance of the register, the realistic, and the idealistic loop sets, respectively. Bars represent execution time of the parallel loops on a four-processor CMP normalized to the sequential program execution time and the reference line represents the coverage of each loop set. S has no synchronization for memory-resident values; M has compiler-inserted synchronization for memory-resident values, as described in Section 3.5.2; R has hardware-inserted synchronization for memory-resident values.

5.14 Impact of instruction scheduling for memory-resident value

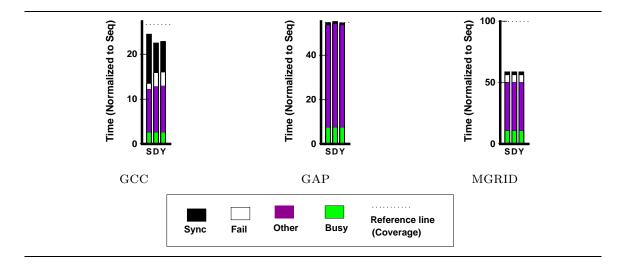

| 5.15 | Impact of profiling accuracy on speculatively scheduling in-<br>structions across data dependences. Results are shown for the<br><i>register set only</i> . Bars represent execution time of the parallel loops on<br>a four-processor CMP normalized to the sequential program execution<br>time and the reference line represents the coverage of each loop set. <b>S</b><br>schedules instructions using conservative instruction scheduling algo-<br>rithm; <b>D</b> schedules instructions across data dependences, profiled with<br>the <b>ref</b> input set; <b>Y</b> schedules instructions across data dependences,<br>profiled with the <b>train</b> input set | 117        |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 5.16 | Impact of profiling accuracy on speculatively scheduling in-<br>structions across control dependences. Results are shown for the<br><i>register set only</i> . Bars represent execution time of the parallel loops<br>on a four-processor CMP normalized to the sequential program execu-<br>tion time and the reference line represents the coverage of each loop<br>set. S schedules instructions using conservative instruction scheduling<br>algorithm; C schedules instructions across control dependences, pro-<br>filed with the ref input set; X schedules instructions across control                                                                           | 110        |

| 5.17 | Impact of profiling accuracy on compiler-inserted synchro-<br>nization. Results are shown for the <i>realistic set</i> only. S has no syn-<br>chronization for memory-resident values; M has compiler-inserted syn-<br>chronization for memory-resident values profiled with the <b>ref</b> input<br>set; Z has compiler-inserted synchronization for memory-resident val-                                                                                                                                                                                                                                                                                               | 118<br>119 |

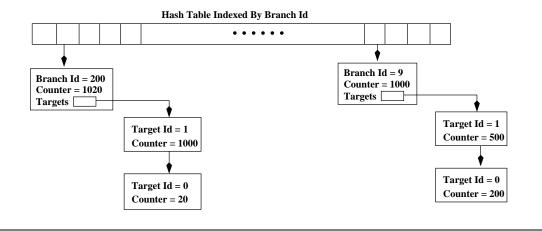

| A.1  | Data structure maintained at runtime to keep track of branch behavior.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 129        |

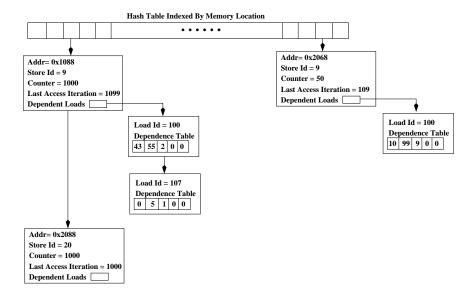

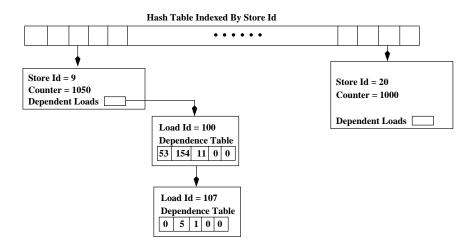

| A.2  | Data structured maintained at runtime to keep track of data dependences.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 132        |

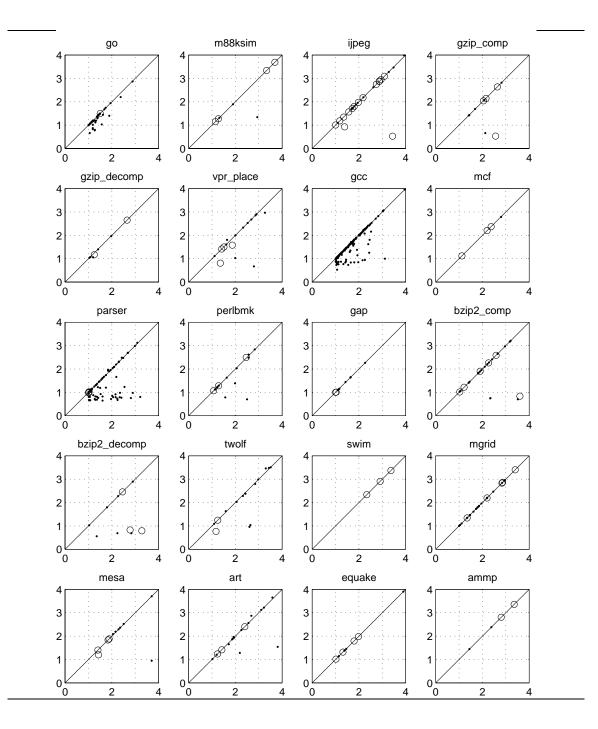

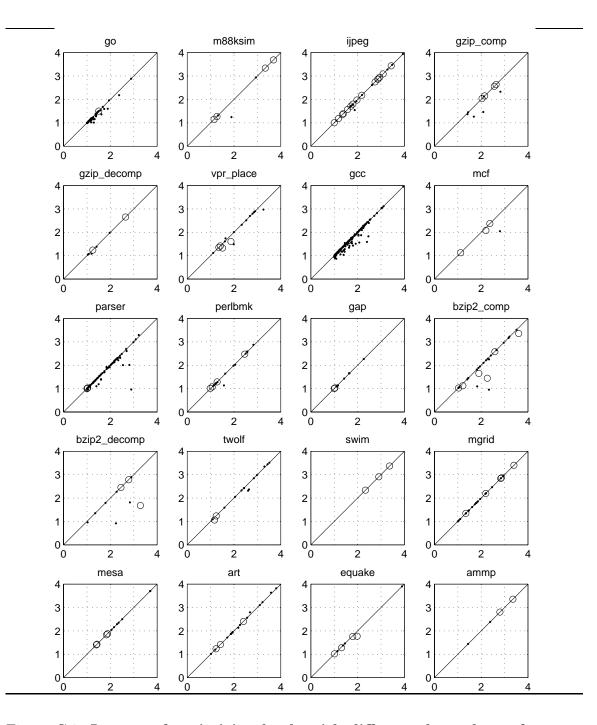

| C.1  | Impact of only avoiding speculation failures caused by loads<br>of frequently occurring inter-thread data dependences. In each<br>graph, the x-axis is the speedup with a perfect value prediction for<br>register-resident values and loads that depend on previous threads in<br>more than 1% of all threads, and the y-axis is the speedup with a pre-<br>fect value predictor for all register-resident values and memory-resident<br>values. Loops that do not speed up in both cases are omitted from the<br>graph for clarity.                                                                                                                                    | 141        |

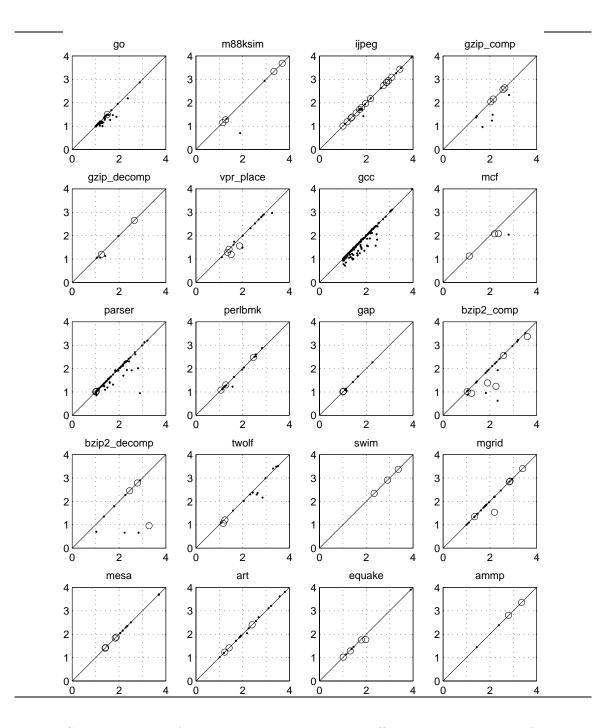

- C.2 Impact of only perfectly predicting values for loads on its first occurrence within a thread. In each graph, the x-axis is the speedup with a perfect value predictor for register-resident values and loads of frequently occurring data dependences on the first occurrences of these loads, and the y-axis is the speedup with a perfect value predictor for register-resident values and loads of frequently occurring data dependences on the first occurrences are on all occurrences. Loops that do not speed up in both cases are omitted from the graph for clarity.

- C.3 Impact of optimizing loads in the callee procedures. In each graph, the x-axis is the speedup with a perfect value predictor for all register-resident values and for loads of frequently occurring dependences regardless of their location, and the y-axis is the speedup with a perfect value predictor for all register-resident values and loads of frequently occurring dependences that can be reached from the parallelized loop with at most ten levels of procedural calls. Loops that do not speed up in both cases are omitted from the graph for clarity. . . 145

- C.4 Impact of optimizing loads in the callee procedures. In each graph, the x-axis is the speedup with a perfect value predictor for all register-resident values and for loads of frequently occurring dependences regardless of their location, and the y-axis is the speedup with a perfect value predictor for all register-resident values and loads of frequently occurring dependences that can be reached from the parallelized loop with at most five levels of procedural calls. Loops that do not speed up in both cases are omitted from the graph for clarity.

- C.5 Impact of optimizing loads in the callee procedures. In each graph, the x-axis is the speedup with a perfect value predictor for all register-resident values and for loads of frequently occurring dependences regardless of their location, and the y-axis is the speedup with a perfect value predictor for all register-resident values and loads of frequently occurring dependences that can be reached from the parallelized loop without going through any procedural calls. Loops that do not speed up in both cases are omitted from the graph for clarity. . . 147

146

143

- C.7 Impact of optimizing loads with different dependence frequencies. In each graph, the x-axis is the speedup with a perfect value predictor for all dependences occurring in more than 1% of all threads, the y-axis is the speedup with a perfect value predictor for all dependences occur in more than 2% of all threads; Loops that do not speed up in both cases are omitted from the graph for clarity. . . . . . 150

- C.8 Impact of optimizing loads with different dependence frequencies. In each graph, the x-axis is the speedup with a perfect value predictor for all dependences occurring in more than 1% of all threads, and the y-axis is the speedup with a perfect value predictor for all dependences occurring in more than 4% of all threads. Loops that do not speed up in both cases are omitted from the graph for clarity. . . 151

- C.9 Impact of optimizing loads with different dependence frequencies. In each graph, the x-axis is the speedup with a perfect value predictor for all dependences occurring in more than 1% of all threads, the y-axis is the speedup with a perfect value predictor for all dependences occurring in more than 8% of all threads. Loops that do not speed up in both cases are omitted from the graph for clarity. . . . 152

- C.10 Impact of optimizing loads with different dependence frequencies. In each graph, the x-axis is the speedup with a perfect value predictor for all dependences occurring in more than 1% of all threads, the y-axis is the speedup with a perfect value predictor for all dependences occurring in more than 16% of all threads. Loops that do not speed up in both cases are omitted from the graph for clarity. . . . 153

- C.11 Impact of avoiding speculation failures caused by false sharing. In each graph, the x-axis is the speedup with a perfect value predictor for loads of all real frequently occurring dependence, the yaxis is the speedup with a perfect value predictor for loads of all real frequently occurring dependence and false sharing. Loops that do not speed up in both cases are omitted from the graph for clarity. . . . 154

XV

## List of Tables

| 5.1  | Simulation parameters                                                                                                       | 82  |

|------|-----------------------------------------------------------------------------------------------------------------------------|-----|

| 5.2  | Benchmark descriptions                                                                                                      | 84  |

| 5.3  | Truncation of benchmark execution                                                                                           | 85  |

| 5.4  | Fraction of execution being parallelized                                                                                    | 94  |

| A.1  | Profiling routines that mark the beginning and the end of a region. $% \left( {{{\bf{n}}_{{\rm{n}}}}_{{\rm{n}}}} \right)$ . | 128 |

| A.2  | Profiling routines to collect control dependence information. $\ldots$ .                                                    | 129 |

| A.3  | Profiling routines to collect data dependence information                                                                   | 131 |

| B.1  | Speedup for High Coverage Loops in GO                                                                                       | 134 |

| B.2  | Speedup for High Coverage Loops in IJPEG                                                                                    | 134 |

| B.3  | Speedup for High Coverage Loops in GZIP_DECOMP                                                                              | 134 |

| B.4  | Speedup for High Coverage Loops in VPR                                                                                      | 135 |

| B.5  | Speedup for High Coverage Loops in MCF.                                                                                     | 135 |

| B.6  | Speedup for High Coverage Loops in PARSER                                                                                   | 135 |

| B.7  | Speedup for High Coverage Loops in PERLBMK.                                                                                 | 136 |

| B.8  | Speedup for High Coverage Loops in BZIP_COMP.                                                                               | 136 |

| B.9  | Speedup for High Coverage Loops in BZIP_DECOMP                                                                              | 136 |

| B.10 | Speedup for High Coverage Loops in TWOLF                                                                                    | 136 |

| B.11 | Speedup for High Coverage Loops in SWIM                                                                                     | 137 |

| B.12 | Speedup for High Coverage Loops in MGRID                                                                                    | 137 |

| B.13 | Speedup for High Coverage Loops in MESA.                                                                                    | 137 |

| B.14 | Speedup for High Coverage Loops in ART                                                                                      | 138 |

| B.15 | Speedup for High Coverage Loops in EQUAKE                                                                                   | 138 |

| B.16 | Speedup for High Coverage Loops in AMMP                                                                                     | 138 |

| D.1  | Fraction of execution being parallelized                                                                                    | 157 |

### Chapter 1

### Introduction

As technology advances, microprocessors that support multiple threads of execution are becoming increasingly common [18–20, 22, 35, 38, 66]. One way to fully utilize the computational power of such processors to speed up a single application is to create parallel programs by finding independent threads [5, 33, 65]. However, automatic parallelization for many general-purpose applications (e.g., compilers, spreadsheets, games, etc.) is very difficult due to pointer and indirect references, complex data structures and control flow, and input-dependent program behaviors. Thread-Level Speculation (TLS) [1, 14, 24, 29, 31, 32, 36, 40, 43, 51, 53, 54, 63, 67] facilitates the parallelization of such applications by allowing potentially dependent threads to execute in parallel while maintaining the original sequential semantics of the programs. To ensure correct execution under TLS, all true (read-after-write) inter-thread data dependences must be satisfied through some form of *inter-thread value communication*. However, inter-thread value communication, if not properly managed, may become the performance bottleneck by serializing parallel execution. This thesis reports the design, implementation and evaluation of several compiler techniques that mitigate such effects on performance.

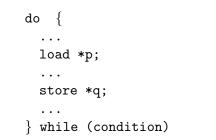

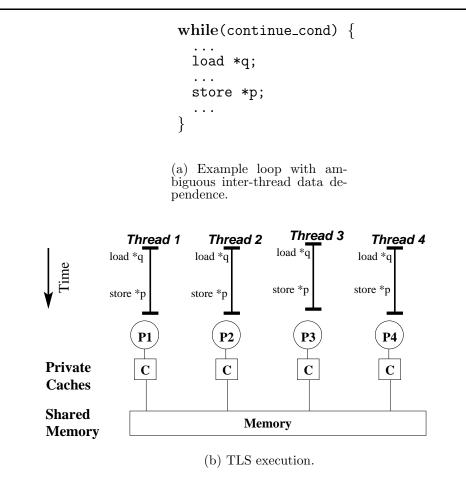

#### 1.1 TLS and Inter-Thread Communication

In TLS, the compiler partitions a program into parallel speculative threads without having to prove that they are independent, while at runtime the underlying hardware checks whether inter-thread data dependences are preserved and re-executes any thread for which they are not. This TLS execution model allows the parallelization of programs that were previously non-parallelizable. The following example demonstrates the basic principles of TLS. With TLS, the loop in Figure 1.1(a) can be parallelized by the compiler without proving that pointer p does not point to the same memory location as pointer q from previous iterations for all executions of the loop. Figure 1.1(b) shows how the program is executed speculatively in parallel on a four-processor, shared-memory multiprocessor that supports TLS, where each thread of execution corresponds to a single iteration of the loop. A thread is allowed to execute until completion if the load through pointer p in this thread does not load from the addresses stored to by pointer q in the previous threads. However, in the example, the load through pointer p in thread 4 loads from the address stored to by thread 1, creating a read-after-write data dependence and causing the speculation to fail. Consequently, while threads 1, 2 and 3 have been successfully parallelized, thread 4 has to be re-executed.

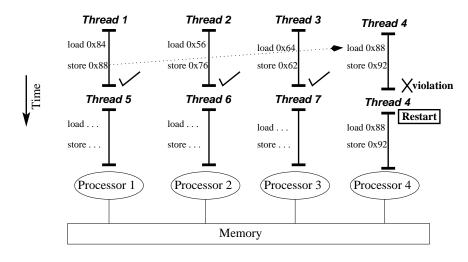

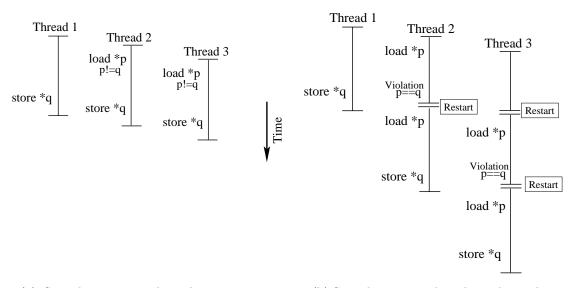

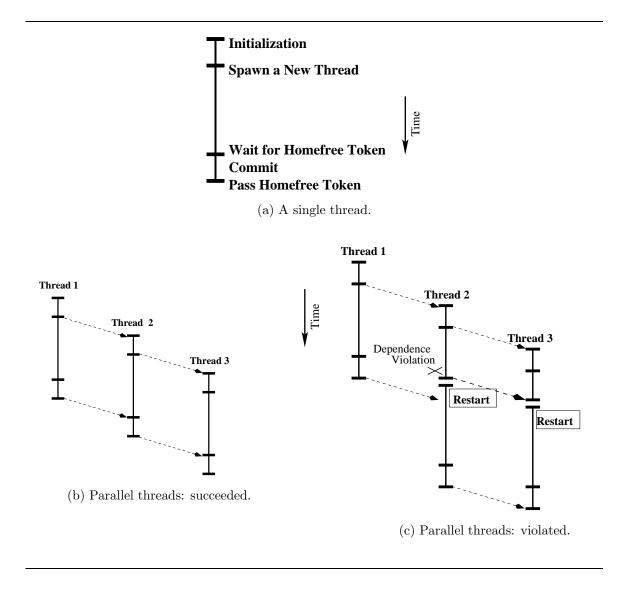

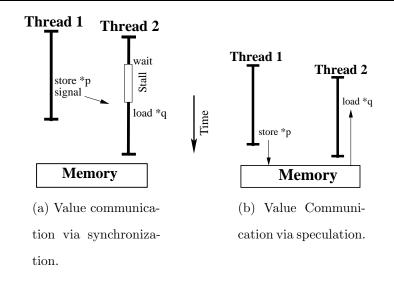

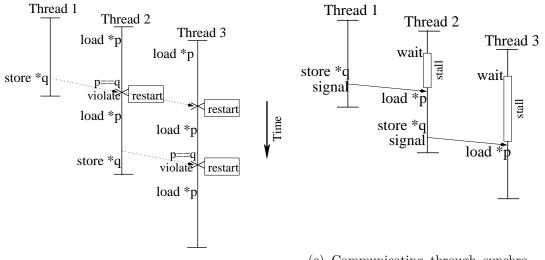

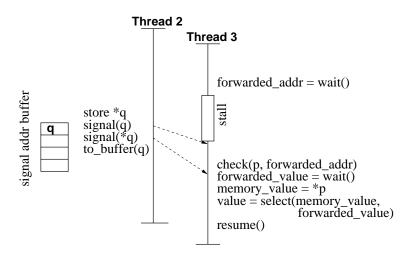

TLS is very efficient when speculation always succeeds since it would allow maximum parallel overlap as shown in Figure 1.2(a), while it becomes very inefficient when speculation fails often since re-execution has to be invoked frequently, as shown in Figure 1.2(b). Thus, for frequently occurring data dependences, we must have some alternative methods to avoid speculation failures. One approach is to synchronize them by inserting a wait operation before load \*p and a signal operation after store \*q to forward the stored value explicitly between the two threads, as shown in Figure 1.2(c). On the other hand, synchronization has its own problem—it stalls the

(a) Pointer-based code example.

(b) Speculatively parallel threads.

Figure 1.1: Loops with potential inter-thread data dependences can be parallelized under TLS.

(a) Speculating on a data dependence that always succeeds.

(b) Speculating on a data dependence that always fails.

Thread 2

\*p

tall

Thread 3

stall

wait

load \*p store \*q

signal

forward \*q

Figure 1.2: Synchronization vs. speculation under TLS.

consumer threads. The amount of time the consumer threads sit idle during parallel execution is determined by the *critical forwarding path*, which is the time between when a thread first receives a value from its predecessor to when a new value is generated and forwarded to its successor. The shorter the *critical forwarding path*, the more parallel overlap the parallel threads have, as shown in Figure 1.2(c) and 1.2(d). To summarize, from the perspective of the compiler, there are two ways to communicate values between threads under TLS. The compiler can either (i) pretend that the dependence does not exist, and completely rely on the underlying hardware to detect dependence violations, and invoke recovery operations when necessary; or (ii) schedule an explicit synchronization using the wait/signal instruction pair to forward a value between the threads. We refer to the former as value communication via speculation and the latter as value communication via synchronization.

## 1.2 Estimating the Performance Impact of Optimizing Inter-Thread Value Communication

To quantify the importance of optimizing inter-thread value communication, we estimate the performance potential of compiler optimization for inter-thread value communication by simulating TLS execution using an optimal inter-thread value communication model. For this experiment, a set of loops is selected to maximize program performance when the cost of inter-thread value communication could be completely eliminated. These loops are parallelized by synchronizing all dependences between register-resident values and speculating on all dependences between memory-resident values. This inter-thread value communication scheme is chosen as the default implementation because the dependences between register-resident values are easy to analyze statically and are often dependent, while memory-resident values are difficult

Figure 1.3: Program performance potential of optimizing inter-thread value communication. U is unoptimized for inter-thread value communication, all register-resident values are synchronized and all memory-resident values are speculated; O assumes a perfect value predictor for all values.

to analyze statically and less likely to be dependent.

This experiment is conducted using a detailed simulator that implements a fourprocessor single-chip multiprocessor with TLS support. Detailed description of the underlying hardware can be found in Chapter 2. Two sets of simulations are studied, the first simulating the costs of inter-thread value communication, including the costs of both re-executions and synchronization, and the second set estimating the performance upper bound by implementing an oracle that always applies the optimal strategy of inter-thread value communication. The best possible optimization for reducing the cost of value communication is a perfect value predictor that prevents any data dependence speculation from failing and any synchronization from stalling. The results are shown in Figure 1.3, in which each bar represents the program execution time normalized to that of the original sequential program. Bars less than 100 are speedups. The  $\mathbf{U}$  bars, which are the execution time when no value communication optimization is applied, indicate that our baseline spends a significant amount of time on inter-thread value communication, slowing down integer benchmarks by 21.8% while speeding up floating point benchmarks by a mere 1% on average relative to sequential execution. With a perfect value predictor eliminating the cost of interthread value communication, integer benchmarks and floating point benchmarks can potentially speed up performance by 33.6% and 52.5% respectively relative to the sequential program execution. The performance gap between the **U** bars and the **O** bars is pursued in this dissertation.

This dissertation proposes to use the compiler to orchestrate inter-thread value communication for both memory-resident and register-resident values. The compiler first decides whether to synchronize or to speculate on a potential data dependence. If synchronization is necessary, the compiler will then insert the corresponding *signal* and *wait* instructions, creating a point-to-point path to forward the values involved in the dependence. The compiler is also used to avoid stalling the consumer threads by scheduling instructions to reduce the critical forwarding path.

#### 1.3 Related Work

Many schemes have been proposed for improving the efficiency of inter-thread value communication, some hardware-based [15, 39, 43, 47, 64] and others software-based [32, 67, 68, 72, 73, 75]. This section explains value communication issues raised from both hardware-based and software-based previous investigations. More detailed descriptions of the related work for each compiler optimization technique can be found in the corresponding chapters.

### 1.3.1 Hardware-Based Schemes for Improving Inter-Thread Value Communication

For inter-thread value communication, hardware-based approaches usually treat registerresident values and memory-resident values with different strategies. Hardwarebased automatic synchronization [15, 47, 64] was proposed specifically for inter-thread memory-resident value communication. Dedicated hardware register-resident value forwarding [39] and reorder buffer prioritization [64] were proposed specifically for improving register-resident values communication. We will also discuss hardwarebased value prediction techniques [15, 44, 64] that target both memory-resident and register-resident values.

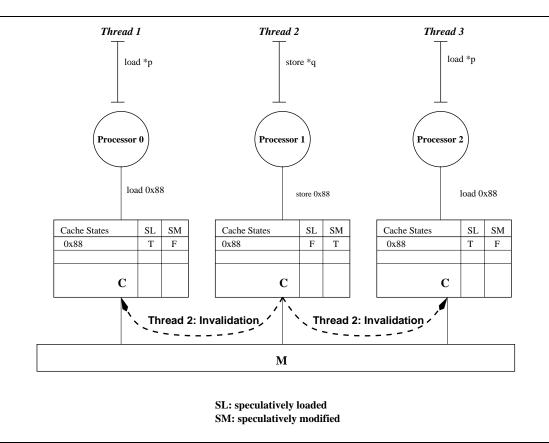

### Hardware Support for Automatic Synchronization for Memory-Resident Values

To detect inter-thread data dependences for memory resident values, Multiscalar [25, 26, 58] proposed using a centralized address resolution buffer (ARB). Based on such a centralized scheme, Moshovos *et al.* [47] used a centralized hardware lookup table to automatically synchronize frequently occurring data dependences by matching dependent load/store pair and demonstrated that the number of speculation failures can be reduced. This approach, however, requires a special functionality that is unique to the Multiscalar proposal—that is, the memory location causing data dependence violation is made available to the consumer immediately after the producer has finished modifying this location. For TLS proposals that are based on a distributed memory coherence protocol, implementing this feature implies performing complex version management. In addition, this scheme could limit performance and is difficult to scale due to the need of centralized structures.

To avoid the centralized structures required in Moshovos' work, Cintra *et al.* [15] and our group [64] both proposed approaches using only decentralized hardware lookup tables for automatically synchronizing memory-resident values. Cintra *et al.* [15] implemented hardware lookup tables to determine whether speculation is likely to fail for a certain cache line, while our proposal [64] used a fully associative buffer to keep track of load instructions rather than memory lines. Although it is relatively easy to identify the cache lines and/or the load instructions that cause speculation to fail, it is more difficult to identify the corresponding store instructions that produce the value. For the producer to identify such store instructions, it must be able to predict (i) the memory locations causing data dependence violations in the consumer thread and (ii) the last stores modifying these memory locations. Thus, both proposals could over-synchronize parallel execution by requiring the consumer thread to stall until the previous threads commit.

The compiler, having a global view of the entire program, could help in this case, and thus this research uses the compiler to identify not only load instructions that cause speculation to fail, but also the corresponding stores. Consequently, load instructions could be issued as soon as their corresponding store instructions are executed. Details are presented in Section 5.8.

### Hardware Support for Fast Inter-Thread Register-Resident Value Forwarding

The critical forwarding path introduced by synchronizing register-resident values can serialize parallel execution and degrade performance. It includes two components, (i) the time required to compute the forwarded value and (ii) the time required to forward the value between two processors. Our group's previous work [64] proposed to reduce the former by prioritizing instructions required to compute forwarded value in the reorder buffer and computing the forwarded value early. Krishnan *et al.* [40] proposed to reduce the latter using a dedicated distributed register file system that is referred to as the *distributed scoreboard*. Since synchronization for register-resident value is often the performance bottleneck during parallel execution, both approaches have been demonstrated to be effective. However, we believe that the compiler, having the global knowledge of the entire program, can schedule instructions across a larger distance and can thus reduce the *critical forwarding path* more aggressively. In addition, the compiler-based approach eliminates the need for expensive hardware support. Details are presented in Section 5.7.

#### Value Prediction for Register-Resident and Memory-Resident Values

Hardware can also avoid the costs of inter-thread value communication through value prediction [15, 43, 44, 64]. Previous work [44] has shown that value prediction can be used efficiently to communicate register-resident values, but it is less efficient at communicating memory-resident values. Cintra *et al.* [15] and our group's [64] previous studies have also pointed out that since incorrect value prediction can incur expensive recovery operations, it should be applied only to values that are predictable.

### 1.3.2 Improving Inter-Thread Value Communication Using Compiler Techniques

In this section, we briefly discuss two previous proposals that rely on the compiler to manage inter-thread values communication.

Multiscalar [25, 26, 58] developed compiler algorithms to insert synchronization and to move signals and their dependent instructions early within a thread (which is also referred to as a *task* in Multiscalar). However, the Multiscalar scheduler was designed specifically for Multiscalar tasks, which usually consist of only a few basic blocks and do not contain procedure calls or loops. In contrast, the work in this dissertation targets threads that are much larger on average and may contain complex control flow. We propose and implement a dataflow-based scheduler that is able to move instructions past inner loops and procedure calls. More implementation details and a contrast to Multiscalar are presented in Section 4.2 and the performance comparison is in Section 5.7.2. The Superthreaded architecture [67] proposed a different execution model. In this model, each thread first computes the addresses stored to by the current thread on which later threads could be dependent (a.k.a target store addresses), and forwards these addresses to its successors. It then forwards the contents of these addresses as they become available. The consumer thread, on the other hand, will stall before it loads a value from a forwarded target store address. However, computing all the *target store addresses* early requires significant instruction reordering by the compiler, which is not always possible. Thus, it is difficult to obtain the desired parallel overlap.

Concurrently with our work, Zilles and Sohi [75, 76] proposed the master/slave speculative execution paradigm by having a master thread execute a *distilled* version of the program that orchestrates and predicts the values for slave threads. In this scheme, communicated values are pre-computed by the master thread and distributed to the slave threads (as opposed to being updated and forwarded between consecutive speculative threads). Generating the distilled code for the master thread essentially requires us to identify the critical forwarding path for all values that require communication, and the instruction scheduling techniques described in Section 4.3 can be used for this purpose.

#### **1.4** Dissertation Contributions

The primary contributions of this dissertation are the following:

• The proposal of using profiling-based compiler techniques to automatically synchronize frequently occurring memory-resident value dependences to avoid speculation failure. This approach, which aims to improve performance by synchronizing frequently occurring data dependences, trades off the costs of the recoveries from failed speculations with the costs of synchronization stalls. Because the existence of potential aliasing between memory accesses makes accurate static analysis difficult, this research relies on profiling information to identify instructions that need synchronization and on hardware support to ensure correct execution.

- The proposal of using dataflow-based instruction scheduling algorithms to reduce the critical forwarding path. This research identifies the critical forwarding path introduced by register-resident value synchronization as a key performance bottleneck for many applications and presents novel dataflow-based instruction scheduling algorithms to reduce the length of the critical forwarding path. With the proper hardware support, this technique has also been extended to speculatively schedule instructions across control and data dependences within a thread.

- A thorough evaluation of the proposed compiler algorithms on a detailed architectural model with the help of a simulator. The evaluation shows that the proposed compiler-based techniques are effective in reducing the cost of interthread value communication.

- A comparison between compiler-based and hardware-based inter-thread value communication techniques. This demonstrates that compiler-based instruction scheduling techniques are more effective in reducing the critical forwarding path than hardware-based techniques, since the compiler, having global knowledge of the entire program, is able to schedule instructions across a larger distance. On the other hand, this study also shows that the compiler and the hardware should work in tandem to avoid speculation failures, since each of the two techniques benefits a different set of benchmarks.

### Chapter 2

# Hardware and Software Support for TLS

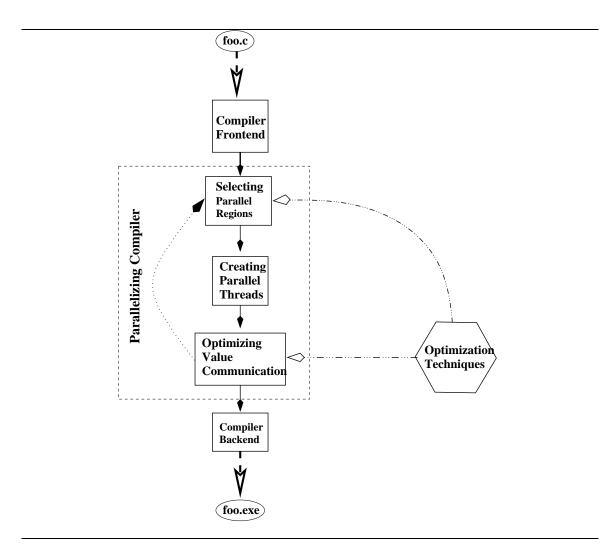

This chapter presents a thorough description of the hardware and software requirements for implementing thread-level speculation. It begins with a high-level introduction of the TLS execution model to establish the background for the rest of this chapter, followed by a section on the necessary hardware support. It then defines the hardware and software interface that allows the compiler to manipulate speculative execution. Finally, it demonstrates how various compiler passes can be combined to generate optimized parallel programs from sequential applications.

### 2.1 Execution Model

This section describes the TLS execution model targeted by the compiler, with particular focus on inter-thread value communication. This execution model targets a single-chip multiprocessor in which each processor has its own private first-level cache while sharing a second-level cache, as shown in Figure 2.1. A sequential program is

Figure 2.1: Basic architecture and execution model for TLS.

divided into threads, and each thread is assigned to a different processor. These parallel threads can be potentially dependent, but are executed *speculatively* in parallel. We rely on the underlying hardware to detect inter-thread data dependences and recover from incorrect execution. Figure 2.2(a) shows the life cycle of a single thread: each thread is first created by its predecessor through a lightweight fork, called a **spawn**, and executed in parallel with its predecessor. All threads must be committed sequentially to preserve the original execution order. This is achieved with the help of a *homefree token*: by obtaining this token, a thread can ensure that all previous threads have made all of their speculative modifications visible to the memory system and hence it is safe to commit. The thread that holds the token is *homefree*, and speculation succeeds if there is no inter-thread data dependence. This execution model allows us to exploit thread-level parallelism, as shown in Figure 2.2(b). However, when there is an inter-thread data dependence, the hardware will detect the dependence violation, and restart the thread containing the consumer of the dependence. All logically later threads must also be restarted, as shown in Figure 2.2(c).

#### 2.1.1 Inter-Thread Value Communication

The goal of this section is to examine the value communication mechanisms available under TLS from the compiler's perspective. TLS supports two forms of communication and the compiler can decide which mechanism is appropriate for a particular data dependence to obtain maximum parallel overlap:

**Synchronization** explicitly forwards a value between the source and the destination of a data dependence, as shown in Figure 2.3(a). It allows for partial parallel overlap and is thus suitable for frequently occurring data dependences that can be clearly identified. However, if the instructions that compute the communicating value are sparsely located in a thread, explicit synchronization could also

Figure 2.2: TLS execution model.

Figure 2.3: TLS value communication model.

limit performance by stalling the consumer threads more than necessary.

Speculation relies on the underlying hardware to detect data dependence violations at runtime and trigger re-execution when necessary, as shown in Figure 2.3(b). It allows for maximum parallel overlap when speculation always succeeds, however, if speculation always fails, this mechanism would introduce a significant performance penalty. Thus, this form of value communication is suitable for data dependences that are difficult to analyze and occur rarely.

### 2.2 Hardware Support

This section describes the hardware required to support speculative threads. There has been many proposals on hardware support for TLS [1, 15, 29, 31, 32, 43, 51, 63, 67], and a thorough treatment is beyond the scope of this dissertation. We will describe only the TLS hardware support used as the framework of this study.