# Tasks and Connection Sets: Choreographed Communication on a Reconfigurable Connection-Based Parallel Computer

Thomas E. Warfel April 1996 CMU-CS-96-155

School of Computer Science Carnegie Mellon University Pittsburgh, PA 15213

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering

Thesis Committee:

H.T. Kung, Chair Thomas Gross David R. O'Hallaron Daniel P. Siewiorek Jay Strosnider

Copyright ©1996 Thomas E. Warfel

This research was sponsored in part by the Defense Advanced Research Projects Agency/CSTO monitored by SPAWAR under contract N00039-93-C-0152, and in part by the Air Force Office of Scientific Research under contract F49620-92-J-0131. The views and conclusions contained in this document are those of the author and should not be interpreted as representing the official policies, either expressed or implied, of the U.S. Government.

#### Abstract

High-bandwidth, high-throughput applications with hard latency constraints are difficult to implement on a general-purpose parallel computer. Multiple developer-controlled "trial-and-error" cycles are usually needed before applications can reliably meet throughput and latency constraints, even on platforms having ample network bandwidth and computation power. Not only is reliable execution difficult to achieve for code developed in this manner, the code itself is difficult to modify or reuse without upsetting the delicate timing balance achieved.

Local computation performance can usually be bounded, but communication performance is often more difficult to predict. While hardware-supported connections can offer minimal quality-of-service bandwidth and latency guarantees, limited connection resources make scheduling the full application difficult. This thesis introduces a new approach: use multiple sets of connections, and allow tasks to perform local communication context switches and dynamically swap, within tasks, between statically scheduled sets of connections.

The mechanics of swapping connection sets, starting a task, and ending a task can be encapsulated into a small set of control primitives built upon fast, efficient barrier synchronization. If the control primitives are constructed to give predictable performance, the tasks created using those primitives will have predictable performance as well. Most important, complex tasks can be hierarchically constructed by assembling simpler tasks into larger structures while still maintaining predictable performance.

To demonstrate this scalable predictability, the TCS (Tasks and Connection Sets) programming model is introduced and implemented on a real target machine, iWarp. The prototype is used to implement a variety of communication patterns and then compared with fast message-passing implementations on the same machine. Finally, the scalable, hierarchical nature of TCS tasks is demonstrated by implementing a portion of a real-time computer vision application. TCS is shown to be well-suited not only for this application, but also for similar applications requiring continuous high-bandwidth input, low-latency output, and multiple computations per datum.

|  | e . |  |  |  |  |  |

|--|-----|--|--|--|--|--|

|  |     |  |  |  |  |  |

|  |     |  |  |  |  |  |

|  |     |  |  |  |  |  |

|  |     |  |  |  |  |  |

|  |     |  |  |  |  |  |

#### Acknowledgements

I would like to thank a number of people who enabled my completing this work. H.T. Kung, my advisor, for giving me the chance. Thomas Gross and Dave O'Hallaron, for the late-night/weekend meetings and discussions. Carl Love, Elaine Lawrence, and Lynn Philibin for guiding me through myriad vital paperwork over the years. Joseph Furman, who enabled me to keep my "dual identity" at Pitt while working at CMU. The support of friends here, especially Tom Stricker and Anja Feldmann, with whom many ideas were hatched and nurtured over the years and coffee. The members of the Nectar/iWarp research group, my office mates through the years, and the Carnegie Tech Amateur Radio club, for both critiques and moral support. Last but not least, my family, for their unflagging love, support and encouragement.

#### **Table of Contents**

| Chapter 1 - Introduction                             |

|------------------------------------------------------|

| Introduction                                         |

| Why TCS?                                             |

| The prototypical parallel target machine             |

| "Tasking" - sharing the load                         |

| Thesis 9                                             |

| Structure of thesis                                  |

| Chapter 2 - The TCS Programming Model                |

| The model for addressing the problem                 |

| Tasking under the TCS model                          |

| Task relations                                       |

| Utilizing reconfigurable connections                 |

| Implementing applications                            |

| Chapter summary                                      |

| Chapter 3 - Target Platform Communication Mechanisms |

| Target machine overview                              |

| iWarp array                                          |

| iWarp Communication agent                            |

| PCT-supported connections                            |

| Known system irregularities                          |

| iWarp platform summary                               |

| Measured iWarp communication performance             |

| PCT-based connection communication                   |

| RTS Message-passing communication                    |

| Deposit message-passing                              |

| Chanter summary 30                                   |

| Chapter 4 - Barrier Synchro | onization                             | 40 |

|-----------------------------|---------------------------------------|----|

| Introduction                |                                       | 40 |

| What is a ba                | arrier, and what does it do?          | 40 |

| Barrier prop                | erties                                | 41 |

| Issues affecting bar        | rrier synchronization implementations | 41 |

| The canonic                 | al barrier implementation             | 41 |

| Scalability o               | of a barrier implementation           | 42 |

| Barrier mess                | sage memory                           | 44 |

| Barrier skew                | /                                     | 45 |

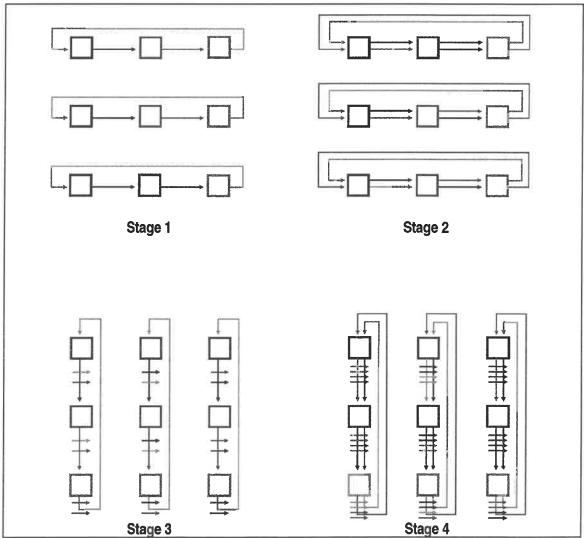

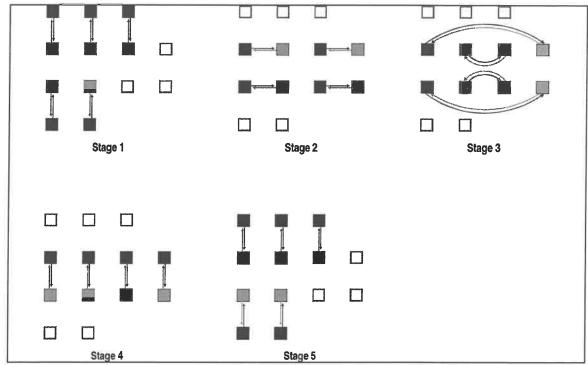

| Design Space for Ba         | arrier Implementations                | 45 |

| Physical sign               | naling scheme                         | 46 |

| Messaging p                 | protocol                              | 54 |

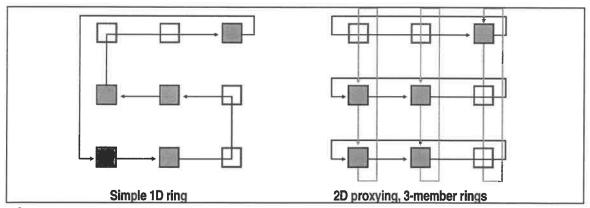

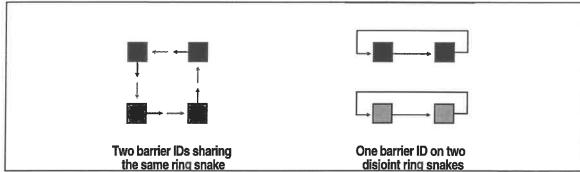

| Allowable ba                | arrier memberships                    | 70 |

| Barrier capac               | city                                  | 72 |

| Design methodology          | y                                     | 74 |

| The question                | ıs                                    | 75 |

| Crafting a barrier in       | plementation                          | 76 |

| Physical sign               | naling on iWarp                       | 76 |

| Non-broadca                 | ast messaging protocols on iWarp      | 77 |

| Putting it tog              | gether                                | 78 |

| Conclusions                 |                                       | 82 |

| Chapter summary             |                                       | 84 |

| Chapter 5 - TCS Control Pri | imitives                              | 85 |

| Introduction                |                                       | 85 |

| Connection set recor        | nfiguration                           | 85 |

| Reconfigura                 | tion model                            | 86 |

| Measured pe                 | erformance and predictions on iWarp   | 86 |

|                             | set reconfiguration conclusions       |    |

| Task creation                                       | 38 |

|-----------------------------------------------------|----|

| Task creation model                                 | 38 |

| Measured performance and predictions on iWarp 9     | 0( |

| Task creation conclusion 9                          | 0  |

| Task end 9                                          | 0  |

| Task end model                                      | 1  |

| Measured performance and predictions on iWarp       | 1  |

| Task end conclusions                                | 2  |

| Chapter summary                                     | 2  |

| Chapter 6 - TCS Validation - Communication Patterns | 4  |

| Introduction                                        | 4  |

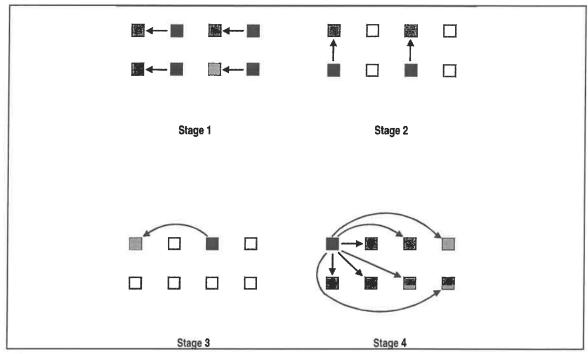

| Scatter/gather                                      | 4  |

| Scatter/gather - message-passing                    | 5  |

| Scatter/gather - TCS Connections                    | 6  |

| Scatter/gather conclusions                          | 8  |

| Reduction/broadcast                                 | 8  |

| Reduction/broadcast using message-passing           | 9  |

| Reduction/broadcast using TCS connections           | 1  |

| Reduction/broadcast conclusions                     | 2  |

| All-to-all communication                            | 3  |

| Message-passing implementation                      | 4  |

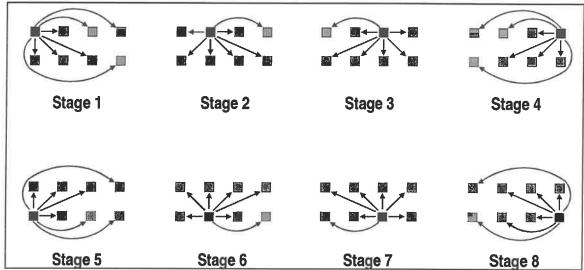

| All-to-all communication using TCS connections      | 6  |

| All-to-all conclusions                              | 9  |

| Chapter summary                                     | 9  |

| Chapter 7 - TCS Validation - Hierarchical Tasking   | 1  |

| Introduction                                        | 1  |

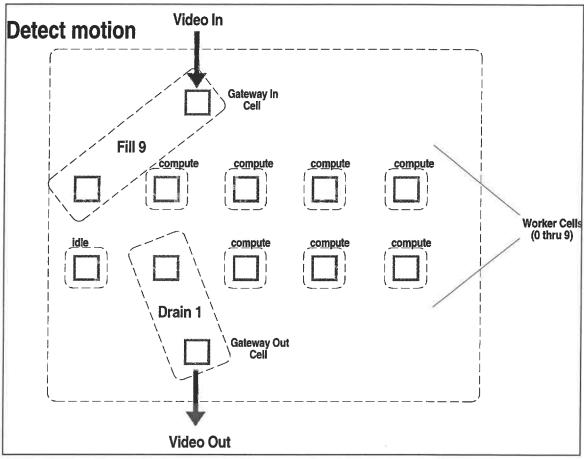

| Implementing the motion-detector                    | 2  |

| Requirements                                        | 2  |

| Utilizing multiple processors              |

|--------------------------------------------|

| The TCS implementation                     |

| Predictions                                |

| Throughput                                 |

| Latency                                    |

| Results                                    |

| Chapter summary                            |

|                                            |

| Chapter 8 - Related Work                   |

| Chip/Poker                                 |

| GF-11                                      |

| Polymorphic Torus                          |

| Transputer-based systems: C_NET and MARC   |

| iWarp, PCS, ConSet, and PCS+               |

| HeNCE(1991), CODE(1992), and Paralex(1992) |

| Orca-C and ZPL (1992)                      |

| Fortran M (1994)                           |

| Fx 126                                     |

| Mentat                                     |

| Static communication scheduling            |

| Chapter summary                            |

|                                            |

| Chapter 9 - Thesis Summary                 |

| Conclusions                                |

| Future work                                |

| Barrier hierarchies                        |

| Other platforms                            |

| Chapter summary                            |

| <b>Bibliography</b>                        |

# Chapter 1 -

### Introduction

#### 1.1 Introduction

High-bandwidth, high-throughput applications with hard latency constraints are often difficult to implement on a general-purpose parallel computer. Hardware-supported connections can offer minimal quality-of-service bandwidth and latency guarantees, but finite connection resources makes application scheduling difficult; machines usually lack sufficient connections to enable statically scheduling a complex application. Conversely, a purely dynamic connection resource allocation scheme may not be able to guarantee resource availability at run-time, which could lead to missed latency constraints. A hybrid approach that can work for many of these applications is to use multiple sets of connections, allowing tasks to perform *local communication context switches* and dynamically swap, within tasks, between statically scheduled sets of connections.

The mechanics of swapping connection sets, starting a task, and ending a task can be encapsulated into a small set of control primitives built upon fast, efficient barrier synchronization. Expressing the application using these primitives exposes the application's potential runtime communication complexity to the linker, which can then make globally-optimal communication resource allocations. One knows at link time whether or not sufficient resources exist to meet the run-time demands; there are no surprises with run-time resource unavailability. Furthermore, if the control primitives are constructed to give predictable performance, the tasks created using those primitives will have predictable performance. Most important, complex tasks can be hierarchically constructed by assembling simpler tasks into larger structures while still maintaining predictable performance.

To demonstrate this scalable predictability, the **TCS** (**T**asks and **C**onnection **S**ets) programming model is introduced and implemented on a real target machine, iWarp. TCS allows parallel tasks to perform **local communication context switches**, reliably swapping (in predictable time) between predefined sets of connections having guaranteed worst-case latency and bandwidth. Three key machine features are required to support TCS:

- (1) the network switches must allow their connection state to be directly configured by the local processing elements,

- (2) connections must be reliable and offer guaranteed worst-case bandwidth and latency, and

- (3) some form of fast, reliable barrier synchronization must be available.

Unlike message-passing communication (which handles all communication resource assignments at runtime), TCS requires that the connection sets (but not their usage patterns) be known at compile time; communication resource assignment is resolved at link time. This link time global foreknowledge of the permissible runtime connection states allows the TCS toolchain to make communication resource assignments that will meet the requested bandwidth criteria, or else return an error message at link time. If a TCS application successfully links, the requested connection sets are guaranteed to be available at runtime. Realtime problems having deadlines on the order of milliseconds can be addressed by solutions with execution times predictable to within a few microseconds.

To demonstrate the utility and validity of the idea, the TCS prototype was used to implement a variety of communication patterns representative of real application patterns. For comparison, the same communication patterns were also implemented using a fast message-passing system on the same machine. While message-passing and TCS both can provide fast, predictable performance for uncongested patterns, dense communications patterns (such as all-to-all) lead to unpredictable link congestion which causes message-passing to lose both performance and predictability. TCS is shown to maintain good, predictable

performance even with dense communication patterns.

Finally, the scalable, hierarchical nature of TCS tasks is demonstrated by implementing a portion of a real-time computer vision application. The vision application is realized as a TCS task constructed by assembling smaller TCS tasks. TCS is shown to be well-suited not only for this application, but also for similar applications requiring continuous high-bandwidth input, low-latency output, and multiple computations per input datum.

#### 1.2 Why TCS?

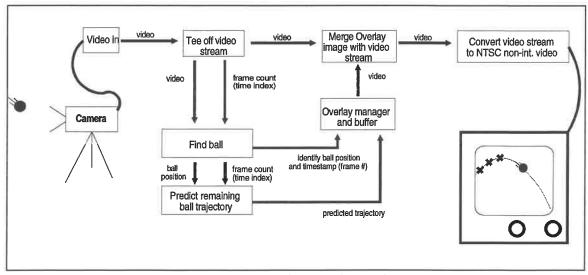

Consider the following problem: a ball is thrown through the field of view of a watching camera. A computer attached to the camera locates the ball in several consecutive frames, then plots a predicted trajectory for the ball. Current ball position and predicted ball trajectory are superimposed over a display showing the live camera video (Figure 1.1). No hardware-supported frame-buffers are used; the only special hardware is a fast, unbuffered analog-to-digital converter (which converts the incoming video pixels to binary numbers), a comparitor to detect video sync edges, and a digital-to-analog converter to convert an output stream of pixel values to an NTSC video output. The real-time nature of this problem is apparent in that the incoming video pixels must be sampled, forwarded through the system, and output to the video monitor in a timely manner. Latencies are additive,

Figure 1.1 Locate a thrown ball in a live video feed, then predict its future trajectory.

and thus for the system to be useful, the ball's position must be detected and future positions predicted and plotted all within one frame time. Otherwise, the result is just a "comet trail" drawn behind the ball on the screen. This is a fairly demanding (but statically schedulable) communication problem. What makes the problem interesting is that the "ball finding" computations and the trajectory prediction occur asynchronously with respect to the incoming video stream.

Other example applications with similar latency, computation, and throughput constraints include:

- (1) Phased array multi-sensor acoustic processing, such as an ultrasonic anti-collision system on a car's rear bumper;

- (2) Phased array sonar processing [35,36];

- (3) Real-time medical imaging, including:

- (a) correcting for patient movements in the imaging plane "on-the-fly" while doing functional (multiple scan) MR imaging;

- (b) precisely quantifying radiation therapy dosages by generating a CT-like image "on-the-fly" from the radiation treatment (realtime noninvasive internal dosimetry), and comparing these against prior, conventional CT (Computed Tomography) scans used for dose planning, so that treatment can be redirected or aborted if sensitive tissues (such as the spinal cord) become overly-irradiated. Off-line portal image evaluation is discussed in [19] and [31] to detect damage inflicted, but on-line realtime 3D internal dosimetry is not yet practiced.

While by no means an exhaustive application list, the scope is broad enough to draw some generalizations. Common features shared by these examples include:

- 1) Large amounts of computation (multiplication and addition) are required per data point.

- 2) Real-world data is sampled in high-bandwidth, time-critical bursts.

- 3) The problems have some inherently parallel aspect, whether it

- be multiple sensors acquiring data to be processed, or whether it be the means by which the data itself is processed

- 4) The output of the process has a time-critical nature; the output is often used as feedback in some sort of control loop which may or may not be completely automated (that is, a human may be in the loop).

#### 1.3 The prototypical parallel target machine

A parallel computer exists as a group of *cells* interconnected via a communication network. Each cell is a single functional computer within the larger parallel machine, complete with processor, local memory, specialty I/O devices (if any), and a connection to the machine's communication network. While some architectures may use more than one processor per cell, for the purposes of this thesis the cell is treated as the smallest functional computing unit. Due to the real-time nature of the applications being addressed, stand-alone cells must offer predictable execution times.

Fast, predictable, low-latency interprocessor communication emerges as a requirement for this parallel machine. While not an explicit part of any application definition per se, little is gained if multiple cells can acquire high-speed data in parallel but cannot pass that data on for correlation at the same rate. Buffering can compensate for small discrepancies in bandwidth, but the basic communication capacity needs to be available. Fast communication involves two major issues: the communication protocol used (how two cells talk), and the network implementation (which cells can talk to which other cells, how fast can they talk, and how many can talk at once).

Conventional supercomputers often accept high latencies as the price for high bandwidth, and accordingly pipeline their computations and data transfers in huge blocks[45,47]. For instance, while image N is being computed, data for image N+1 is being loaded, and image N-1 is being written out. If the computation goal is just to generate weather maps, this pipeline latency is not a problem. Due to the time-critical nature of

applications such as those listed in section 1.2, though, long pipeline delays cannot be afforded. A driver backing up needs to know what's behind the car <u>now</u>, not what was behind the car several scans ago.

While general-purpose message-passing (such as offered by MPI libraries[15,27]) is a commonly used communication paradigm for parallel machines, a number of characteristics make it undesirable for the types of applications discussed. First of all, the overhead and unpredictable delays an interrupt-driven messagepassing system implies can't be afforded in a real-time control problem. Second, message-passing systems typically evaluate routing issues ("how do I send a message from A to B") on a message-by-message basis at runtime. For all the applications shown, the necessary communication patterns can be worked out at compile time. The precise usage of those communication patterns may be unknown, but the patterns themselves can be known. It is far more efficient, then, to work out the communication resource and routing assignments once, when compiling or linking, rather than re-evaluating them for each and every message sent at runtime [17,22].

Instead of message-passing, a connection-like mechanism is needed for communication between processors. A connection acts as a "first-in, first-out" buffer connecting the output of one cell to the input of another. Data written into the connection (from the output of the sending cell) is available to be read out (at the input of the receiving cell) in the same order it was written in. The actual means by which connections are implemented is unimportant, provided that the implementation can offer minimal-quality-of-service bandwidth and latency guarantees, and that an adequate number of connections can be supported. These guarantees are necessary to insure that processors can forward data fast enough to keep up with input data bursts.

Point-to-point wires between communicating cells are the most direct means of supporting connections. This approach has several difficulties, the biggest being that communication paths are

essentially "programmed with solder"; reconfiguring to support different communication patterns becomes impossible. Supporting multiple applications, each having different connection requirements, on a machine with finite resources, implies the ability to reconfigure the machine between application runs.

The ability to reconfigure connections while running an application (and not just between applications) is also desirable. To provide low-latency communication, any connection implementation requires some sort of direct hardware support. Because low-latency connections must rely on a finite physical resource, the total number available will have some finite limit. If an application requires more connections than the underlying implementation is able to support at one time, the application's needs could still be met if the implementation supports reconfigurable connections. Reconfigurable connections allow resources to be allocated that guarantee minimal-quality-ofservice for one connection, and when the connection is no longer needed, those resources can be revoked and reallocated to support another connection. Because most parallel applications exhibit a "locality of communication", only a few connections are usually needed during any particular stage of program execution[17]. Thus, a few reconfigurable connections are usually adequate to meet an application's needs.

#### 1.4 "Tasking" - sharing the load

Once a specific parallel system is established as sufficient to meet the application's requirements, the challenge becomes mapping the application components, or tasks, to different cells within the machine. A task is a functional unit of computation; all applications consist of one or more communicating tasks. The specific cells that a task is mapped to are referred to as that task's allocation. Two tasks running on different cell allocations are said to be parallel tasks. Two non-communicating tasks which have at least one cell in common between their cell allocations are said to be sequential tasks; they cannot both run at the same time. A task will not execute until all the cells of its allocation are ready to run that task.

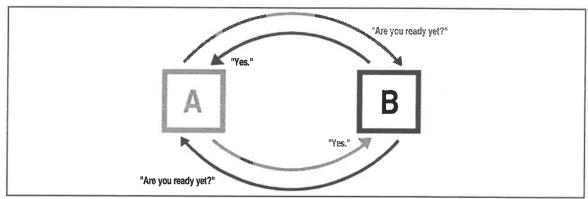

Parallel tasks may either be synchronous or asynchronous. In a synchronous tasking model, all tasks start together and end together, much like a marching band. The brass, woodwinds, and percussion all start together, march together, and stop together. If an application requires multiple task sets over time, a global barrier separates the different task sets so that all tasks in a set begin together. Everything runs on a fixed schedule which must make worst-case assumptions; thus, tasks can be blocked due to conditions entirely beyond their concern. In a more flexible, asynchronous tasking environment, a task will only block until the resources it needs are available, then execute. This model more closely resembles dinner in a restaurant: arriving parties are seated and served as tables become available. Once the resources become available (a sufficiently large table becomes free), dinner proceeds independently of the other parties in the restaurant.

Actually, the restaurant analogy can be extended to illustrate some of the problems of synchronous tasking on a large parallel system. Consider a large catered dinner event, such as a wedding reception. In this case, arriving parties are seated and left to sip ice water until all other guests have been seated. Meanwhile, the servers are left standing idle. Once all guests are seated, the meal is served one course at a time. If a sufficient number of servers are available, all guests are simultaneously given their soup, then the soup bowls are cleared away. All guests are simultaneously given their salad, then the salad bowls are cleared away. No guest receives a salad until the last guest has had his soup bowl removed. Unfortunately, most catered dinners suffer from limited "busboy bandwidth". Food service is not simultaneous, but rather occurs in a wave, as the servers shuttle food from kitchen to successive tables. Guests who have finished their soup are forced to wait until all other guests have finished their soup before they can begin their salad. The larger the group of guests (or the larger the number of processors in the machine) the worse this "wave of waiting" becomes. Globally synchronous execution in a parallel machine not only forces cells to wait for their neighbors at each stage, but also magnifies the problems of finite communication bandwidth. The asynchronous

tasking model means cells spend less time waiting, but allocating communication resources becomes a more difficult problem.

The problem, in essence, is "**how** can one combine connection-based communication (which implies static scheduling/resource allocation), with a flexible tasking model (which inherently involves dynamic resource allocation)?"

#### 1.5 Thesis

By placing some restrictions on the tasking model (statically allocating the potential communication resources an application may need), the application goals (multiple interacting tasks, high-bandwidth I/O, multiple computations per data point, hard latency constraints) can be met while maintaining effective processor utilization. Given a parallel computer with connections having guaranteed minimal-quality-of-service and a local connection state that is directly-writable by the local computing cell, one can construct a small set of barrier-based control primitives that yield predictable performance. By exposing the communication complexity to the linker, these primitives can be used to create parallel tasks which also exhibit predictable performance, and those tasks can in turn be hierarchically assembled to create even more complex tasks while still maintaining predictability.

A prototype programming system, TCS, was created to demonstrate the validity of this hypothesis. TCS applications are composed of tasks that communicate via sets of unidirectional connections. Tasks can be hierarchically constructed by assembling simpler tasks, and complex communication patterns can be expressed as a series of local communication phases within the task. Tasks (with latency constraints in the tens to hundreds of microseconds) are built with a small set of barrier-based control primitives which offer predictable (to within a microsecond) performance. Properly constructed, tasks using these primitives also exhibit predictable execution times and can be assembled into more complex tasks that maintain their predictability. Their communication resources are statically scheduled by the linker as sets of connections within

each task, but dynamically invoked by the task at run-time.

#### 1.6 Structure of thesis

The next few chapters explore the characteristics of TCS connection-based communication and explain the hierarchical nature of the four TCS control primitives: barrier synchronization, local communication context switch, task start, and task end. Both the communication and the control primitives are implemented on a real target machine, and their performance is measured and compared with predicted performance.

Chapter 2 explains the TCS programming model in more detail and explains the functions of the barrier synchronization, local communication context switch, task start, and task end primitives.

Chapter 3 introduces the target machine, iWarp, and outlines the three major communication mechanisms it provides: *PCT-supported connections*, *RTS message-passing*, and *deposit message-passing*. These communication mechanisms are explored and characterized. PCT-supported connections are the mechanism used to implement TCS connections.

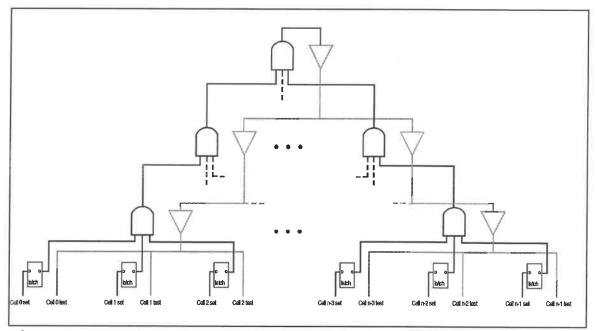

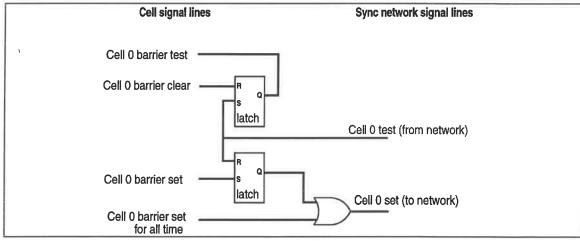

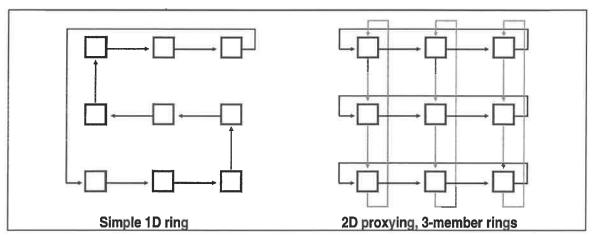

Chapter 4 deals with barrier synchronization: what it is, relevant aspects, and ways to implement it. The interaction between a barrier implementation's physical signaling scheme and messaging protocol is first predicted, then illustrated by constructing and benchmarking barrier implementations built from the three communication mechanisms introduced in Chapter 3. Based on these results, a 1-D (N-1) ring built using PCT-supported connections is chosen as the basis for the TCS barrier primitive.

Chapter 5 introduces the remaining TCS control primitives. The barrier primitive introduced in Chapter 4 underlies all dynamic resource allocation at runtime, and it is used in constructing the remaining three primitives: local communication context switch, task start, and task end.

Chapter 6 uses the TCS control primitives and a prototype

connection linker to create three single-task communication patterns representative of real application communication: scatter/gather, reduction/broadcast, and all-to-all. The TCS implementations are shown to have predictable (within a few percent) performance regardless of transfer size and number of cells. A message-passing implementation, based on deposits, was shown to have comparable performance and predictability with simple patterns on an unloaded machine, but as congestion increased, message-passing was unable to maintain predictable performance.

Chapter 7 demonstrates the hierarchical nature of TCS tasking, constructing a real-time video-rate motion-detector by assembling several simpler tasks. This composite task was predicted to meet video requirements as it was assembled, then it was benchmarked to verify predicted performance.

Chapter 8 discusses related work which is significant for using sets of connections, dynamic tasking on a parallel machine, or both.

Chapter 9 is the conclusion and summarizes the key points of the thesis.

## Chapter 2 -

## The TCS Programming Model

#### 2.1 The model for addressing the problem:

TCS (for Tasks and Connection Sets) is a general computation model for reconfigurable connection-based parallel machines which exploits certain machine properties. In particular, special advantage is taken of hardware-supported, low-latency connections for communication within and between running tasks. Task-internal communication, and the synchronization barriers needed for connection resource management, are all concealed within the task that decouples the task's internal execution from its neighbors. Communication between tasks is self-synchronizing and is the only synchronizing operation crossing task boundaries.

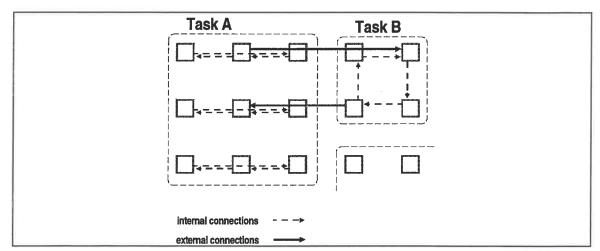

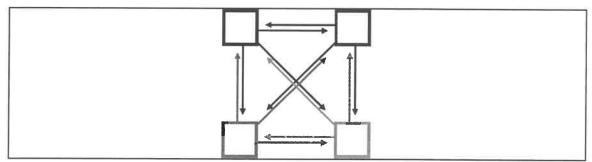

Under this model, all communication occurs through unidirectional connections. Connections provide communication both within tasks (internal connections) and between tasks (external connections)

Figure 2.1 Cells within a task communicate via internal connections. Inter-task communication occurs via external connections.

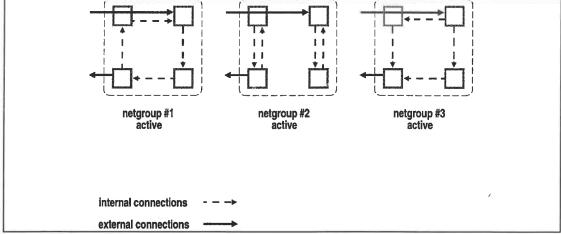

(Figure 2.1). While the external connections persist for the lifetime of a task, internal connections within the task may be reconfigured under the task's local control. Connections are grouped into networks, and networks are in turn grouped into netgroups. A netgroup is just a set of local connections. A connection may only belong to one network, but a network may belong to more than one netgroup. A task may have only one netgroup active at any time. A connection is active if the network it belongs to is in the active netgroup; active connections may be used for communication. If the connection does not belong to the active netgroup, no communication resources are supporting it and it may not be used for communication. Tasks can perform communication context switches to change the active netgroup.

Good candidate applications for the model have the following characteristics:

- (1) they process multiple "sets" of data;

- (2) they can be expressed as a collection of communicating tasks, each task having:

- (a) a fixed set of communication patterns (but not necessarily knowledge of the order in which the patterns will be used), and

- (b) a good estimate of required execution time, though the actual run time may have data dependencies.

Having a fixed set of communication patterns allows static allocation of the communication resources, which in turn allows making some guarantees about minimum runtime communication performance. Having an accurate estimate of task execution time is important when mapping tasks to cells; using too few cells to support a task could result in a computational bottleneck, and using too many is a waste of resources.

Purely systolic applications, with a static set of connections ordered at compile-time, can be cleanly implemented using TCS, but would not see a substantial benefit over globally synchronous tasking models. TCS will allow efficient use of systolic tasks as part of a larger, non-systolic application, though.

The benefits of using the TCS model include:

- (1) support for mapping problems (such as the examples shown) onto realizable parallel architectures;

- (2) the ability to express loosely-coupled tasks without any artificial couplings; there is no requirement for the developer to construct artificial global phases. Eliminating artificial couplings enables faster performance by eliminating unnecessary synchronization barriers.

#### 2.2 Tasking under the TCS model

TCS tasks rely on cell-to-cell connections and four control primitives: barrier synchronization, connection reconfiguration (also known as a communication context switch), task start, and task end. Connection (communication) performance is a function of the underlying hardware and communication resource scheduling. In the next few chapters the performance of the control primitives are characterized and (most important!) shown to be predictable (to within ten percent or better) using simple models. Barrier synchronization is the fundamental primitive upon which both connection reconfiguration and task start are both based. In fact, the TCS control primitives are hierarchical in nature, and thus a fast barrier implementation is a key implementation concern because it is repeatedly encountered at each hierarchical tasking level.

Tasks consist of program code executing on a predetermined (at link time) cell allocation as a coordinated entity, together with all communication generated by that program code, and the external ports used to communicate with other tasks. A task begins execution when it is invoked (task start) by a parent task; parent task operation is suspended on those cells, and the child task executes. When the child task terminates, parent task execution resumes. The lifetime of a task lasts from when all task members (the cell allocation) complete a barrier synchronization on task startup, until all members complete a barrier synchronization on task termination. Only one task may be actively executing on a single cell at a time.

A parent task can pass *invocation parameters* to the child tasks it starts. Each cell in the parent task's allocation passes the same set of parameters to the child task, but the values of the parameters can vary from cell to cell.

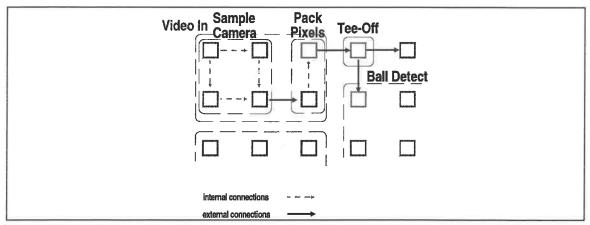

For example, consider Figures 2.2 and 2.3. In 2.2, an application is starting that includes the tasks **Video In**, **Tee-off**, and **Ball Detect**.

Figure 2.2 Three of the tasks used in the "predict and plot the ball's trajectory" example.

Video In then invokes two child tasks, Sample Camera and Pack Pixels (Figure 2.3). Sample camera acquires data from four video cameras at once (4 bytes, 1 byte per camera, packed as one 32-bit word), and forwards the data to Pack Pixels, which takes 4 words, discards data from the 3 irrelevant cameras, and packs the 4 bytes

Figure 2.3 Video In has invoked two children, Sample Camera and Pack Pixels.

of data from the relevant camera into a new word and outputs it using an external connection inherited from the parent task (**Video** In). Thus, the complex task **Video** In has been constructed by assembling two simpler, smaller tasks.

#### 2.3 Task relations

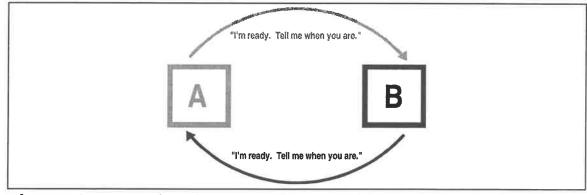

As a task begins execution, all members of the task's cell allocation synchronize to verify that all cells needed to run that task are indeed ready. If the task has any "personal" external connections (as opposed to an external connection inherited from a parent), the local work needed to set up an external connection is done, and another synchronization is performed, which now includes both communicating tasks' cell allocations. This second barrier is necessary to ensure that no data is sent before the receiving end of the connection is established. External connections persist for the entire lifetime of a task, hence, an additional barrier synchronization is necessary between communicating tasks when the task terminates to ensure the connection is no longer needed before tearing it down.

Because only one task may be actively executing on a cell at a time, tasks with overlapping cell allocations may not execute concurrently. Therefore, concurrent tasks that need to communicate with each other must be mapped onto the machine such that their allocations do not overlap. Conversely, if a task wishes to invoke a child task, the child must lie entirely within the allocation of the parent task. If a task wishes to invoke two communicating child tasks, both must lie within the parent's allocation without overlapping (See Figure 2.3).

Child tasks have limited external communication options: they may have external connections between themselves and other (non-overlapping) child tasks invoked from the same parent, or they may communicate with tasks external to the parent's allocation via external connections inherited from the parent. Child modules may not create new external connections extending outside the parent's cell allocation; this restriction is necessary to keep the encapsulation "pure". The parent module presents a particular

interface to the application. If an invoked child were to "reach out" of the parent's allocation without the parent's express knowledge, the parent module's interface would no longer be sufficient: a calling task (or application) would need to know about both the parent and the child. Because knowledge of the parent's interface alone would no longer be sufficient, the parent's ability to encapsulate communication complexity would be lost. By allowing child tasks to inherit a parent's external connections, complicated multi-stage tasks can be assembled from a collection of simpler tasks, while concealing the internal complexity from the calling task or application. For example, in Figure 2.3, Pack Pixels is shown inheriting the external connection from Video In to Tee-Off.

A parent task may communicate with its child only via parameters and pointers; there is no concept of a connection between a parent and child because parent execution suspends while the child task runs. Parent tasks may invoke children to an arbitrary depth, but recursion and reentrancy are expressly forbidden. The absolute depth of task invocation must be known at link time to ensure adequate communication resources can be available at runtime. If variable depth recursion were allowed, runtime resources could not be guaranteed at link time unless some arbitrary depth limit were pre-established. The depth limit approach is unacceptable because

- (1) all scheduling would have to assume the worst-case depth limit, resulting in inefficient resource utilization, and

- (2) some program would inevitably try to exceed the preestablished limit at runtime and crash, violating our guaranteed predictability.

Thus, to ensure predictability and allow efficient resource allocation, the absolute depth of task invocation must be known at link time.

#### 2.4 Utilizing reconfigurable connections

All communication within and between tasks occurs via unidirectional **connections**. A connection is a long-lived bandwidth reservation between a source port on a source cell and a destination port on a destination cell. Data put into the source

port is guaranteed to be available at the destination port within a time interval determined by the connection's level of service. A port is a software construct belonging to the task which makes the connection (which is really just a bandwidth reservation) accessible to the program code. While it is realized by specific hardware resources belonging to the cell, it is managed as an entity belonging to the task. A connection can be thought of as a pipe connecting two cells; the ports are the openings of the pipe. Data poured into the uphill end of the pipe flows out the downhill end.

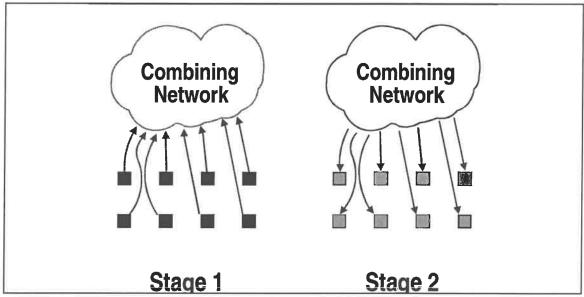

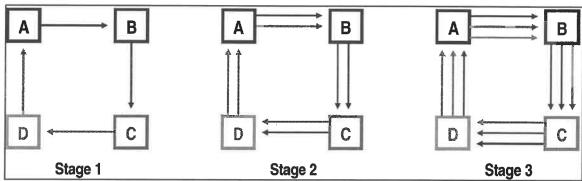

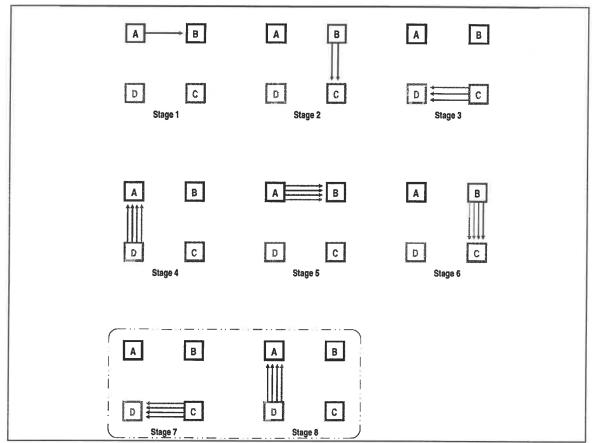

All communication between cells within a task occurs via internal connections, defined by a source cell, source port name (needed by the source cell code), destination cell, destination port name (needed by the destination cell code), and an optional bandwidth reservation. Connections used together are grouped by the application developer (or a higher-level compiler) into networks. Task-local communication phases, called netgroups, are defined by grouping networks together. A connection may only belong to a single network, but a network (and hence its connections) may belong to several netgroups (Figure 2.4). All aspects of internal connections (connections, networks, and netgroups) are entirely contained within the task definition. Only one netgroup may be active within a task at a given time.

Figure 2.4 Netgroups allow finite physical connection resources to support multiple local communication phases.

Communication between tasks occurs through external connections, which join external ports on each task. External ports may either be defined as part of the task, or may be passed in to a child task from a parent. Because external connections are not wholly owned by the task (the task only owns one of the external ports, and cannot specify bandwidth), external connections need to be defined by a higher-level (parent) task, or at the application level.

If a task has external ports, a barrier synchronization is required at the beginning of task execution covering all cells belonging to both communicating tasks, ensuring that all cells of each task's allocations are ready. This operation is necessary to ensure no data is sent via an external port before the connection is established. Similarly, another barrier is required at task termination to ensure all communication stops have completed before reclaiming the external connection resources. Barrier synchronizations are also needed whenever a task changes the active netgroup, but requires only the participation of the task's cell allocation. No other cell, external controller, nor any other agent outside of the task's allocation is required to participate when changing the active netgroup. Connection reconfiguration within a task occurs purely under local control.

Note that all connections are defined by endpoints and bandwidth; no routing information is included as part of any connection definition. The mapping of connections to physical communication resources, including their routing on the target machine, is the linker's concern, not the application designer's.

#### 2.5 Implementing applications

Applications exist as one or more communicating tasks executing on physical cells on a real machine. A TCS "program" isn't a single entity; it exists as a database containing the executable program code for each task for each cell, as well as the hardware-specific connection resource mappings for each cell. A TCS program is created by mapping the cell allocations of specific module

instances to specific cells on a target machine, linking the program code of the tasks and their children for the individual target machine cells, routing the connections and assigning specific hardware resources to support those connections, evaluating what barrier synchronizations memberships are needed, and assigning the necessary resources, then creating the loadable images for code, synchronization, and communication. To run a TCS application, the program code, synchronization information, and communication information must be loaded onto all cells in the machine, then all cells can begin execution.

#### 2.6 Chapter summary

This chapter introduced the TCS programming model. TCS applications are constructed from multicellular tasks which communicate by means of unidirectional connections. Internal task communication occurs via internal connections, which are grouped into networks, and networks are grouped into sets called netgroups. Only one netgroup may be active at a time; tasks may perform local communication context switches to change the set of active connections from one netgroup to another. External connections support communication between tasks and persist for the lifetime of the task. Task execution is controlled using a small set of primitives: task start, local communication context switch, and task end. These primitives are all built upon a fourth control primitive, barrier synchronization, which will be covered in more detail in Chapter 4.

### Chapter 3 -

### **Target Platform Communication**

### Mechanisms

The last chapter introduced the TCS machine model and the notion of TCS connections. This chapter introduces iWarp[12], the target machine, and shows how TCS connections can be supported on this hardware. Two different message passing implementations, RTS message-passing and deposit message-passing, are introduced for comparison, and the performance of TCS connections and message passing communication are characterized in isolation on an unloaded machine. While both message passing and TCS are shown to offer good performance and predictability for large transfers, TCS maintains a substantial performance advantage for small transfers.

#### 3.1 Target machine overview

An iWarp array is the target platform used to validate the TCS model because it offers a rich set of communication hardware that allows fair comparisons of different communication models.

#### 3.1.1 iWarp array

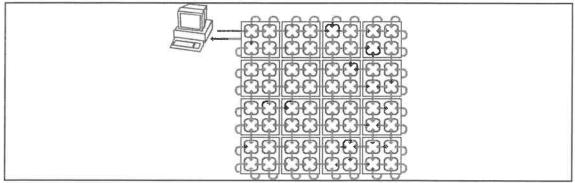

The target machine is composed of 64 processing cells arranged as an 8x8 torus, plus one host-interface cell (Figure 3.1). Each

Figure 3.1 The iWarp array configuration - an 8x8 torus plus a host interface.

cell is composed of an iWarp chip (or iWarp component) plus 512K static RAM. Each iWarp component contains a VLIW CPU (the computation agent) and a network interface (the communication agent).

#### 3.1.2 iWarp Communication agent

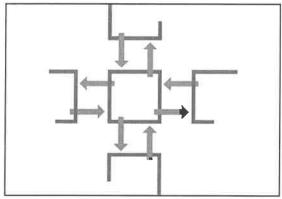

Figure 3.2 iWarp connectivity.

Each communication agent has eight external physical network connections, four in and four out. These are designated as X or Y, Up/Left or Down/Right, and In or Out. Each external network connection has a maximum bandwidth of 40 MB/sec (Figure 3.2).

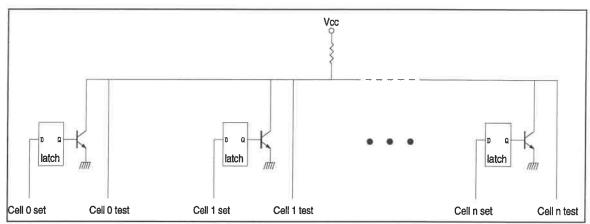

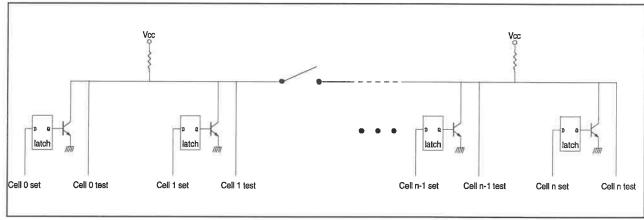

Internally, the communication agent has 20 eight-word FIFOs known as **PCT**s. Each PCT can be configured to receive data from an external physical network connection or from the computation agent, and each PCT can send data either to an external network connection or to the computation agent.

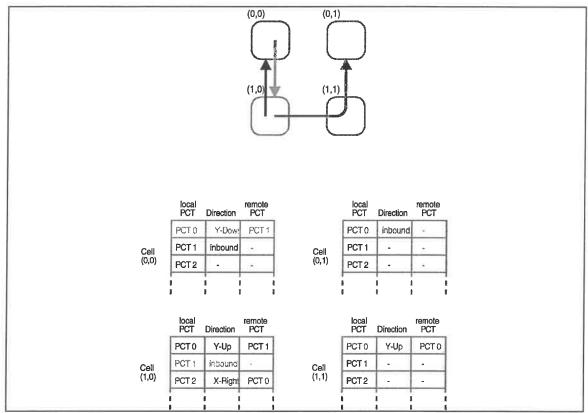

#### 3.1.3 PCT-supported connections

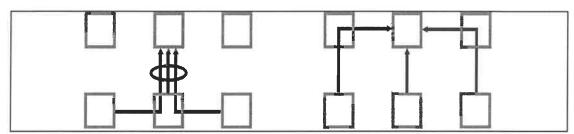

Connections are built by chaining together PCTs on adjacent cells, building a contiguous path from source to destination (Figure 3.3). A connection consumes physical link bandwidth only if it is actively forwarding data. If two connections share the same physical link but only one is carrying data, the one carrying data gets full link bandwidth. If both connections are actively carrying data, each gets only half the link bandwidth, multiplexed between them on a word-by-word basis. For a given connectivity, congestion (and therefore available bandwidth) depends on both routing and connection activity. In Figure 3.4, both examples show a connection from each cell in the bottom row to the center cell in the top row. In the left-hand example, if all three

Figure 3.3 Example PCT configuration illustrating how three connections could be supported via PCTs

connections are active at once, only one-third of the physical link bandwidth is available to each connection. In the right-hand example, the same source/destination connectivity is provided, but no congestion occurs - each connection is routed over a different physical network link.

Figure 3.4 For a given connectivity, the routing affects the maximum bandwidth available.

The computation agent can read or write from connections by accessing the PCTs of the communication agent either through **gates** or **spools**. A **gate** is a special register that can map an iWarp

component's PCT in the communication agent into the computation agent's register file. CPU operations treat a gate like any other register, but reading a gate pulls data from the front of the mapped PCT's FIFO. Writing to a gate appends data at the back of the PCT's FIFO. Each iWarp component has two read-only gates and two write-only gates, which can be mapped to any of the twenty PCTs.

A **spool** is a hardware feature that provides DMA-like transfers between a block of memory and a PCT. Each active spool "steals" up to one-third of the computation agent's CPU cycles, but requires no other direct CPU action once a transfer has been started.

Connections may be created (or destroyed) by one of two mechanisms:

#### (1) Source routing

Special tagged words may be launched at the connection's source that automatically set the state of the communication agents as they pass through the array. PCT assignments dynamically occur as the communication agents forward the connection header along. The computation agent at the destination can be notified of an incoming connection either by polling or by an interrupt, depending on how it has configured its communication agent.

If a resource needed to complete a route is busy, the communication agent will block the connection until the resource becomes available.

#### (2) Direct configuration

As the name implies, with direct configuration the computation agent directly writes the state of the communication agent to set a specific PCT configuration. While source routing requires only computation agent participation at the source and destination of a connection, direct reconfiguration requires the active participation of computation engines along the entire path from source to

destination. Furthermore, while the communication agent is responsible for PCT assignment/reclamation in the source routing approach, direct configuration requires all PCT assignments to be known prior to runtime. Direct configuration offers two potential performance advantages: the state of the communication agents along the route of a connection can all be configured together in parallel, and multiple connections can be configured in parallel. source routing, as a connection header makes its way through the system, it must sequentially configure the state of the communication agent at each step of the way. With direct configuration, the state for the entire path can be configured at once. Furthermore, with source routing, a cell can only launch one connection header at a time. With direct configuration, an entire set of connections may be established simultaneously.

Because direct configuration requires the participation of cells other than just the connection source and destination, some form of **barrier synchronization** is needed whenever a connection state change is needed. For instance, in Figure 3.3, the connection from cell (1,0) to (0,1) passes through (1,1). Cell (1,1) needs to be certain the connection is no longer needed before it reclaims the PCT.

#### 3.1.4 Physical communication schemes

PCT-based connections form the basis of all iWarp communication mechanisms, but how those connections are used yields three very different physical signaling mechanisms.

#### 3.1.4.1 PCT-supported static (TCS) connections

TCS connections are implemented using the direct configuration approach but allow for PCT subsets to be configured; that is, a TCS module may only need to reconfigure PCTs 1 through 8, and will leave the remaining 12 (which may be supporting other connections or the runtime system) alone.

#### 3.1.4.2 RTS message-passing

The iWarp runtime system, or RTS, is a low-level system monitor that allows programs to be loaded and executed on array cells, provides proxy I/O service for the array cells, and allows a cell's internal state to be examined or modified by the host. To provide these services, the RTS requires a communication system that provides connectivity to all cells with minimal use of cell resources. The RTS communication system is implemented as a general-purpose message-passing system built upon a unidirectional token-ring communication structure. Each cell forfeits two PCTs to the runtime system to build a large, single closed-loop connection that passes through all cells exactly once; this loop then supports a token-ring-like communication mechanism. At boot time, the host interface cell injects a token into this closed ring; the token circles endlessly until a cell requires RTS services. When a cell needs to send a message, it acquires the token, then injects its message into the ring. The message follows the ring until it reaches its destination, upon arrival it signals an interrupt at the destination cell, and the destination cell consumes and processes it. An acknowledgment is sent from the destination in a ringward direction until it reaches the message source. The source consumes the acknowledgment then reinjects the RTS token into the ring.

This communication mechanism, RTS message-passing, is available to user programs and provides a simple means for any two arbitrary cells in the array to communicate. All communication requires circumnavigating the array at least once (the message travels partway around the ring; the acknowledgment completes the round-trip), generating interrupts at the source and destination cells (and consequently causing in program context swaps). Only one cell pair can use the ring at a time, therefore, the total bandwidth available through this mechanism is limited, especially impacting multiple short message transfers which could otherwise occur in parallel.

#### 3.1.4.3 Deposit message-passing

Deposit message-passing is an iWarp communication library [42,43]

providing message-passing services similar to RTS message-passing, but with vastly improved performance. Features include: multiple cells can send at once, cells can receive and send at the same time, and fewer copies and program context swaps are used when communicating. The sender specifies the address of the buffer to be used by the receiver. Deposit message-passing requires nine PCTs and two spools be dedicated to the message-passing system, but allows all cells to send and receive at once. Messages are implemented as source-routed dynamic connections. Only one message at a time is supported over a physical network link, but the message has the full link bandwidth available to it once it does go through. The PCTs used by a message are immediately deallocated as the message trailer passes through each of the communication agents along its route. Routing is calculated onthe-fly when a message is launched. Unlike RTS message-passing (or even Nx-based message-passing), deposit message-passing assumes a pre-allocated memory buffer at the destination so that protocol overhead is much reduced. This reduced processing overhead in turn results in a more efficient implementation.

In summation, three general communication options are available on the iWarp:

- (1) static PCT-supported connections, which are routed prior to runtime and can last longer than just one message time,

- (2) RTS message-passing, which provides a token-ring like communication system, and

- (3) deposit message-passing, which uses source-routed dynamic connections and allows simultaneous sending and receiving by all cells at once.

TCS connections are a special form of static PCT-supported connections that allow small groups of cells to reconfigure independently of the rest of the array without disturbing existing connections passing through the cells.

#### 3.1.5 Known system irregularities

While the iWarp is a good target platform, it has a few eccentricities that make accurate performance prediction difficult, but not impossible.

#### 3.1.5.1 Network contention unfairness

In theory, multiple connections sharing a physical network connection share the bandwidth fairly. In reality, the on-chip pathway scheduler views PCTs as four groups of five PCTs each. Each pass through the scheduler (for each of the four outgoing physical connections) the scheduler looks at the four groups in a round-robin fashion, and chooses a PCT within that group in a round-robin manner. If a group has no PCTs with data to send, that group is skipped. Thus, scheduling is fair if all PCTs with data to be sent lie within one group, or if the same number of PCTs lies in each of the different groups. Otherwise, PCTs belonging to groups with a small number of active PCTs get a disproportionately higher percentage of bandwidth.

For example, consider three PCTs with data in group one, and one PCT with data in group two, all competing for the same outgoing pathway. The one PCT in group two would get one-half of the physical pathway bandwidth, and each of the three PCTs in group one would get one-sixth of the physical pathway bandwidth (rather than one-fourth as expected under a fair scheduling scheme).

#### 3.1.5.2 DQ contention

Every PCT that receives a word from a network connection must return an acknowledgment word to the cell that sent the data. This acknowledgment word is called a DQ (short for "dequeued message acknowledgment") and is carried on a special, physically separate link parallel to the data link but running in the reverse direction. In an ideal world, the DQ bandwidth would be the same as the forward link bandwidth. Unfortunately, under certain conditions, when multiple connections pass through a cell and at least one connection changes direction in the cell (for example, the message had been going up but turned left at the cell), congestion occurs within the cell's DQ-processing hardware, and DQs are forwarded in an unfair manner. This amount of congestion can be predicted, and if the forward links are fed no faster than the congested rate (by intentionally sending data at a reduced rate), forward pathway bandwidth is shared fairly (within the constraints of Section 3.5.1). If one tries to feed the forward

pathways faster than the DQ congestion-limited rate, the DQ signals are returned in an unpredictable manner, and forward data flow is choked by the lack of DQ signals showing available buffer space.

#### 3.1.5.3 Uneven forward link bandwidth

Theoretically, the iWarp is supposed to deliver 40Mbytes/sec on each pathway. In reality, the scheduler tends to "skip" sending a word every thousand words or so, yielding a true bandwidth closer to 39.96Mbytes/sec.

#### 3.1.6 iWarp platform summary

While the communication hardware has a few anomalies, they are known and can be accounted for in performance models that maintain detailed knowledge of the underlying PCT assignments.

Three general communication methods are available: PCT-supported connections, RTS message-passing, and deposit message-passing. While the PCT-supported connections require resource allocation prior to runtime, both message-passing schemes handle communication resource allocation on-the-fly. The RTS message-passing has the lowest resource requirements and, given its token-ring-like nature, the lowest expected performance.

Because the iWarp cells use static RAM for main memory, computation performance can be accurately predicted. Figures 3.5 and 3.6 show communication times, both predicted and measured, for short and long transfers using simple point-to-point PCT-based connections, demonstrating that communication performance (at the lowest level) is both predictable and repeatable.

#### 3.2 Measured iWarp communication performance

The iWarp architecture provides three general communication schemes: PCT-based connections, RTS message-passing, and deposit message passing. This section quantitatively measures the performance of these communication schemes for varying quantities of data and varying distances. Times are measured in "clock cycles". Each iWarp component has an on-chip, program-accessible

clock/counter. While the iWarp runs at a 20MHz system clock rate, the counter runs at only one-eighth of the processor clock rate. Eight system clock ticks occur for every counter clock tick. Counter ticks are multiplied by 8 to yield the number of system clock cycles. Thus, while times are reported in "system clock ticks," the actual resolution is only to every eighth clock tick.

#### 3.2.1 PCT-based connection communication

Figures 3.5 and 3.6 show the measured times for single-word exchanges on the iWarp for distances ranging from 1 to 7 cell-widths. Times are measured by taking the round-trip exchange time (cell A sends a word to B, B receives the word then sends a word back to A, cell A receives it) and dividing by 2. Figure 3.5 shows that single-word exchanges have a repeatability well within the measurement error of the timer, and Figure 3.6 shows that runs of 8-word exchanges have a time-per-exchange that is repeatable to within a single clock.

|          | 1    | 2 cells | 3 cells | 4 cells | 5 cells | 6 cells | 7 cells |

|----------|------|---------|---------|---------|---------|---------|---------|

|          | cell |         |         |         |         |         |         |

| Avg time | 12   | 19      | 22      | 28      | 32      | . 38    | 42      |

| max time | 12   | 20      | 24      | 28      | 36      | 40      | 44      |

| min time | 12   | 16      | 20      | 28      | 32      | 36      | 40      |

Figure 3.5 - PCT-supported-connection single-word communication time (in clocks), average, maximum, and minimum times vs. distance, for 1000 single-word sequential exchange runs. Max measured error is 4 clocks.

|          | 1    | 2 cells | 3 cells | 4 cells | 5 cells | 6 cells | 7 cells |

|----------|------|---------|---------|---------|---------|---------|---------|

|          | cell |         |         |         |         |         |         |

| Avg time | 10   | 16      | 20      | 26      | 30      | 36      | 40      |

| max time | 10   | 16      | 20      | 26      | 30      | 36      | 40      |

| min time | 10   | 16      | 20      | 26      | 30      | 36      | 40      |

Figure 3.6 - PCT-supported-connection single-word communication time (in clocks), average, maximum, and minimum times vs. distance, for 1000 eight-word exchanges.

Max measured error less than 1 clock.

These measurements (particularly Figure 3.5) demonstrate that communication latencies within a real machine are neither uniform nor constant. Notice that in Figure 3.5 the communication time increments by 6 then 4 then 6 then 4 etc. This variation is due to the physical construction of the iWarp; cells are grouped four to a board. Cell-to-cell communication within a board incurs a latency of 4 clocks/cell, whereas communication between two cells on adjacent boards incurs a 6 clocks/cell latency. Furthermore, communication that "turns a corner" at a cell (such as transitions from left-to-right travel to up-to-down travel) incurs an additional 1 clock penalty. Assuming a 5 clocks/cell communication latency is a reasonable approximation that simplifies the modeling.

Connection communication cost can be modeled as having:

- (1) a fixed set-up cost for sending,

- (2) a per-word transfer cost which is a function of available network bandwidth (depends on runtime link usage, but known at link time),

- (3) a distance-dependent network-latency cost, and

- (4) a fixed set-up cost for receiving.

##

This simple model allows comparisons between predicted vs. measured communication using PCT-supported connections for multiple-word exchanges. The following tables (Figures 3.7 and 3.8) show varying predicted and measured (avg, max, and min) exchange times for payloads ranging from four bytes to 16 Kbytes over distances of one to seven cells.

Both single and multi-word exchanges can be measured. Even for exchanges as large as 16 Kbytes, communication performance on the unloaded network is both extremely repeatable and predictable (to within a microsecond). Figure 3.7 shows the results of 1000 "short bursts" of communication; Figure 3.8 shows the results of longer bursts. As can be seen, even the longer bursts maintain

predictability within half a microsecond, which is better than one percent. The iWarp connection hardware's high degree of predictability is key to obtaining fast, predictable barrier performance, which enables construction of the other TCS control modules. As will be shown shortly, while certain kinds of message passing can maintain predictability on an unloaded machine, the TCS connections will maintain predictability even on a heavily loaded machine. Certain simplifying approximations at the task level of modeling will degrade the predictability somewhat from the degree shown in Figure 3.8; still, predictability within three percent or better can be expected.

message distance (cells)

| bytes     | 1 cell | 2 cells | 3 cells | 4 cells | 5 cells | 6 cells | 7 cells |

|-----------|--------|---------|---------|---------|---------|---------|---------|

| 4         | 43     | 49      | 53      | 59      | 63      | 69      | 73      |

| (predict) | (43)   | (48)    | (53)    | (58)    | (63)    | (68)    | (73)    |

| max       | 43     | 60      | 64      | 68      | 72      | 80      | 84      |

| min       | 42     | 48      | 52      | 56      | 60      | 68      | 72      |

| 16        | 49     | 55      | 59      | 65      | 69      | 75      | 79      |

| (predict) | (49)   | (54)    | (59)    | (64)    | (69)    | (74)    | (79)    |

| max       | 60     | 64      | 68      | 76      | 80      | 88      | 88      |

| min       | 48     | 52      | 56      | 64      | 68      | 72      | 76      |

| 64        | 73     | 79      | 83      | 89      | 93      | 99      | 103     |

| (predict) | (73)   | (78)    | (83)    | (88)    | (93)    | (98)    | (103)   |

| max       | 84     | 88      | 92      | 100     | 104     | 108     | 116     |

| min       | 72     | 76      | 80      | 88      | 92      | 96      | 100     |

| 256       | 169    | 175     | 179     | 185     | 189     | 195     | 199     |

| (predict) | (169)  | (174)   | (179)   | (184)   | (189)   | (194)   | (199)   |

| max       | 180    | 188     | 188     | 196     | 196     | 204     | 208     |

| min       | 168    | 172     | 176     | 184     | 188     | 192     | 196     |

| 1024      | 553    | 559     | 563     | 569     | 573     | 579     | 583     |

| (predict) | (553)  | (558)   | (563)   | (568)   | (573)   | (578)   | (583)   |

| max       | 564    | 572     | 576     | 580     | 584     | 588     | 596     |

| min       | 552    | 556     | 560     | 568     | 572     | 576     | 580     |

| 4096      | 2089   | 2095    | 2099    | 2105    | 2109    | 2115    | 2119    |

| (predict) | (2091) | (2096)  | (2101)  | (2106)  | (2111)  | (2116)  | (2121)  |

| max       | 2100   | 2104    | 2112    | 2116    | 2120    | 2124    | 2132    |

| min       | 2088   | 2092    | 2096    | 2104    | 2108    | 2112    | 2116    |

| 16384     | 8233   | 8239    | 8243    | 8249    | 8253    | 8259    | 8263    |

| (predict) | (8241) | (8246)  | (8251)  | (8256)  | (8261)  | (8266)  | (8271)  |

| max       | 8240   | 8252    | 8252    | 8260    | 8264    | 8268    | 8272    |

| min       | 8232   | 8236    | 8240    | 8248    | 8252    | 8256    | 8260    |

Figure 3.7 PCT-supported connection communication time (in clocks), average, predicted, maximum, minimum, vs. size and distance, 1000 single-ping runs (error +/- 4 clocks/measurement)

message distance (cells)

| bytes     | 1 cell | 2 cells | 3 cells | 4 cells | 5 cells | 6 cells | 7 cells |

|-----------|--------|---------|---------|---------|---------|---------|---------|

| 4         | 42     | 48      | 52      | 58      | 62      | 68      | 72      |

| (predict) | (43)   | (48)    | (53)    | (58)    | (63)    | (68)    | (73)    |

| max       | 42     | 48      | 52      | 58      | 62      | 68      | 72      |

| min       | 42     | 48      | 52      | 58      | 62      | 68      | 72      |

| 16        | 48     | 54      | 58      | 64      | 68      | 74      | 78      |

| (predict) | (49)   | (54)    | (59)    | (64)    | (69)    | (74)    | (79)    |

| max       | 48     | 54      | 58      | 64      | 68      | 74      | 78      |

| min       | 48     | 54      | 58      | 64      | 68      | 74      | 78      |

| 64        | 72     | 78      | 82      | 88      | 92      | 98      | 102     |

| (predict) | (73)   | (78)    | (83)    | (88)    | (93)    | (98)    | (103)   |

| max       | 72     | 78      | 82      | 88      | 92      | 98      | 102     |

| min       | 72     | 78      | 82      | 88      | 92      | 98      | 102     |

| 256       | 168    | 174     | 178     | 184     | 188     | 194     | 198     |

| (predict) | (169)  | (174)   | (179)   | (184)   | (189)   | (194)   | (199)   |

| max       | 168    | 174     | 178     | 184     | 188     | 194     | 198     |

| min       | 168    | 174     | 178     | 184     | 188     | 194     | 198     |

| 1024      | 552    | 558     | 562     | 568     | 572     | 578     | 582     |

| (predict) | (553)  | (558)   | (563)   | (568)   | (573)   | (578)   | (583)   |

| max       | 552    | 558     | 562     | 568     | 572     | 578     | 582     |

| min       | 552    | 558     | 562     | 568     | 572     | 578     | 582     |

| 4096      | 2088   | 2094    | 2098    | 2104    | 2108    | 2114    | 2118    |

| (predict) | (2091) | (2096)  | (2101)  | (2106)  | (2111)  | (2116)  | (2121)  |

| max       | 2088   | 2094    | 2098    | 2104    | 2108    | 2114    | 2118    |

| min       | 2088   | 2094    | 2098    | 2104    | 2108    | 2114    | 2118    |

| 16384     | 8232   | 8238    | 8242    | 8248    | 8252    | 8258    | 8262    |

| (predict) | (8241) | (8246)  | (8251)  | (8256)  | (8261)  | (8266)  | (8271)  |

| max       | 8232   | 8238    | 8242    | 8248    | 8252    | 8258    | 8262    |

| min       | 8232   | 8238    | 8242    | 8248    | 8252    | 8258    | 8262    |

Figure 3.8 PCT-supported connection commuication time (in clocks), average, predicted, maximum, minimum, vs. size and distance, 1000 eight-ping runs, (error < 1 clock)

#### 3.2.2 RTS Message-passing communication

max

min

RTS message passing is the low-resource-overhead communication mechanism provided by the runtime system. It enables any two arbitrary cells to communicate over a token-ring-like network constructed from just two PCTs per cell. While its token-ring nature serializes all communication and hence makes it undesirable for high-bandwidth parallel communication, it is worth examining as a model for a collision-free network with serialized access. The following table (Figure 3.9) shows measured performance for messages of varying size.

| bytes | 1 cell | 2 cells | 3 cells | 4 cells | 5 cells | 6 cells | 7 cells |

|-------|--------|---------|---------|---------|---------|---------|---------|

| 32    | 27964  | 28200   | 27966   | 28200   | 27966   | 28198   | 28839   |

| max   | 28180  | 28204   | 28180   | 28204   | 28180   | 28200   | 28840   |

| min   | 27884  | 27600   | 27884   | 27600   | 27884   | 27600   | 28540   |

| 64    | 27980  | 28215   | 27982   | 28215   | 27982   | 28217   | 28855   |

| max   | 28196  | 28216   | 28196   | 28216   | 28196   | 28220   | 28856   |

| min   | 27664  | 27904   | 27904   | 27904   | 27904   | 27900   | 28844   |

| 256   | 28076  | 28311   | 28078   | 28311   | 28078   | 28313   | 28951   |

| max   | 28292  | 28312   | 28292   | 28312   | 28292   | 28316   | 28952   |

| min   | 27996  | 28016   | 28000   | 27992   | 28000   | 28000   | 28940   |

| 1024  | 28460  | 28695   | 28462   | 28695   | 28462   | 28695   | 29337   |

| max   | 28676  | 28696   | 28676   | 28696   | 28676   | 28696   | 29340   |

| min   | 28380  | 28384   | 28384   | 28384   | 28384   | 28380   | 29040   |

| 4096  | 29996  | 30231   | 29998   | 30233   | 29998   | 30231   | 30873   |

| max   | 30212  | 30232   | 30212   | 30236   | 30212   | 30232   | 30876   |

| min   | 29680  | 29920   | 29920   | 29920   | 29920   | 29916   | 30576   |

|       |        |         |         |         |         |         |         |

message distance (cells)

Figure 3.9 - measured RTS message-passing time (in clocks), average, maximum, and minimum vs. payload size and distance for 1000 single-ping runs

Given that RTS message-passing requires multiple context switches and utilizes code not accessible to the programmer, one cannot easily predict communication performance for this communication mechanism. Thus, Figure 3.9 merely reflects the measured

performance. Note that on an unloaded machine, RTS message passing also shows repeatable performance to within one-half to one-percent, but its absolute average communication time is roughly 400 times slower than PCT-supported connections for small messages (64 bytes) and 4 times slower for large messages (16 Kilobytes). As multiple cells exchange messages, the token-ring-like nature of this communication mechanism will lead to greater performance variance as cells vie for the limited ring bandwidth.

#### 3.2.3 Deposit message-passing

Deposit message-passing[22] uses a foreground-send/background-receive communication model; thus all communication incurs the cost of a program context switch on every receive. As with PCT-based connections, communication costs can be modeled rather simply. Costs include:

- a fixed set-up cost for sending;

- (2) a per-word transfer cost which is a function of available network bandwidth (depends on physical link usage at runtime);

- (3) a distance-dependent network-latency cost;

- (4) a fixed set-up cost for receiving. Depending on the communication pattern, this set-up at the receiving cell may be done in parallel with the sending cell's set-up, and the cost may be "hidden" in the overlap. Patterns which require simultaneous sending and receiving cannot hide the receive cost.

Putting these together, the message passing transfer time is modeled as follows:

Mp\_xfer\_time = (Send\_overhead + Recv\_overhead) +

(Msg\_Size/Network\_BW) + (Dist x cost\_per\_cell\_hop)

While this looks similar to the formula expressed in Section 3.2.1, the difference is that the Network\_BW is <u>not</u> known at link time, and in fact is resolved on-the-fly at runtime. One group of messages may block another, temporarily reducing available bandwidth to zero. The tables shown in Figures 3.10 and 3.11 list the transfer times predicted by the above equation, as well as the measured average, maximum, and minimum times for 1000 individual